SerDes基础知识总结

在开始了解高速接口的时候,必然会涉及到SerDes,本篇博客主要是在阅读大量文献之后形成的转述和总结。serdes的知识点实际上非常多,并且很多文章论述的侧重点不一样,有的测重整体,有的着眼细节,我则综合提取,以帮助跟我一样的初学者能够初步建立对SerDes清晰的认识。

1. 简介

SerDes是Serializer/Deserializer的缩写,即串行器和解串器,顾名思义是一种将并行数据转换成串行数据发送,将接收的串行数据转换成并行数据的”器件“。对于FPGA工程师来说“串并转换”再熟悉过不过了,只不过SerDes是一种需要数模硬件实现的,用于高速传输的“高级”串并转换器件。至于接口从最初从串口到并口,再回归到串口的历史发展,可以阅读相关的文献,借此可以了解一下系统同步、源同步的技术瓶颈。目前,商用基于SerDes架构的通信协议最高可实现单通道56Gbps(好像已经可达112Gbps)的速率,在未来高带宽、低成本的应用领域会越来越广泛。

SerDes主要具有以下优点:

- 减少布线冲突(串行,并且无单独的时钟线,时钟嵌入在数据流中,从而也解决了限制数据传输速率的信号时钟偏移问题);

- 抗噪声、抗干扰能力强(差分传输);

- 降低开关噪声;

- 扩展能力强;

- 更低的功耗和封装成本;

题外话:看了文献之后,才知道PCIE、JESD204B都是基于SerDes的协议,用OSI网络分层模型来类比的话,SerDes更接近于物理层,并强调了电气属性,而PCIE和JESD204B相当于涵盖数据链路层、网络层和传输层,所以SerDes通常又被称之为物理层(PHY)器件。实际上和很多人没分清RS232和URAT之间的关系一样。

2. 整体架构

SerDes有四种架构:1)并行时钟SerDes;2)嵌入式时钟SerDes;3)8b/10b编码SerDes;4)位交错SerDes。(注:至于这4种所谓的架构有什么区别,实现有什么特点,我还没找到专门的文献来说明)。

常见的SerDes架构是一种基于8b/10b编码并且时钟嵌入进数据流中的架构(是不是就是上面2、3的组合?),主要由物理介质相关子层( PMD)、物理媒介附加子层(PMA)和物理编码子层( PCS )所组成。如下图所示:

底色为浅绿色的子模块为PCS层,负责数据流的编码/解码,是标准的可综合CMOS数字逻辑,可以硬逻辑实现,也可以使用FPGA软逻辑实现。

底色为浅褐色子模块是PMA层,是数模混合CML/CMOS电路,负责负责串化/解串化,是理解SerDes区别于并行接口的关键。

PMD是负责串行信号传输的电气块(未画出)。

PLL模块(PLL Block)负责产生SerDes各个模块所需要的时钟信号,并管理这些时钟之间的相位关系。

一个SerDes通常还要具调试能力,例如伪随机码流产生和比对,各种环回测试,控制状态寄存器以及访问接口,LOS检测,眼图测试等,所以还需要相应的功能测试模块。

整个流程可以简述为:

- 发送(TX)

FPGA软逻辑(fabric)送过来的并行信号,通过接口FIFO(Interface FIFO),送给8b/10b编码器(8b/10b encoder)或扰码器(scambler),以避免数据含有过长连“0”或者连“1”,之后送给串行器(Serializer)进行并->串转换。串行数据经过均衡器(equalizer)调理,由驱动器(driver)发送出去。

- 接收(RX)

外部串行信号由线性均衡器(Linear Equalizer)或DFE (Decision Feedback Equalizer,判决反馈均衡)结构均衡器调理,去除一部分确定性抖动(Deterministic jitter)。CDR从数据中恢复出采样时钟,经解串器变为对齐的并行信号。8b/10b解码器(8b/10b decoder)或解扰器(de-scambler)完成解码或者解扰。如果是异步时钟系统(plesio-synchronous system),在用户FIFO之前还应该有弹性FIFO来补偿频差。

注:我发现系统性的把SerDes细节讲清楚的文献并不多,并且有些SerDes接口芯片并不完全是上面这种架构,在实际过程中,各个厂家可能会根据性能做不同的算法优化,具体的模块可能用到不同的技术,所以不要片面的理解上述架构是Serdes的唯一架构。

3. 发送端模块说明

3.1 8b/10b编码器

8b/10b编码是由IBM于1983年发明的,旨在解决系统互联以及GB以太网传输的问题。 是指将8b的数据通过某种编码规则扩展成10b,保证数据流中的“0”和“1”数量基本一致,通过降低效率来增加传输的数据恢复的可靠性。8b/10b 主要具有以下优点:

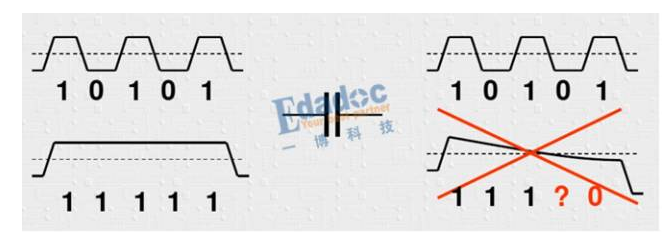

- 保证直流(DC)平衡(重点)

直流平衡是什么意思呢?如上图所示,由于我们的串行链路中会有交流耦合电容,信号频率越高,阻抗越低,反之频率越低,阻抗越高。因此上面的情况,当码型是高频的时候,基本上可以不损耗的传输过去,但是当码型为连续“0”或者“1”的情况时,电容的损耗就很大,导致幅度不断降低,带来的严重后果是无法识别到底是“1”还是“0”。因此编码就是为了尽量把低频的码型优化成较高频的码型,从而保证低损耗的传输过去。

8b/10b编码方式总输出位数是10个位,其中“0”与“1”出现的次数总共也仅在三种场合存在,分别为“5个位0与5个位1”、“4个位0与6个位1”、“6个位0与4个位1”。有一个8b/10b编码的技术专用语“不均等性(Disparity)”,其涵义就是指10个位中位0与位1出现次数的差。换句话说,8b/10b编码的“Disparity”就仅有“+2”(4个位0与6个位1)、“+0”(5个位0与5个位1)以及“-2”(6个位0与4个位1)三种状况。

- 有利于提取时钟

时钟恢复是依赖于“电平跳变沿“(后面会介绍),所以平衡”0“和”1“,可以简化了时钟恢复,降低了接收机成本。

- 方便错误检查

8B/10B编码采用冗余方式,将8位的数据和一些特殊字符按照特定的规则编码成10位的数据,根据这些规则,能检测出传输过程中单个和多个比特误码。

有关8b/10b编码的编码算法可以进一步查阅相关文献。在SerDes中长常用编码方式除了8b/10b编码外,还有64b/66b编码等;

3.2 扰码

扰码是一种将数据重新排列或者进行编码以使其随机化的方法,但是必须能够解扰恢复。我们希望打乱长的连“0”和长的连“1”序列,将数据随机化。扰码产生是通过循环移位寄存器来实现的,而扰码生成多项式决定循环移位寄存器的结构。那么对信号加干扰有什么好处?

- 解决EMI问题

当数据重复传输时,能量就会集中在某一频率上,产生EMI噪声;数据经过加扰后,能把集中的能量分散开,几乎变成白噪声。

-

有利于提取时钟

-

同时又扩展了基带信号频谱,起到加密的效果

总结到这里,看网友有提问,也提醒了我。问题是:在SerDes中先进行8b/10b编码之后再进行扰码,感觉两个的作用类似,只是扰码进一步增加“0”和“1”的随机性,还有没有其他更重要的作用?先加扰再编码有没有问题?初学者总有很多疑问。

3.3 串行器/解串器

串行器Serializer把并行信号转化为串行信号。Deserializer把串行信号转化为并行信号。一般地,并行信号为8 /10bit或者16/20bit宽度,串行信号为1bit宽度(也可以分阶段串行化,如8bit->4bit->2bit->equalizer->1bit以降低equalizer的工作频率)。

Serializer/Deserializer的实现采用双沿(DDR)的工作方式,利用面积换速度的策略,降低了电路中高频率电路的比例,从而降低了电路的噪声。

接收方向除了Deserializer之外,一般带有还有对齐功能逻辑(Aligner)。相对SerDes发送端,SerDes接收端起始工作的时刻是任意的,接收器正确接收的第一个 bit可能是发送数据的任意bit位置。因此需要对齐逻辑来判断从什么bit位置开始(哪里开始算是第一个数据),以组成正确的并行数据。对齐逻辑通过在串行数据流中搜索特征码字(Alignment Code)来决定串并转换的起始位置,这就需要用到了8b/10b的控制字符集,也就是我们常说的“K”字符,常见的什么K28.5、K28.0、K28.3、K28.4等,在JESD204B中他们又称/K/、/R/、/A/、/Q/字符。

3.4 前向反馈均衡(feed-forward equalization/equalizer)

SerDes信号从发送芯片到达接收芯片所经过的路径称为信道(channel),包括芯片封装、pcb走线、过孔、电缆、连接器等元件。从频域看,信道可以简化为一个低通滤波器(LPF)模型,如果SerDes的速率大于信道的截止频率,就会一定程度上损伤信号(高频被滤掉了,数字信号边沿会变得平滑)。均衡器的作用就是补偿信道对信号的损伤。

发送端的均衡器采用FFE(Feed forward equalizers)结构,从频域上看,FFE是一个高通滤波器(容易理解,信道损伤是一个低通滤波器,会抑制高频,那么均衡就补偿高频)。从时域上看,又叫加重器(emphasis)。加重分为去加重(de-emphasis)和预加重(pre-emphasis)。De-emphasis 降低差分信号的摆幅(swing)。Pre-emphasis增加差分信号的摆幅。由于目前芯片都需要追求降低功耗,所以大部分使用de-emphasis的方式,加重越强,信号的平均幅度会越小。

4. 接收端模块说明

4.2 接收均衡器

4.2.1 线形均衡器(Linear Equalizer)

接收端均衡器的目标和发送均衡器是一致的。对于低速(<5Gbps)SerDes,通常采用连续时间域、线性均衡器实现如尖峰放大器(peaking amplifier), 均衡器对高频分量的增益大于对低频分量的增益。

4.2.2 裁决反馈均衡器(Decision Feedback Equalizer-DFE)

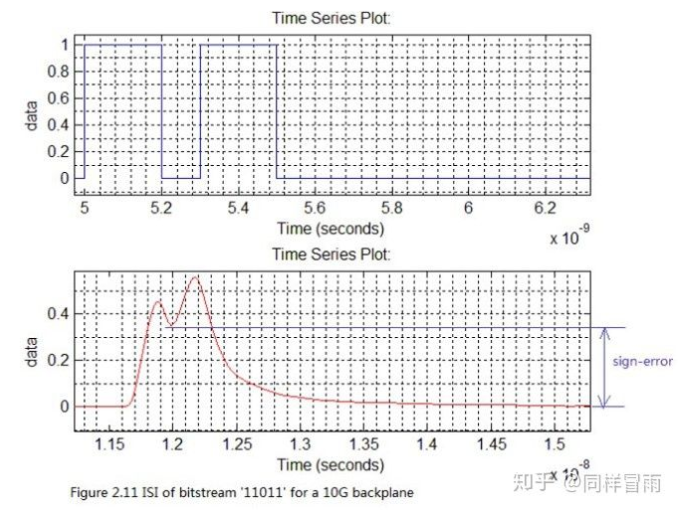

对于高速(>5Gbps)SerDes,由于信号的抖动(如ISI相关的确定性抖动)可能会超过或接近一个符号间隔(UI,Unit Interval),单单使用线性均衡器不再适用。线性均衡器对噪声和信号一起放大,并没有改善SNR或者说BER。对于高速SerDes,采用一种称作DFE的非线性均衡器。DFE通过跟踪过去多个UI的数据(history bits)来预测当前bit的采样门限,从而预测码间干扰。DFE只对信号放大,不对噪声放大,可以有效改善SNR。

不论是发送端还是接收端的均衡器,本质上都是高通滤波器,因为数字信号采样都希望边沿越抖越好,边沿变缓之后就会产生码间干扰。

如下图所示,系统传输一个“11011”的码流,如果没有均衡器,信号受到信道损伤,信号展宽,出现码间干扰,导致中间的“0”,无法被检测到。

DFE设计的关键是确定DFE系数,如果DFE的系数接近信道的脉冲相应,就可以到的比较理想的结果。但是信道是一个时变的媒介,比如温度电压工艺的慢变化等因素会改变信道的特性。因此DFE的系数需要自适应算法,自动扑获和跟随信道的变化。这也是实际应用中DFE功能开启的时候,做环境试验的结果很多时候会出问题,因为DFE在信道特性变化的时候,自适应的速度没有跟上。DFE系数自适应算法非常学术,每个厂商的算法都是保密的,不对外公布。

4.3 时钟数据恢复(CDR)

最开始接触SerDes的是,说“没有单独的时钟线,时钟嵌入在数据流中的”,脑海里第一反应就是在数据中插入一定规则的编码代表时钟的高电平或者低电平,回头一想,那时钟频率不就远低于数据的采集频率了吗?实际上,所谓的“时钟嵌在数据中”的意思,是时钟嵌在数据的跳变沿里。不难理解,极端情况下,假设一串数据流是"1"和"0"交替发送,那这不就是一个时钟了吗。

CDR( Clock and Data Recovery)即时钟和数据的恢复,是SerDes设计中非常重要的环节。CDR常用的技术有基于数字锁相环(PLL)和基于相位插值器两种。当数据经过时,CDR就会捕获数据边沿跳变的频率,如果数据长时间没有跳变,CDR就无法得到精确的训练,CDR采样时刻就会漂移,可能采到比真实数据更多的“0”或“1”。这就是为什么我们在发送的时候采用8b/10b编码或扰码来避免重复出现“0”或“1”,原因之一也在此。所以CDR有一个指标叫做最长连“0”或连“1”长度容忍(Max Run Length或者Consecutive Identical Digits)能力。

恢复了时钟之后,需要恢复数据。第一步首先要将恢复出来的时钟与数据的边缘进行对齐,然后再将数据给读出来。在硬件原理上,使用PLL电路以及触发器即可。

以上是总结的有关SerDes的基础知识,希望能帮助像我一样的初学者建立初步的认识。SerDes每一个模式深入下去都有很多硬件、信号完整性(包括眼图的评价机制)的知识,想做到非常清晰的认识有一定的难度。目前,对于FPGA工程师来说,SerDes作为phy芯片或者集成在IP核中,先掌握应用,需要的时候再深入。

浙公网安备 33010602011771号

浙公网安备 33010602011771号