Day04_vhdl代码_计算机网络

VHDL

3bit计数器分别用out和buffer输出类型的实现

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity counter3 is

port

(

clk,reset: in bit;

-- count: out integer range 0 to 7

count_buffer: buffer integer range 0 to 7

);

end entity counter3;

architecture my_arch of counter3 is

-- signal count_tmp:integer range 0 to 7;

begin

process

begin

wait until (clk'event and clk='1');

-- if (reset='1') or (count_tmp=7) then

-- count_tmp<=0;

-- else count_tmp<=count_tmp+1;

if (reset='1') or (count_buffer=7) then

count_buffer<=0;

else count_buffer<=count_buffer+1;

end if;

end process;

-- count<=count_tmp;

end architecture my_arch;

*功能与资源对比*

| 对比项 | Out类型实现 | Buffer类型实现 |

|---|---|---|

| 代码复杂度 | 需要额外中间信号,代码冗余 | 无需中间信号,代码简洁 |

| *可读性 | 需理解中间信号的作用 | 直接通过端口操作,逻辑清晰 |

| 综合结果 | 可能多一个寄存器(中间信号) | 综合结果更直接,资源占用可能更少 |

| 工具兼容性 | 兼容所有工具(广泛支持out类型) | 部分旧工具可能不支持buffer类型 |

| 设计意图 | 输出端口仅用于输出 | 明确表示端口需要内部反馈 |

二进制回文数检测

逻辑函数:二进制回文数检测器

· *功能描述*:检测4位二进制输入是否为回文数(正读反读相同),输出高电平表示符合条件。

· *输入*:4位二进制数 ABCD(A为最高位,D为最低位)

· *输出*:1位信号 Y

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity detector is

port(

A,B,C,D: in std_logic;

Y : out std_logic

);

end entity detector;

--第一种实现方式:逻辑表达式:Y=(A同或D)并且(B同或C)

architecture behavior1 of detector is

begin

Y <= not(A xor D) and not(B xor C);

end architecture behavior1;

--第二种实现方式:真值表

architecture behavior2 of detector is

signal input_vec : std_logic_vector(3 downto 0); -- 合并输入为矢量

begin

-- 将输入A/B/C/D映射到矢量input_vec[3]/[2]/[1]/[0]

input_vec <= A & B & C & D;

-- 真值表实现

process(input_vec)

begin

case input_vec is

-- 回文数条件:A=D且B=C

when "0000" => Y <= '1'; -- 0 (A=0,D=0; B=0,C=0)

when "0110" => Y <= '1'; -- 6 (A=0,D=0; B=1,C=1)

when "1001" => Y <= '1'; -- 9 (A=1,D=1; B=0,C=0)

when "1111" => Y <= '1'; -- 15 (A=1,D=1; B=1,C=1)

when others => Y <= '0'; -- 其他情况非回文数

end case;

end process;

end architecture behavior2;

- 定义了两种不同的结构体实现该实体

- 真值表法使用ai协助生成

- 真值表虽然清晰,但逻辑函数表示更为简洁

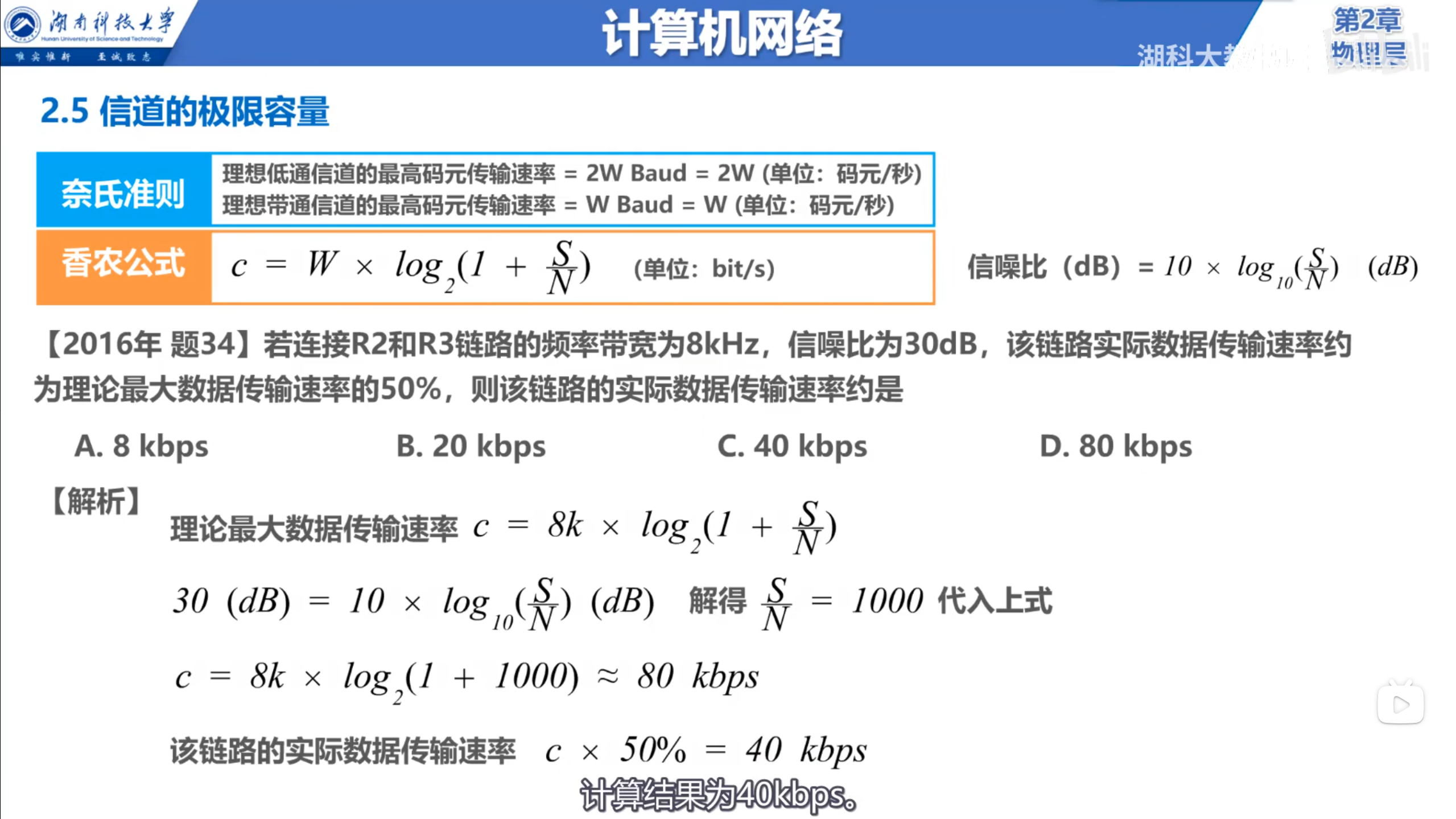

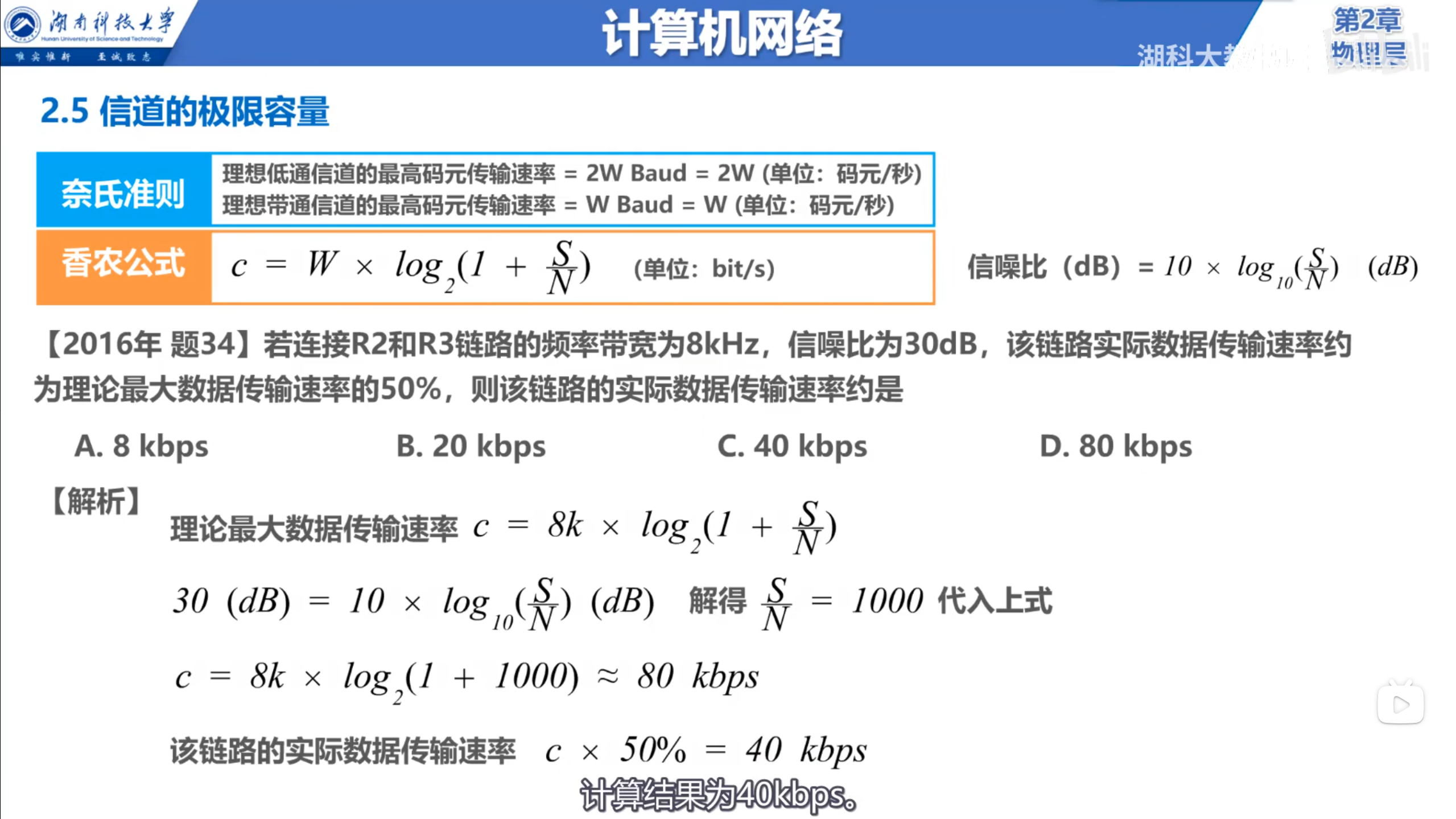

计算机网络

数据传输速率的计算方式

编码方式

百词斩打卡

浙公网安备 33010602011771号

浙公网安备 33010602011771号