1.VCS仿真基础

VCS的仿真流程:

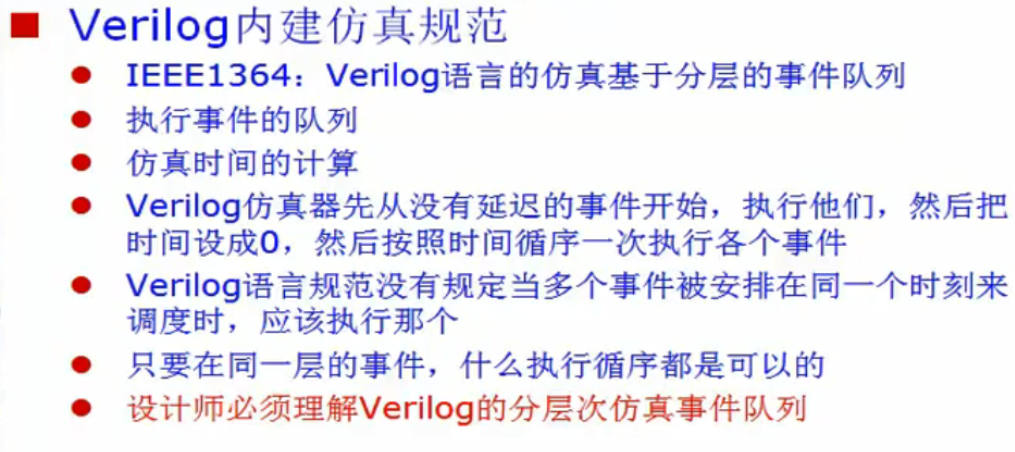

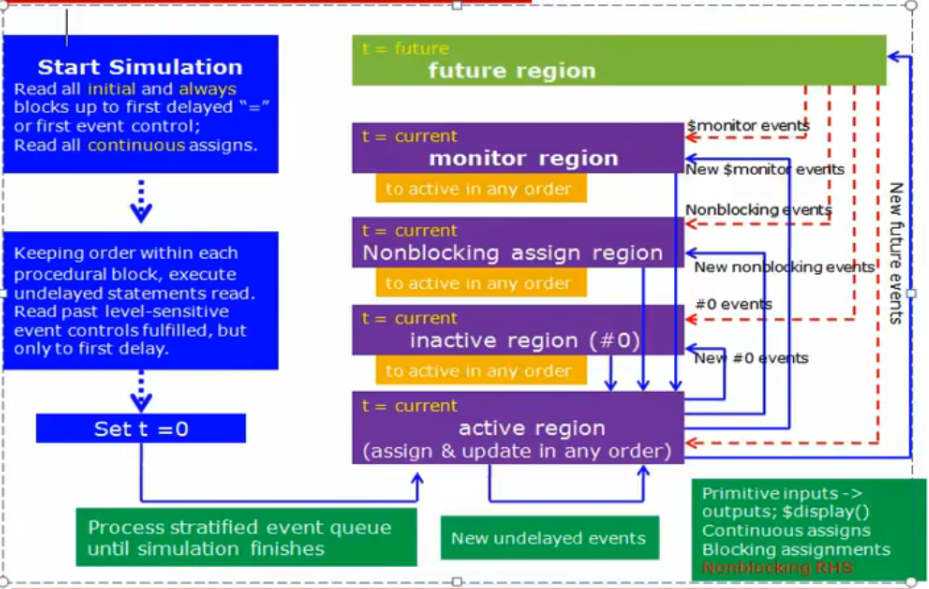

1、编译compile 和 仿真Simulate ,符合 IEEE-1364 标准。

行为及描述、RTL(寄存器传输级)、Gate-level(门级),与具体工艺库相关(TSMC,SMIC,CSMC)

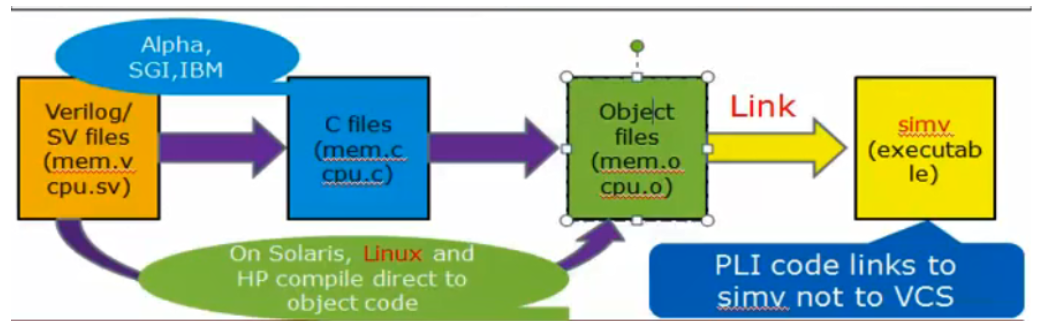

2、VCS如何进行工作的:

3、VCS编译命令格式(Linux下)

$vcs soure_file [compile_time_options]

soure_file :verilog/Systemverilog写的所有文件。

compile_time_options:控制执行的选项

然后产生二进制可执行仿真文件。

4、编译中常用的选项

(1)-Mupdate:增量编译(只编译在原工程中修改后的代码)。

(2)-R: 在编译完成后,自动执行。

(3)-gui:仿真开始后启动DVE图形界面。

(4)-I<filename>:将编译时产生的写入到filename中去。

(5)-sverilog:支持Systemverilog。

(6)+v2k:支持verilog 2001的标准。

(7)-v lib file:

(8)-y lib dir:库放的路径。

(9)+libext+lib ext:加入在这个路径下的所有库文件。

(10)+incdir+inc dir:给出 "include"的路径。

(11)-f file:文件太多时,将所有文件整合到一个文件夹下,利用刚命令执行所有文件。

(12)-o foo:将simv文件转换成foo文件。

(13)+define+<macro_name>=<value>:在程序中定义一些宏。

总结:VCS仿真执行过程

浙公网安备 33010602011771号

浙公网安备 33010602011771号