ESP32原生开发——MAX98375食用指南 1I2S总线介绍

简介

在音频处理领域,I2S是一种广泛使用的通信协议,它专门用于芯片之间的音频数据传输。ESP32 作为一款高性能的微控制器,不仅支持 I2S 通信,还提供了强大的硬件接口和灵活的软件库,使其成为音频项目开发的理想选择。本篇文章将介绍I2S的相关知识和使用ESP32驱动I2S音频设备时比较常用的相关底层API函数。

目前看起来是ESP32的飞利浦I2S总线,还有一种差分I2S总线

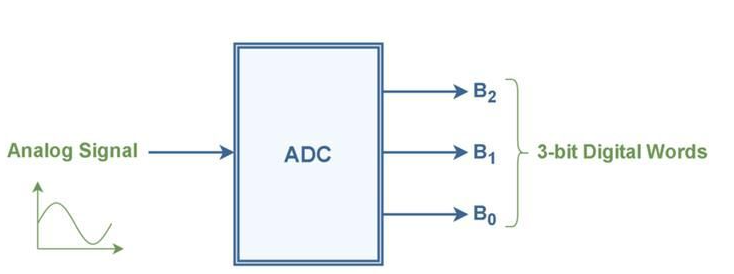

音频数据的量化位数或量化深度,常见的有8bit、16bit、24bit、32bit等,位数越高,信号的动态范围和精细程度越好

怎样使用I2S传输音频?

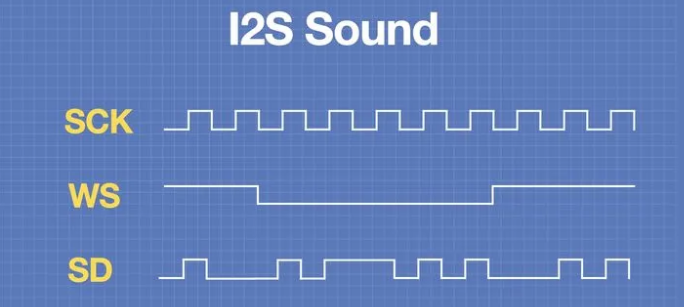

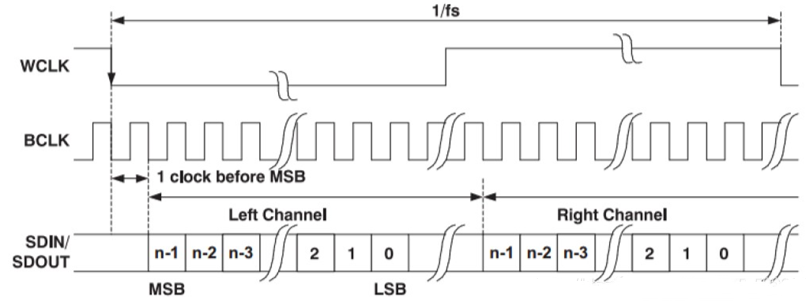

使用I2S传输音频的时候,需要用到时钟信号、控制信号以及数据信号(图6),它们之间是分开传输的。对于标准通信模式下的 I2S 总线主要包含以下几个信号:

位时钟BCLK,

BCLK(Bit Clock,位时钟)

也叫BCK, SCLK(Serial Clock),对应数字音频的每一位数据,是模块内的同步信号

字时钟WS,

也叫 LRCLK (Left Right Clock)即左右声道时钟, 用于标识当前正在传输的是左声道数据还是右声道数据。对于飞利浦公司定义的I2S标准,当 WS 为低电平时表示左声道,高电平时表示右声道。一个完整的 WS 信号周期包含两个声道的数据(左声道和右声道)

WS 信号的频率等于音频的采样率。

例如,如果音频采样率是 44.1kHz,那么 WS 的频率也是 44.1kHz。

串行数据SD。

i2s传输时的音频数据,是用二进制补码表示的,具体数据传输的格式主要包括:I2S格式,左对齐格式,右对齐格式,

每个 BCK 周期会传输一位数据。数据发送端和接收端会根据 BCK 信号的跳变(上升沿或下降沿)同步数据的发送和接收。当 WS 为低电平时,SD 传输左声道数据;当 WS 为高电平时,SD 传输右声道数据。

有的时候还需要MCLK:主时钟线,该信号线可选,具体取决于从机,主要用于向 I2S 从机提供参考时钟。

比如我们传输16 位双声道音频,SD数据为1 0 1 0 1 1 0 1 1 0 0 0 1 0 0 1 1 1 0 0 1 0 0 1 1 0 0 0 1 0 0 1

它表示

每个 BCK 周期传输一位音频数据。

当 WS 为低电平时,SD 按位传输左声道的 16 位数据1 0 1 0 1 1 0 1 1 0 0 0 1 0 0 1

当 WS 为高电平时,SD 按位传输右声道的 16 位数据 1 1 0 0 1 0 0 1 1 0 0 0 1 0 0 1,

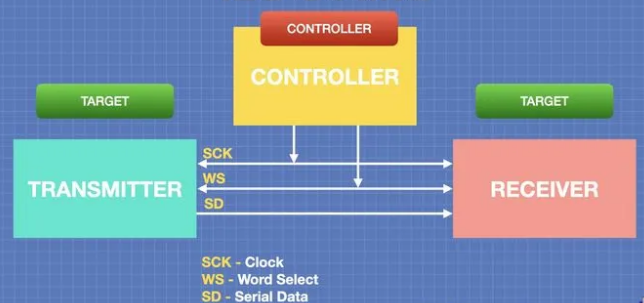

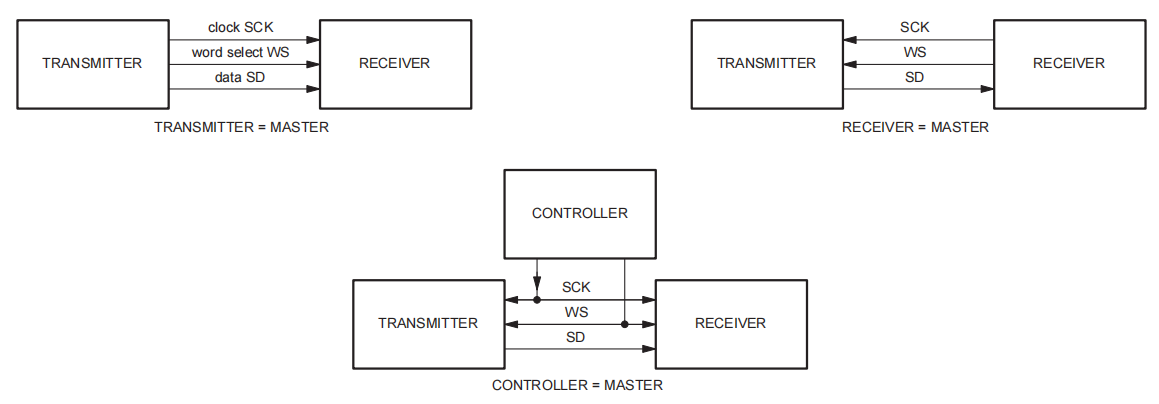

I2S传输模型

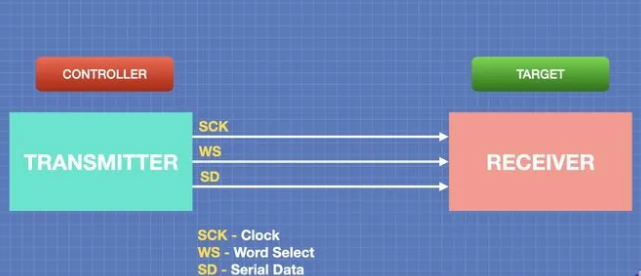

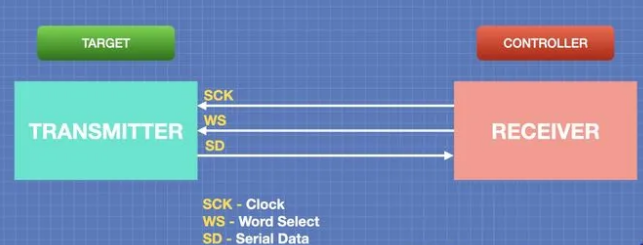

I2S通信支持全双工和半双工通信,支持主/从模式。主设备就是发送时钟的,从设备在时钟的控制下发送或者接收数据。

连接到I2S总线的设备可以分为两类:

控制器——控制 SCK 和 WS 信号。

目标设备——接收 SCK 和 WS 信号

总线上只能有一个控制器,但是总线可以有多个目标设备。

音频设备,可以分为三类:

- 发射器作为控制器, 接收器作为目标设备

- 发射器作为目标设备,接收器作为控制器

- 发射器和接收器都作为目标设备,其他I2S控制器作为控制器

三种经典I2S传输模型

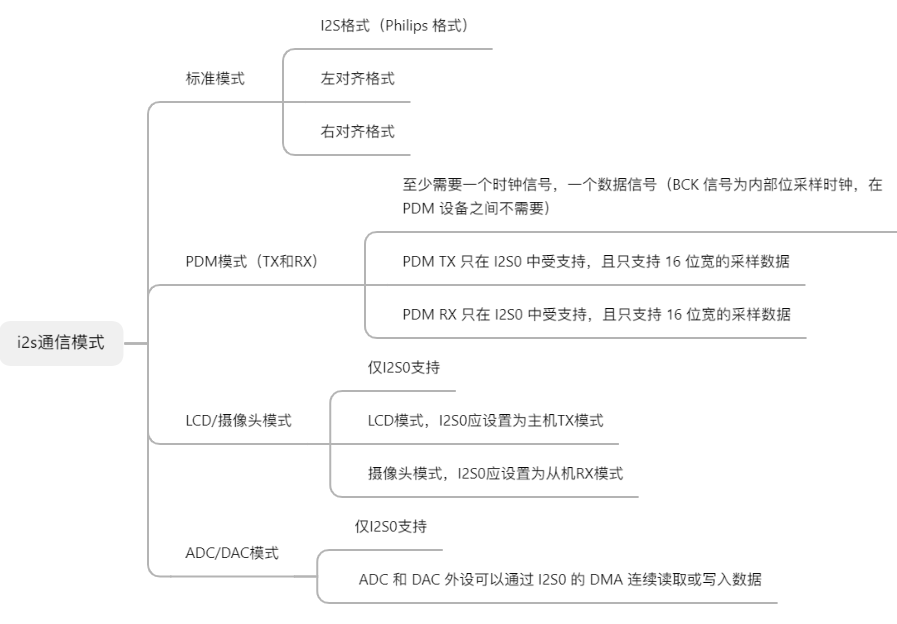

I2S通信格式

PCM510xA 支持行业标准的音频数据格式,包括标准 I2S 和 左对齐(Left-justified) 格式等。

I2S格式

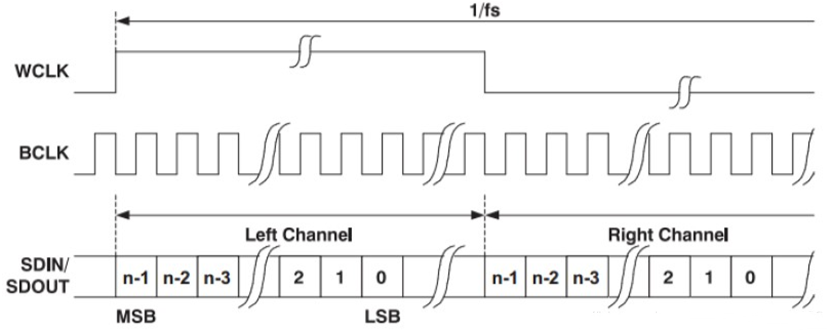

I2S格式:又称飞利浦格式(图7),数据最高位总是出现在字时钟变化后的第二个位时钟脉冲处(滞后一个位时钟),这种格式下数据MSB的位置是确定的,LSB的位置取决于字长。

左对齐格式

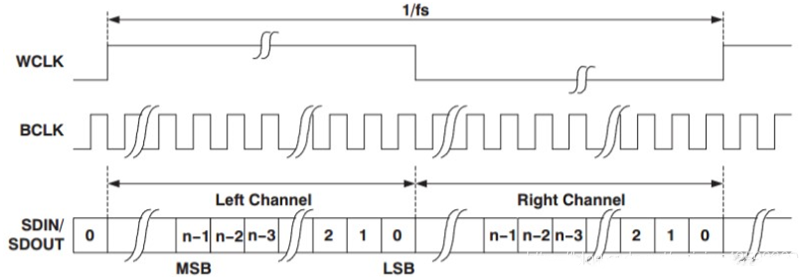

左对齐格式(图8):数据最高位出现在字时钟变化后的第一个位时钟脉冲处(无滞后位时钟)

右对齐格式

右对齐格式:又称日本格式,这种格式和左对齐差不多,只不过整体是靠右对齐的,即数据LSB与WCLK跳变沿对齐。

i2s基本配置

①,i2s的时钟使能和GPIO口配置 ②,配置为i2s模式

③,i2s标准,无论有多少位有效数据,即数据的最高位总是出现在WS变化(也就是一帧开始)后的第2个CK脉冲处。

④,i2s数据长度,包括16位,16位扩展(16位数据以32位包发送),24位,32位。 ⑤,设置i2s时钟

⑥,设置i2s空闲状态下时钟电平 ⑦,i2s使能

浙公网安备 33010602011771号

浙公网安备 33010602011771号