基于FPGA的一维序列三次样条插值算法verilog实现,包含testbench

1.前言

三次样条插值是一种在数据拟合和信号处理中广泛应用的技术,它通过构造分段三次多项式来逼近给定的离散数据点,确保整个插值函数在节点处具有连续的一阶和二阶导数,从而获得平滑的插值结果。在 FPGA 实现中,由于其并行计算和硬件加速的特性,能够高效处理实时性要求高的插值任务。

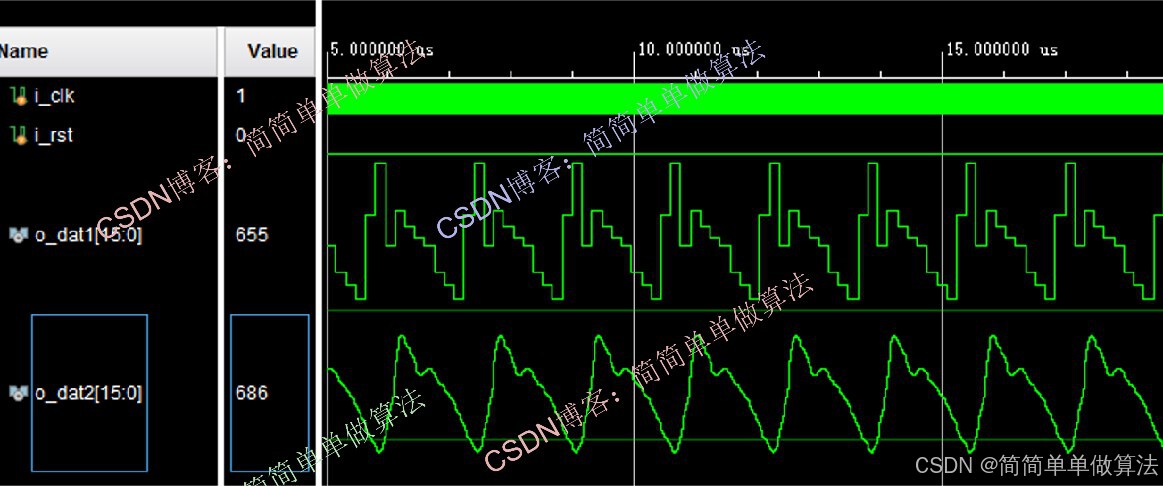

2.算法运行效果图预览

3.算法运行软件版本

vivado2019.2

4.部分核心程序

(完整版代码包含中文注释和操作步骤视频)

//p1 = M4(i,1) *(X(i+1)-x(t))^3/(6*h4(i)); wire signed[31:0]tmp1_1,tmp1_2,tmp1_3,tmp1_4; mult1 mult1_u1(.A(M4_ia), .B(16'd16+X_ia - xta), .P(tmp1_1)); mult1 mult1_u2(.A(16'd16+X_ia - xta), .B(16'd16+X_ia - xta), .P(tmp1_2)); mult1 mult1_u3(.A(tmp1_1[17:2]), .B(tmp1_2[17:2]), .P(tmp1_3)); mult1 mult1_u4(.A(6), .B(h4a), .P(tmp1_4)); reg signed[31:0]p1s; 35_008m

5.算法仿真参数

16;//插值倍数

6.算法理论概述

1. 三次样条函数的表达式 对于每个子区间 [xᵢ,xᵢ₊₁],三次样条函数可表示为: Sᵢ(x) = aᵢ + bᵢ(x-xᵢ) + cᵢ(x-xᵢ)² + dᵢ(x-xᵢ)³ 其中,aᵢ、bᵢ、cᵢ、dᵢ为待定系数,需要根据插值条件和连续性条件确定。 2. 插值条件约束 由插值条件 Sᵢ(xᵢ)=yᵢ,可得: aᵢ = yᵢ 由 Sᵢ(xᵢ₊₁)=yᵢ₊₁,代入 x=xᵢ₊₁得: yᵢ₊₁ = aᵢ + bᵢhᵢ + cᵢhᵢ² + dᵢhᵢ³ 其中 hᵢ = xᵢ₊₁ - xᵢ,为区间长度。 3. 一阶导数连续性条件 计算一阶导数: Sᵢ’(x) = bᵢ + 2cᵢ(x-xᵢ) + 3dᵢ(x-xᵢ)² 在节点 xᵢ₊₁处,左导数 Sᵢ’(xᵢ₊₁) 应等于右导数 Sᵢ₊₁’(xᵢ₊₁),即: bᵢ + 2cᵢhᵢ + 3dᵢhᵢ² = bᵢ₊₁ 4. 二阶导数连续性条件 计算二阶导数: Sᵢ''(x) = 2cᵢ + 6dᵢ(x-xᵢ) 在节点 xᵢ₊₁处,左二阶导数 Sᵢ''(xᵢ₊₁) 应等于右二阶导数 Sᵢ₊₁''(xᵢ₊₁),即: 2cᵢ + 6dᵢhᵢ = 2cᵢ₊₁ 化简得: cᵢ + 3dᵢhᵢ = cᵢ₊₁ 5. 引入二阶导数变量 令 Mᵢ = S''(xᵢ),即节点 xᵢ处的二阶导数值,则在区间 [xᵢ,xᵢ₊₁] 内: Sᵢ''(x) = Mᵢ + 6dᵢ(x-xᵢ) 当 x=xᵢ时,Sᵢ''(xᵢ)=Mᵢ,故 2cᵢ = Mᵢ,即 cᵢ = Mᵢ/2 当 x=xᵢ₊₁时,Sᵢ''(xᵢ₊₁)=Mᵢ₊₁,故 2cᵢ + 6dᵢhᵢ = Mᵢ₊₁,代入 cᵢ得: Mᵢ + 6dᵢhᵢ = Mᵢ₊₁ 解得:dᵢ = (Mᵢ₊₁ - Mᵢ)/(6hᵢ) 6. 推导一阶导数系数 由 Sᵢ(xᵢ₊₁)=yᵢ₊₁,代入 aᵢ=yᵢ,cᵢ=Mᵢ/2,dᵢ=(Mᵢ₊₁ - Mᵢ)/(6hᵢ) 得: yᵢ₊₁ = yᵢ + bᵢhᵢ + (Mᵢ/2) hᵢ² + [(Mᵢ₊₁ - Mᵢ)/(6hᵢ)] hᵢ³ 化简得: bᵢ = (yᵢ₊₁ - yᵢ)/hᵢ - (Mᵢhᵢ)/2 - (Mᵢ₊₁ - Mᵢ) hᵢ/6 7. 构造线性方程组 由一阶导数连续性条件 bᵢ + 2cᵢhᵢ + 3dᵢhᵢ² = bᵢ₊₁,代入 bᵢ、cᵢ、dᵢ表达式: [(yᵢ₊₁ - yᵢ)/hᵢ - (Mᵢhᵢ)/2 - (Mᵢ₊₁ - Mᵢ)hᵢ/6] + 2*(Mᵢ/2)hᵢ + 3[(Mᵢ₊₁ - Mᵢ)/(6hᵢ)]*hᵢ² = (yᵢ₊₂ - yᵢ₊₁)/hᵢ₊₁ - (Mᵢ₊₁hᵢ₊₁)/2 - (Mᵢ₊₂ - Mᵢ₊₁)hᵢ₊₁/6 化简后得到: hᵢMᵢ + 2 (hᵢ + hᵢ₊₁) Mᵢ₊₁ + hᵢ₊₁Mᵢ₊₂ = 6 [(yᵢ₊₂ - yᵢ₊₁)/hᵢ₊₁ - (yᵢ₊₁ - yᵢ)/hᵢ] 这是一个关于 Mᵢ的三对角线性方程组,需要结合边界条件求解。

浙公网安备 33010602011771号

浙公网安备 33010602011771号