https://en.wikipedia.org/wiki/MESI_protocol

Modified (M): cache line 唯一且dirty(和memory不同,且有责任更新memory)

Eclusive(E): cache line 唯一且 和memory 相同

Share(S): cache line可能不唯一可能不唯一,且clean(不负责向memory写),和memory相同

Invalid(I): cache中无此cache line

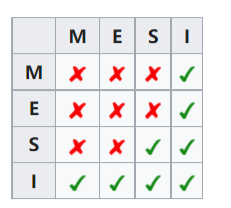

任意两个cache中对应的cache line可能的状态:

![]()

Processor Requests to Cache include the following operations:

- PrRd: The processor requests to read a Cache block.

- PrWr: The processor requests to write a Cache block

Bus side requests are the following:

- BusRd: Snooped request that indicates there is a read request to a Cache block requested by another processor

- BusRdX: Snooped request that indicates there is a write request to a Cache block requested by another processor that doesn't already have the block.

- BusUpgr: Snooped request that indicates that there is a write request to a Cache block requested by another processor but that processor already has that Cache block residing in its own Cache.

- Flush: Snooped request that indicates that an entire cache block is written back to the main memory by another processor.

- FlushOpt: Snooped request that indicates that an entire cache block is posted on the bus in order to supply it to another processor(Cache to Cache transfers).

cpu写cache之前要先获得相应cache line的数据并使所有其他cache相应的cache line invalid。

如果本cache中没有相应cache line,要先获得cache line的数据。因此发送BusRdX,获取数据并使其他cache line invalid,这是为了写进行的读操作

如果本cache中有相应的cache line, 不用获取数据,但要使其他cache line invalid, 因此发送BusUpgr使其他cache line invalid.

cache line遇到本cpu的读写和总线上的transaction时的操作如下:

Table 1.1 State Transitions and response to various Processor Operations

|

| Invalid(I) |

PrRd |

- Issue BusRd to the bus

- other Caches see BusRd and check if they have a valid copy, inform sending cache

- State transition to (S)Shared, if other Caches have valid copy.

- State transition to (E)Exclusive, if none (must ensure all others have reported).

- If other Caches have copy, one of them sends value, else fetch from Main Memory

|

| |

PrWr |

- Issue BusRdX signal on the bus

- State transition to (M)Modified in the requestor Cache.

- If other Caches have copy, they send value, otherwise fetch from Main Memory

- If other Caches have copy, they see BusRdX signal and Invalidate their copies.

- Write into Cache block modifies the value.

|

| Exclusive(E) |

PrRd |

- No bus transactions generated

- State remains the same.

- Read to the block is a Cache Hit

|

| |

PrWr |

- No bus transaction generated

- State transition from Exclusive to (M)Modified

- Write to the block is a Cache Hit

|

| Shared(S) |

PrRd |

- No bus transactions generated

- State remains the same.

- Read to the block is a Cache Hit.

|

| |

PrWr |

- Issues BusUpgr signal on the bus.

- State transition to (M)Modified.

- other Caches see BusUpgr and mark their copies of the block as (I)Invalid.

|

| Modified(M) |

PrRd |

- No bus transactions generated

- State remains the same.

- Read to the block is a Cache hit

|

| |

PrWr |

- No bus transactions generated

- State remains the same.

- Write to the block is a Cache hit.

|

Table 1.2 State Transitions and response to various Bus Operations

|

| Exclusive(E) |

BusRd |

- Transition to Shared (Since it implies a read taking place in other cache).

- Put FlushOpt on bus together with contents of block.

|

| |

BusRdX |

- Transition to Invalid.

- Put FlushOpt on Bus, together with the data from now-invalidated block.

|

| |

BusUpgr |

- Transition to Invalid (cache that sent BusUpgr becomes Modified)

- May put FlushOpt on bus together with contents of block (design choice, which cache with Shared state does this)

|

| Modified(M) |

BusRd |

- Transition to (S)Shared.

- Put FlushOpt on Bus with data. Received by sender of BusRd and Memory Controller, which writes to Main memory.

|

| |

BusRdX |

- Transition to (I)Invalid.

- Put FlushOpt on Bus with data. Received by sender of BusRdx and Memory Controller, which writes to Main memory.

|

| Invalid(I) |

BusRd |

- No State change. Signal Ignored.

|

| |

BusRdX/BusUpgr |

- No State change. Signal Ignored

|

| Shared(S) |

BusRd |

- No State change (other cache performed read on this block, so still shared).

- May put FlushOpt on bus together with contents of block (design choice, which cache with Shared state does this).

|

什么时候会flush?

cache line 为M,本cpu要写或其他cpu要读(BusRdX)时。

浙公网安备 33010602011771号

浙公网安备 33010602011771号