systemverilog中的一个问题

#0延迟为什么不起作用?

这与SV中事件调度有关

https://blog.csdn.net/lionsde/article/details/106928252

虽然设计的代码在仿真器中理论上来说是可以并行执行的,但是在实际仿真中,代码都是运行在CPU上的一些程序而已。SV为代码的执行顺序定义了调度机制,最大限度的减少不确定性的产生。

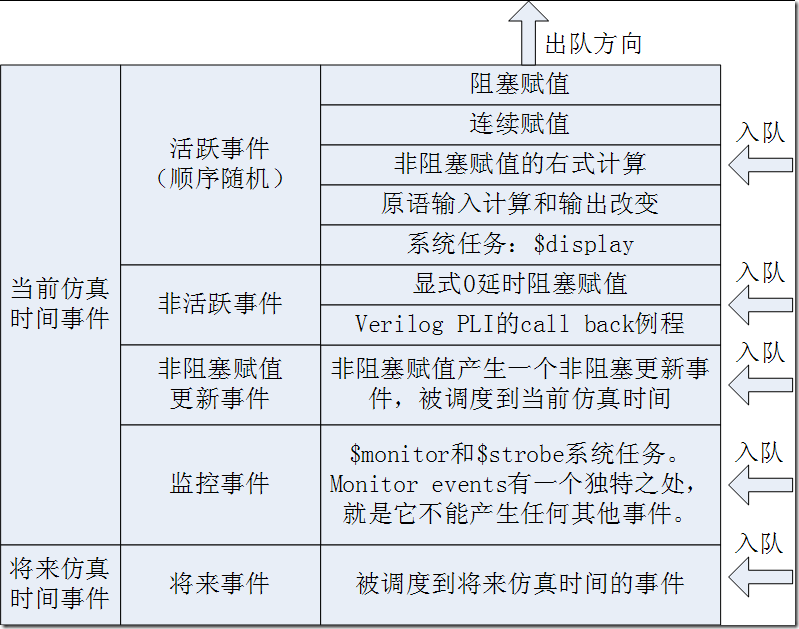

SV被定义为一种基于离散事件执行模型的语言。换句话说,仿真是离散的,是基于时间片进行且只对特定的时刻点进行仿真的。

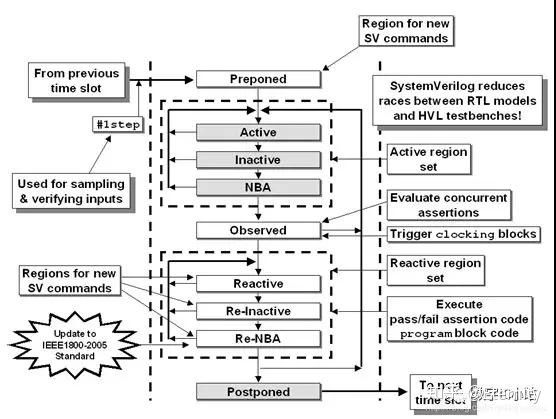

这里说的时间片其实没有时间概念,纯粹是工具为了仿真效果而提出的不同任务工作的区域,在一个时钟边沿有效,可以理解为一个时钟边沿上的进程,但不涉及时间的推进,只是进程顺序执行。只有在当前时间片上的所有仿真全部完成,仿真器才会进入下一个时间片。当然,每个时间片还会细分为多个区域,如下图所示:

module top; int a; initial begin a<=1; #0; $display("a=%d",a); end endmodule

module top; int a; initial begin a<=1; end initial begin #0 a<2; end initial begin $display("a=%d",a); end endmodule

后者#0 在非阻塞赋值之后执行。在同一个begin end 块中还是顺序执行。

如果连续调用两个task

浙公网安备 33010602011771号

浙公网安备 33010602011771号