SPI通信

1、SPI通信

-

SPI与I2C的优缺点:

-

SPI速度更快

-

设计简单粗暴,实现的功能没有I2C的多

-

SPI的硬件开销比较大,通信线的个数比较多,会有资源浪费的现象

-

-

SPI(Serial Peripheral Interface)是由Motorola公司开发的一种通用数据总线

-

四根通信线:SCK(Serial Clock)串行时钟线、MOSI(Master Output Slave Input)主机输出 从机输入、MISO(Master Input Slave Output)主机输入 从机输出、SS(Slave Select)从机选择-->低电平有效

-

同步、全双工

-

支持总线挂载多设备(一主多从)

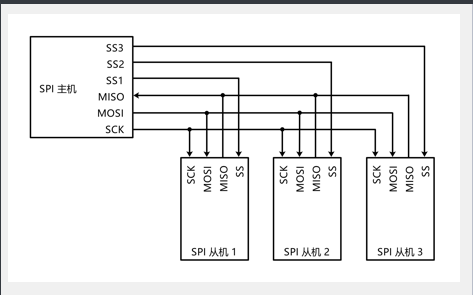

2、硬件电路

-

所有SPI设备的SCK、MOSI、MISO分别连在一起

-

主机另外引出多条SS控制线,分别接到各从机的SS引脚(需要通讯的置于低电平)

-

输出引脚配置位推挽输出,输入引脚配置位浮空或上拉输入

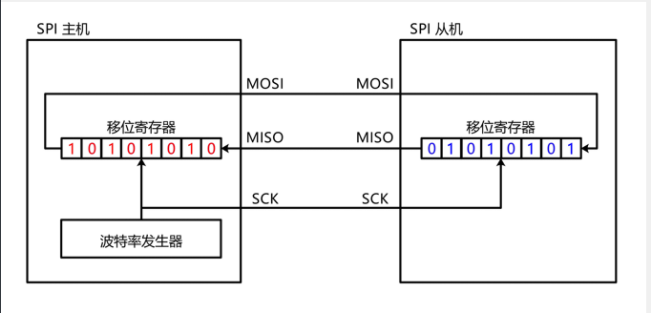

3、移位示意图

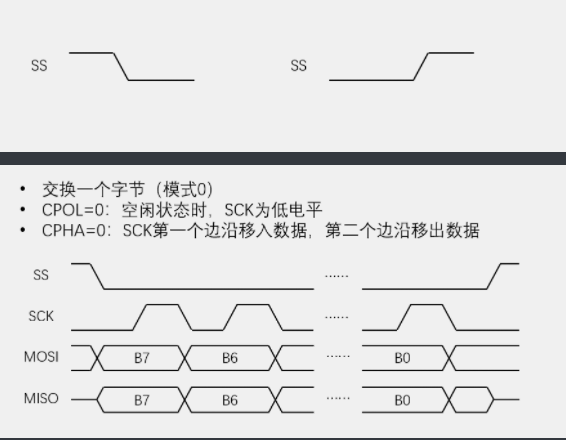

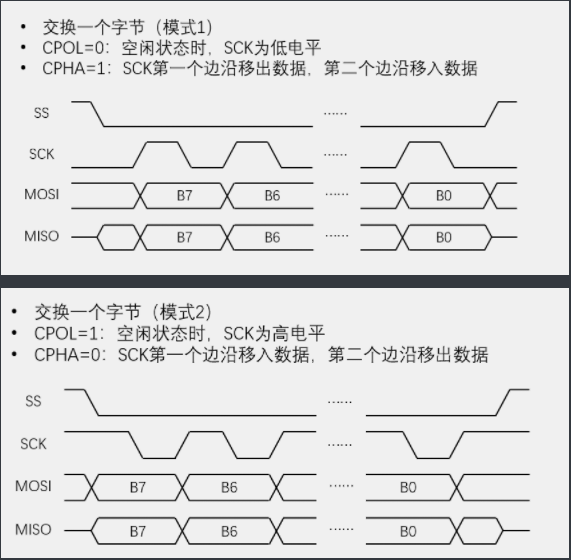

4、SPI时序基本单元

•起始条件:SS从高电平切换到低电平

•终止条件:SS从低电平切换到高电平

低电平选中,高点平未选中

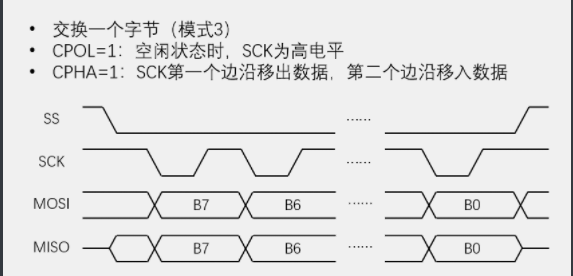

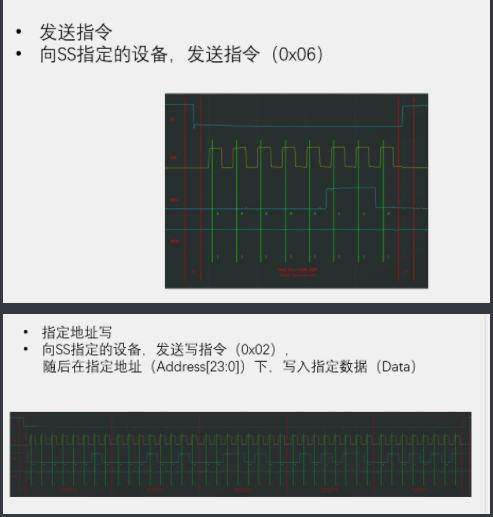

5、SPI时序(以W25Q64芯片为例)

6、W25Q64简介

-

W25Qxx系列是一种低成本、小型化、使用简单的非易失性存储器(数据掉电不丢失),常用于数据存储、字库存储、固件程序存储等场景

-

存储介质Nor Flash(闪存)

-

时钟频率:80MHz / 160MHz(Dual SPI)/ 320MHz(Quad SPI)

-

存储容量(24位地址):

-

W25Q40 : 4Mbit / 512KByte

-

W25Q80: 8Mbit / 1MByte

-

W25Q16: 16Mbit / 2MByte

-

W25Q16: 32Mbit / 4MByte

-

W25Q64: 64Mbit / 8MByte

-

W25Q128: 128Mbit / 16MByte

-

W25Q256: 256Mbit / 32MByte

-

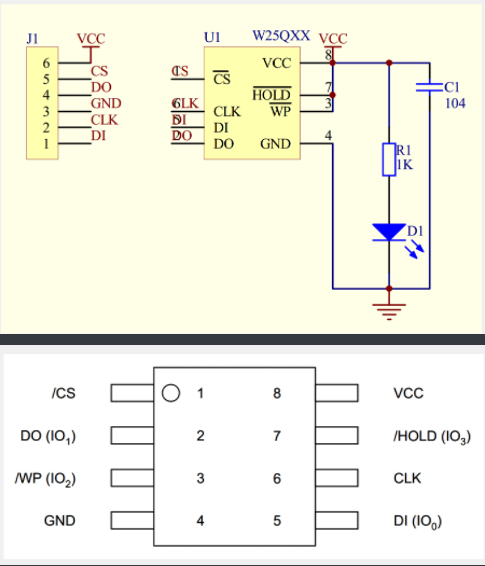

硬件电路

CS低电平有效

WP低电平有效 - WP接低电平,保护,不让写 WP接高电平,不保护,可以写

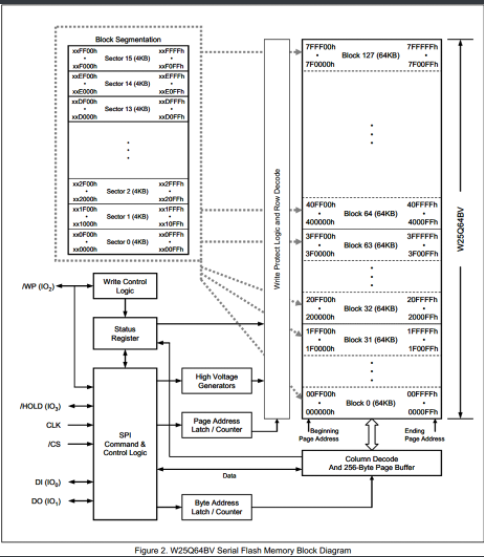

W25Q64框图

容量是8MB,分为128块,一块为64KB,一块分为16个扇区,一个扇区4KB,一个扇区分为16页,一页256字节(RAM存储器)。

flash操作注意事项

-

写入操作时:

-

写入操作前,必须先进行写使能

-

每个数据位只能由1该写为0,不能由0改写为1

-

写入数据前必须先擦除,擦除后,所有数据位变为1(如果不擦除:读出的数据 = 原始数据 & 写入的数据)

-

擦除必须按最小擦除单元进行

-

连续写入多字节时,最多写入一页(256字节 )的数据,超过页尾位置的数据,会回到页首覆盖写入

-

写入操作结束后,芯片进入忙状态,不响应新的读写操作

-

-

读取操作时:

- 直接调用读取时序,无需使能,无需额外操作,没有页的限制,读取操作结束后不会进入忙状态,但不能在忙状态时读取

SPI外设简介

-

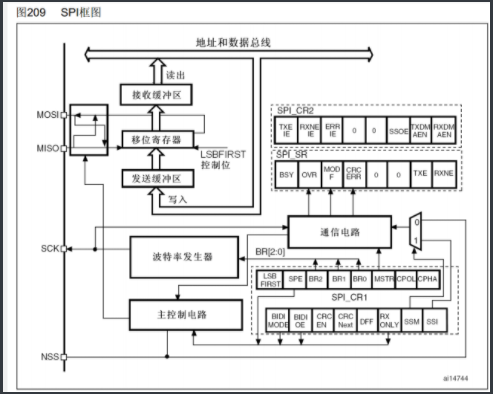

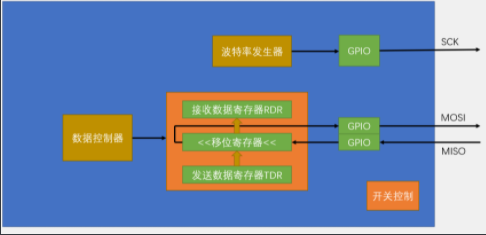

STM32内部集成了硬件SPI收发电路,可以由硬件自动执行时钟生成、数据收发等功能,减轻CPU的负担

-

可配置8位/16位数据帧、高位先行/低位先行

-

时钟频率:fPCLK/(2,4,8,16,32,64,128,256)

-

支持多主机模型、主或从操作

-

可精简位半双工/单工通信

-

支持DMA(用DMA来帮我们自动搬运数据,快速传递大量数据)

-

兼容I2S协议(数字音频信号传输的专用协议)

-

STM32F103C8T6硬件SPI资源:SPI1、SPI2

SPI框图

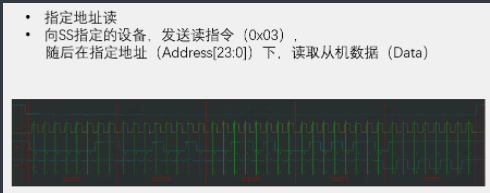

I2C基本结构

时序图

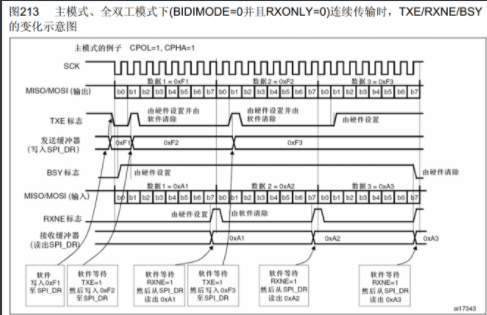

主模式全双工连续传输

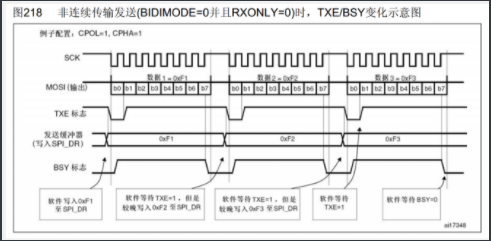

非连续传输

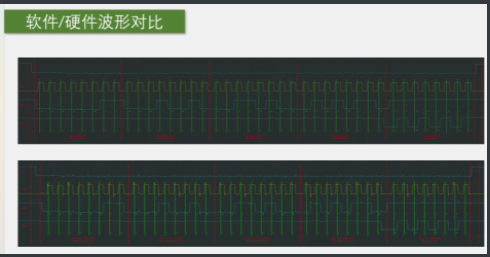

软硬件波形对比(上面是软件/下面是硬件)

浙公网安备 33010602011771号

浙公网安备 33010602011771号