【PCIe Equalization 详解】

为什么要做Equalization

电信号传输过程中,当前bit会阻碍下一个bit电压翻转,这种影响叫符号间干扰(inter‐symbol interference(ISI))。当电压变化越快这种影响会越小,反之连续的相同电压持续时间越长影响越大,当电压转换时就需要更长的时间去抵消这种影响。

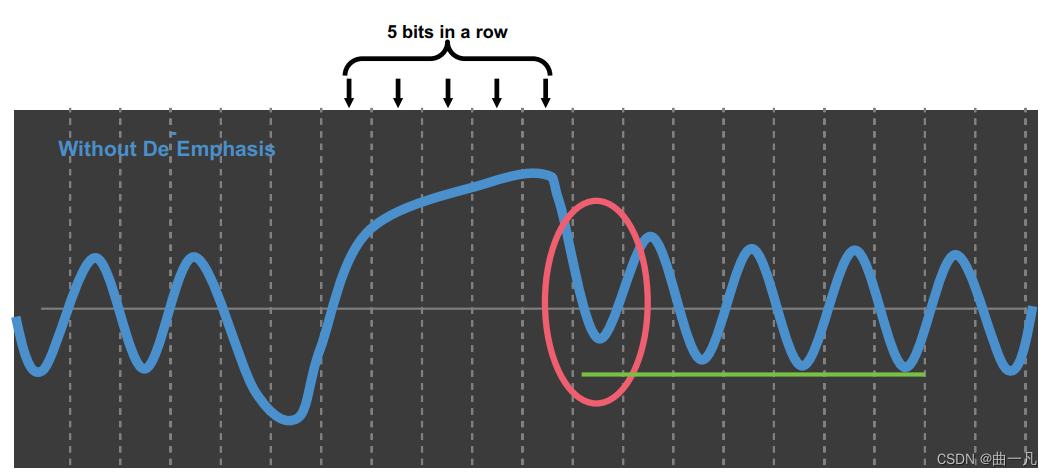

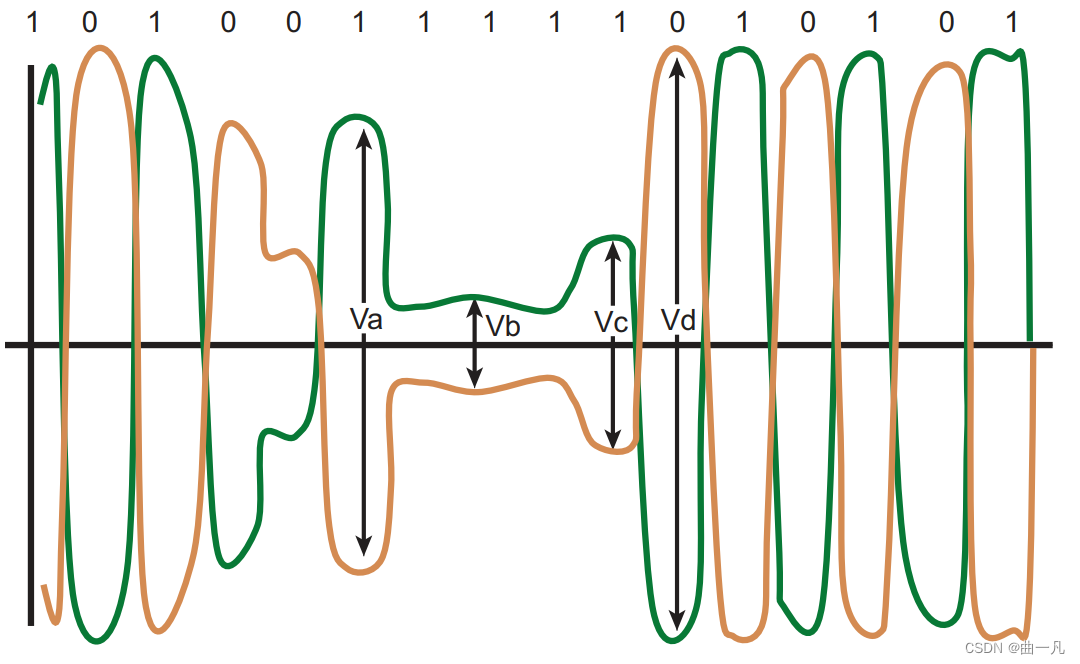

所以当信号频率增加(一个bit持续时间变短)且有连续相同的信号传输时,由于上述描述ISI的存在会导致翻转的那一bit采样错误。下图用具体的例子来表示ISI的影响。

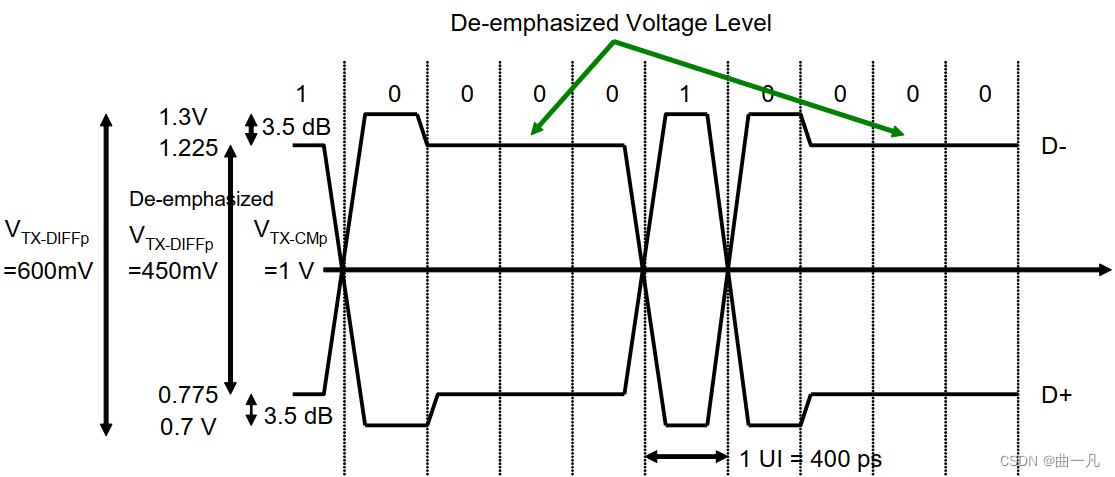

在PICe Gen1 & Gen2 时,为了解决ISI导致的信号失真,PCIe Spec引入了De-Emphasis技术,De-Emphasis通过降低连续相同bit流中第二个bit及以后所有信号来降低这种影响。下图表示De-Emphasis技术的实现。

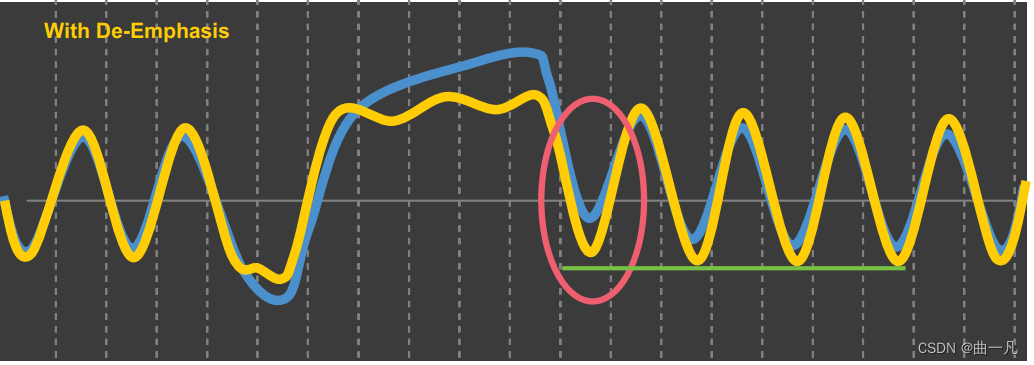

下图表示De-Emphasis 对信号失真的优化。

当PCIe 发展到Gen3及以上时,信号编码方式改变以及信号频率增加,De-Emphasis技术不能满足系统误码率(Bit Error Rate(BER))的要求,所以引入了Equalization技术。

Equalization 原理

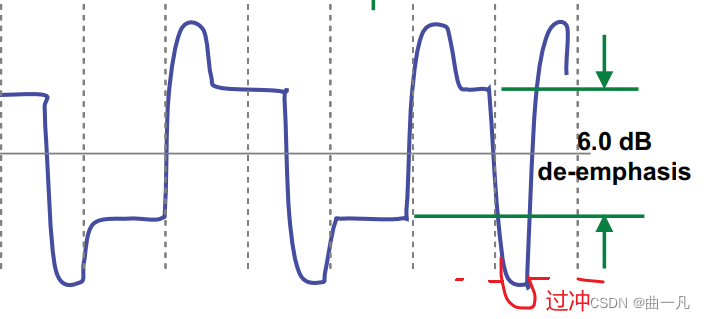

Gen3及以上使用128B/130B 编码方式,会引入更多连续相同的信号传输,且随着每个bit的时间会变的更短,使用上述讲到的De-Emphasis如果过大可能会导致过冲:

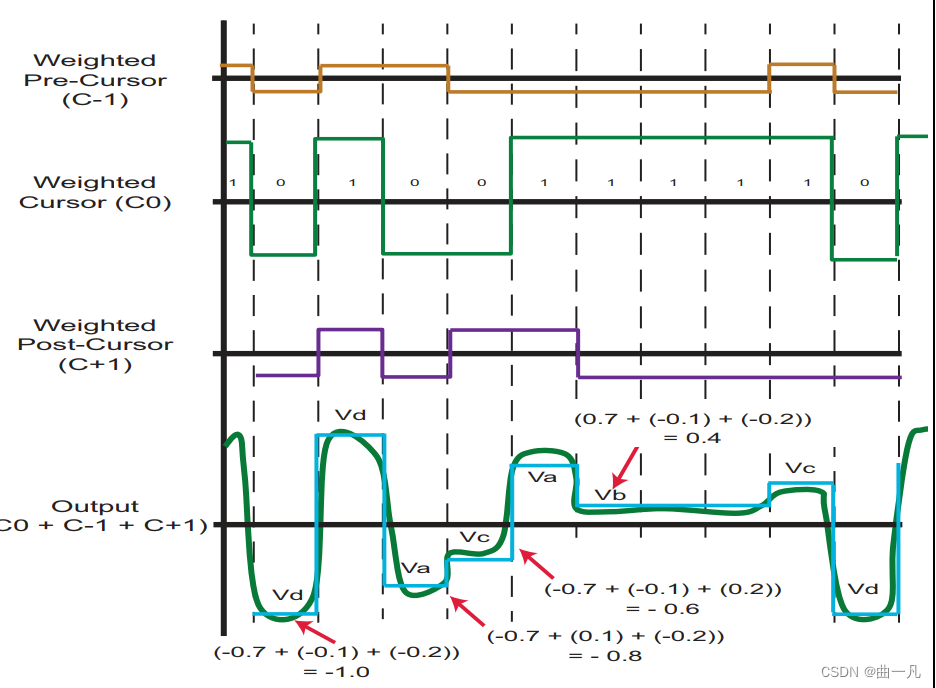

所以Equalization 使用三阶滤波器引入了pre-shoot:

图中Vc 是Pre-shoot 电压,Vb 是De-Emphasis 电压,Va 是连续bit 流的第一个电压也叫normal电压,Vd是没有连续bit流存在时的电压。以上途中波形是Equalization 引入的三阶滤波器实现的。

可以看到三阶滤波器引入三个滤波器参数:C-1, C0, C1,分别表示的是提前一个bit 的信号比重,当前bit信号的比重,延后一个bit的比重,这三个参数的设置及规则将在后续章节进行详细介绍。

下面用一个例子来说明三阶滤波器怎么实现上述四种不同电压的:

Example:

发送端电压为1;C-1=-0.1;C0=0.7;C1=-0.2

- 第一个Vd 由于没有连续bit流所以提前一个bit和延后一个bit的值都应该为1,加上比重系数的影响。

Vd = -0.1(C-1) * 1 + 0.7(C0) * -1 + -0.2(C1)*1 = -1;

- 第一个Va当前值为1,提前一个bit应该为-1,延后一个bit应该1,加上比重系数的影响。

Va = -0.1(C-1) * -1 + 0.7(C0) * -1 + -0.2(C1) * 1 = -0.8;

- 第一个Vc当前值为-1,提前一个bit应该为1,延后一个bit应该-1,加上比重系数的影响。

Vc = -0.1(C-1) * 1 + 0.7(C0) * -1 + -0.2(C1) * -1 = -0.6;

- Vb当前值为1, 提前一个bit应该为1,延后一个bit应该1,加上比重系数的影响。

Vb = -0.1(C-1) * 1 + 0.7(C0) * 1 + -0.2(C1) * 1 = 0.4;

- 第二个Vc当前值为1,提前一个bit应该为-1,延后一个bit应该1,加上比重系数的影响。

Vc = -0.1(C-1) * -1 + 0.7(C0) * 1 + -0.2(C1) * 1 = 0.6;

从例子中可以看出由于三阶滤波器的引入,Pre-Shoot可以通过设置C-1是否为0 来单独应用单独使用De-Emphasis。

- 单独使用De-Emphasis;C-1=0,C1!=0(此时Vb=Vc);

- 都用C-1!=0;C1!=0;

当C-1为0时就可以向后兼容Gen1和Gen2的De-Emphasis。

PHY 怎么要求对端更新coefficients

在链路交换数据过程中,phy一直在评估误码率(BER)。PHY会通过messagebus向MAC的RX Evaluation Statuses 寄存器更新Evaluation的状态,controller根据这些状态寄存器来判断是否需要做Equalization。

PHY具体怎么评估误码率时模拟的只是还需要学习!

LTSSM跳到Equalization的条件

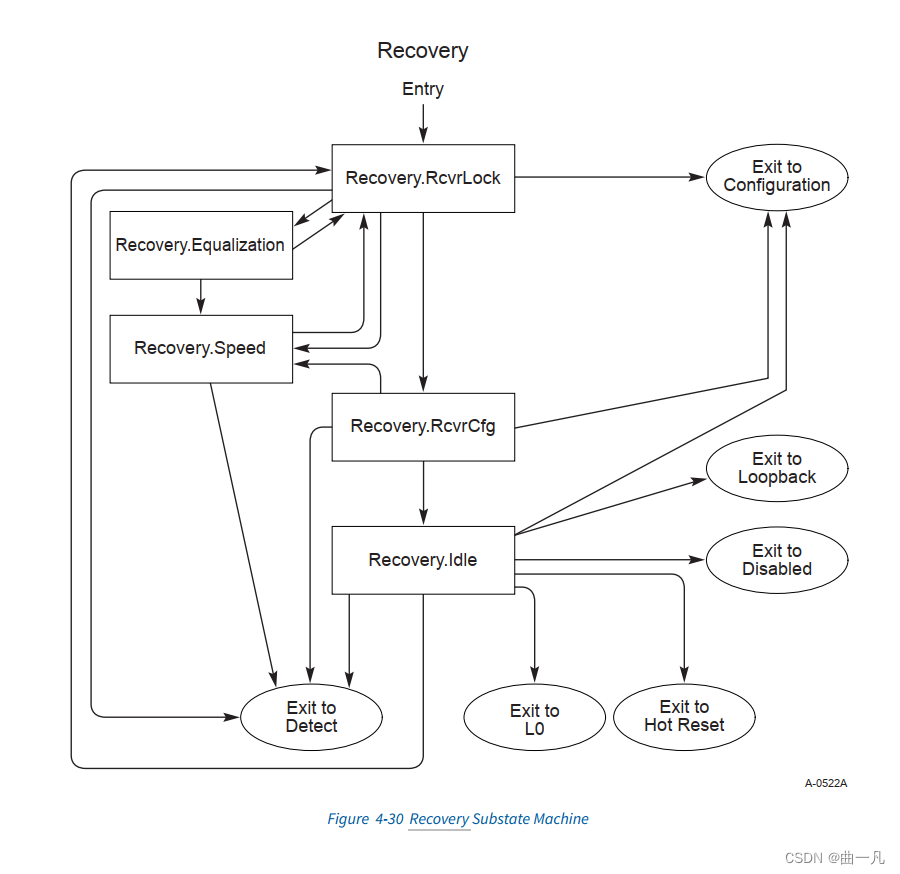

从recovery状态机中可以看出,进入Equalization有且只有一个入口就是Recovery.RcvrLock(有两种情况,1. 第一次做eq 2. 第二次做eq,即redo)。

DownStream Port 和 Upstream Port 从Recovery.RcvrLock 进入的条件不一样:

- start_equalization_w_preset = 1;

- start_equalization_w_preset = 0; (This Equalization will be cased by Downstream Port)

- DownStream Port:

- Recovery.RcvrLock is not from Configure.Idle or Recovery.Idle.

- Perform Equalization bit of Link_Control_3_Register is set to 1.

- Upstream Port:

- Receive 8 consecutive TS1 Ordered Sets with the same lane_id and link_id on all configured Lanes.

- Speed_Change bit is 00

- EC bits are not 00

- DownStream Port:

Equalization 参数介绍

Equalization初始值该怎么设置:

Equalization 初始值设置在第一次做EQ和redo的时候也是不一样的,如下:

下行端口(Downstream Port)

- 8.0 GT/s

- 发送端预设(Transmitter Presets)

必须使用其通道均衡控制寄存器(Lane Equalization Control Register)中定义的发送端预设。 - 接收端预设提示(Receiver Presets Hint)

可以选择性地使用其通道均衡控制寄存器中定义的接收端预设。

- 发送端预设(Transmitter Presets)

- 16.0 GT/s 及以上

- 发送端预设(Transmitter Presets)

- 使用在恢复配置(recovery.cfg)中连续 8 个 TS2 中接收到的发送端预设。

- 使用其通道均衡控制寄存器中定义的发送端预设。

情况 1 的优先级高于情况 2。

- 接收端预设提示(Receiver Preset Hint)

可以选择性地使用其通道均衡控制寄存器中定义的接收端预设。

- 发送端预设(Transmitter Presets)

上行端口(Upstream Port)

- 发送端预设(Transmitter Presets)

必须使用在恢复配置(recovery.cfg)中连续 8 个 TS2 中接收到的发送端预设。 - 接收端预设提示(Receiver Preset Hint)

可以使用在恢复配置(recovery.cfg)中连续 8 个 TS2 中接收到的接收端预设。

重新均衡(redo)

在这种情况下,下行端口和上行端口都要使用上次 Equalization 协商的结果。

Equalization 参数规则

详见Spec Table 8-1。

Equalization 各个Phase详解

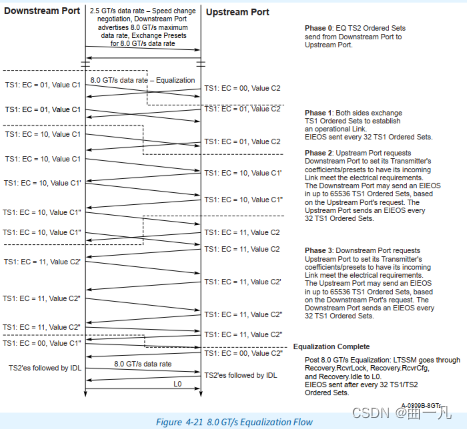

Phase0

只有Upstream Port 存在Phase0,在改状态Upstream Port 发送EC = 00的TS1s。TS1s 中的preset 以及coefficients 是在recovery.cfg状态接受到的TS2s中记录的。

同时Upstream Port PHY检测信号误码率(10-4), 如果误码率低于10-4 意味着Upstream Port可以可靠的接收到TS1s。在误码率满足条件的情况下如果收到两个连续的EC=01的TS1s,Upstream Port将会跳到Phase1。

Summary:Upstream Port 通过发送EC = 0的TS1s来调教Downstream Port Equalization参数。

Phase1

Upstream Port在Phase 1接收Downstream Port 发送的TS1s,如果TS1s中的Equalization参数是合法的,那么Upstream port将使用该组参数来调整自己的发送和接收端的滤波器系数,并通过TS1s返回收到的参数。否则返回reject flag。Upstream Port在收到两个连续带有EC='b10的TS1 之后跳到Phase 2。

Downstream Port在Phase 1做的工作与Upstream Port在Phase 0做的工作相似,当满足误码率要求,并且收到连续两个带有EC=01的TS1s 时跳到Phase 2。

Summary:Downstream Port 通过发送EC = 'b01的TS1s来调教Upstream Port Equalization参数。

Phase2

Upstream Port 在Phase 2检测误码率(10^-12),如果误码率不满足则会发送带有新preset/coeffcients 并且EC=’b10的TS1s。如果误码率满足要求则跳到Phase 3,并发送EC='b11的TS1s。

Downstream Port在Phase 2中接收Upstream Port 的TS1s,并且check 接收到TS1s中的presets/coefficients是否满足条件,如果满足则根据接收到的参数来设置自己的发送和接收的滤波器系数,否则返回返回reject flag,当接收到EC='b11的TS1s跳到Phase3。

Summary: Upstream Port 通过发送EC = ‘b10的TS1s来调教Downstream Port Equalization参数。

Phase3

Phase 3 做的工作与Phase 2相似,Downstream Port通过发送EC = ‘b10的TS1s来调教 Upstream Port Equalization参数。

Equalization 各个Phase跳转

下图完整的描述了Equalization 各个Phase跳转顺序及条件。

浙公网安备 33010602011771号

浙公网安备 33010602011771号