【ARM Cache 与 MMU 系列文章 1.6 -- ARM Cache 全相连 详细介绍】

Cache 全相连(Fully Associative)

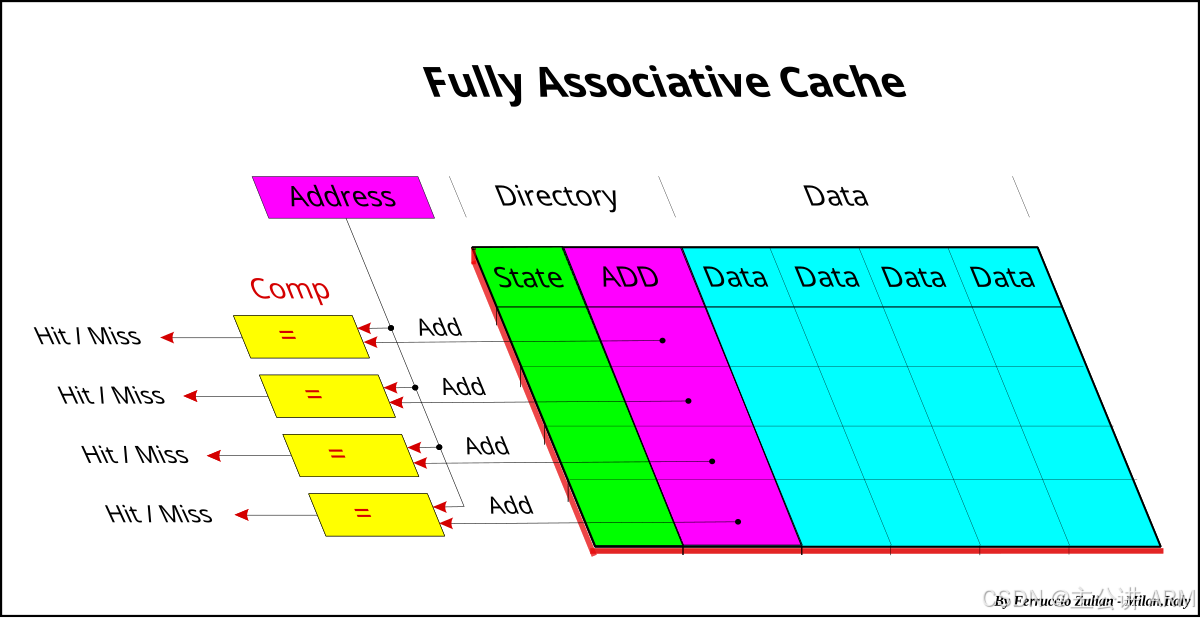

介绍: 在全相连缓存中, 任何内存地址都可以缓存在 Cache 的任何位置 。在查找数据时,缓存会并行检查所有的缓存行,以确定所需数据是否已缓存。这种组织结构的优点是高命中率, 但缺点是查找过程需要更复杂的硬件 ,导致成本和功耗增加。

全相联映射示例

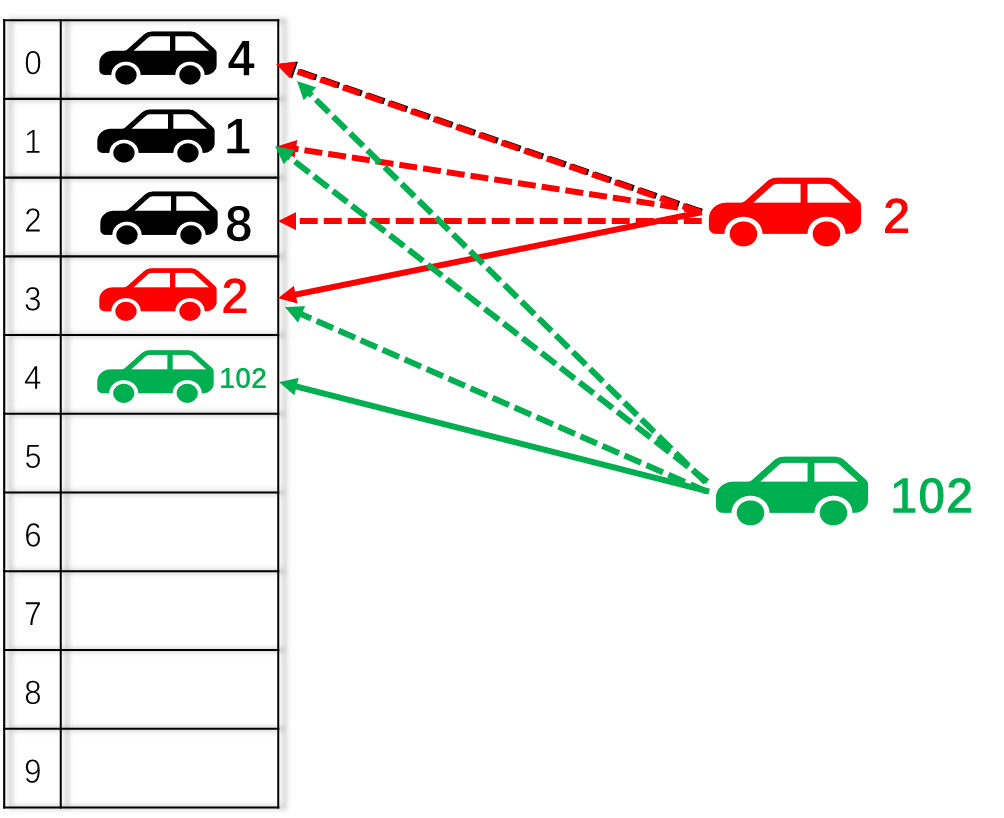

全相联映射规则下的停车场类似与现实生活中的停车场。如下图1-1所示,任意车牌号的车可以停任何车位,有空位就可以停。

假设当前车位0,1,2都有车子占了,2号车子来了,它会按照一定的策略(replacement policy)来找空车位,本示例中是按照顺序查找。当它发现3号车位是空的时候,就把车子进去。102号车也是如此,停在了4号车位。

问题随之而来 ,当车主想要取车时,并不知道自己的车子停在了哪个车位。在最坏的情况下,需要遍历整个停车场(比较9次)才能找到自己的车。

全相联映射规则停车场的优势在于停车方便,车位利用率高,只要有空车位就能停进去。缺点是取车时比较困难,有可能需要遍历整个停车场才能找到自己的车。

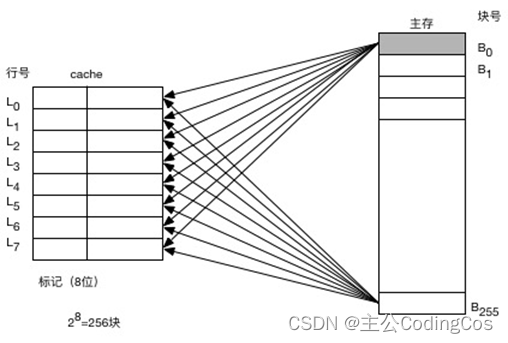

全相联映射原理

主存中的任意一个地址可被映射进cache中的任意cache line,这就是全相联映射。正如上面的全相联映射停车场一样,虽然cache的利用率提高了,但是CPU 读写一个地址时,cache controler需要进行cache look-up才能知道是否发生hit 或者miss。在最坏的情况下,需要遍历整个cache,逐一比较才能得出是否hit的结论。

浙公网安备 33010602011771号

浙公网安备 33010602011771号