【ARM Cache与MMUMPU 系列文章 1.1 -- 如何获取 Cache size 的大小?】

ARMv8/v9 CPU Cache Size

ARM架构通过一系列的系统寄存器来提供CPU和系统的详细信息,包括缓存的大小和配置。在ARMv8和ARMv9架构中,这些信息通常可以通过读取如下寄存器来获取:

-

CTR_EL0 (Cache Type Register) : 提供L1缓存的线大小等信息。

-

CLIDR_EL1 (Cache Level ID Register) : 描述了存在哪些级别的缓存和每级缓存的类型。

-

CSSELR_EL1 (Cache Size Selection Register) : 用于选择想要查询的缓存级别和类型(数据缓存或指令缓存)。

-

CCSIDR_EL1 (Current Cache Size ID Register) : 根据CSSELR_EL1的选择,提供关于选定缓存的大小和组织的信息。

关于这几个寄存器的详细内容见文章 : 【ARM Cache 及 MMU 系列文章 6.1 – Cache maintenance 相关寄存器及指令详细介绍】

下面以 ARMv9 架构下的 Cortex-A520 为例介绍如何读取 CPU 各级cache size 的方法。

Cache Size 的计算方法

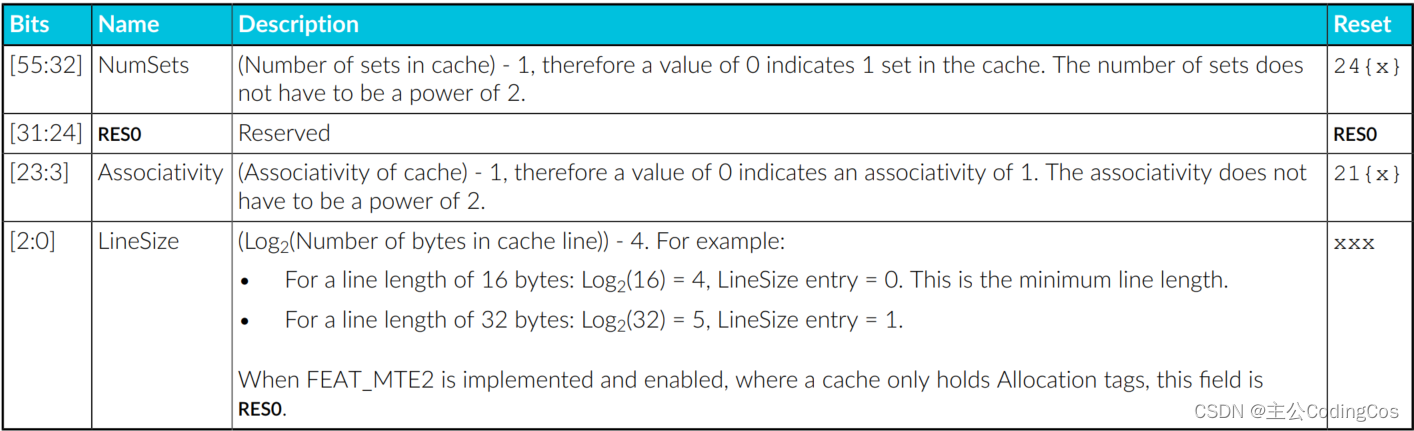

case size 的大小等于 Set * Way * CacheLine ,相关信息位于 CCSIDR_EL1 寄存器中,如下:

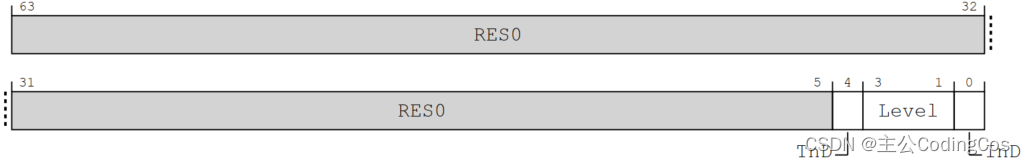

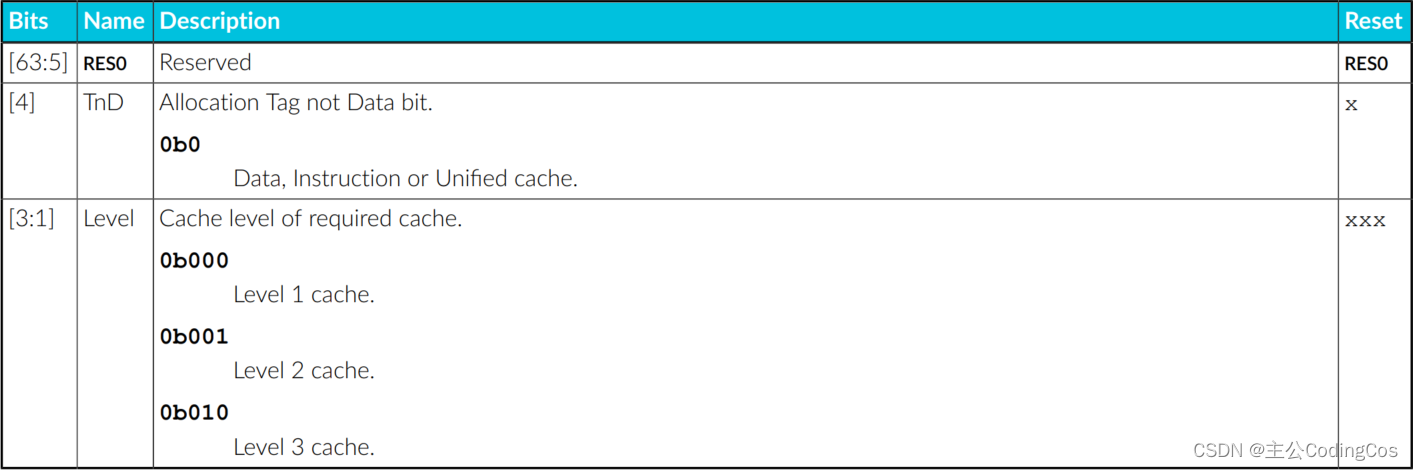

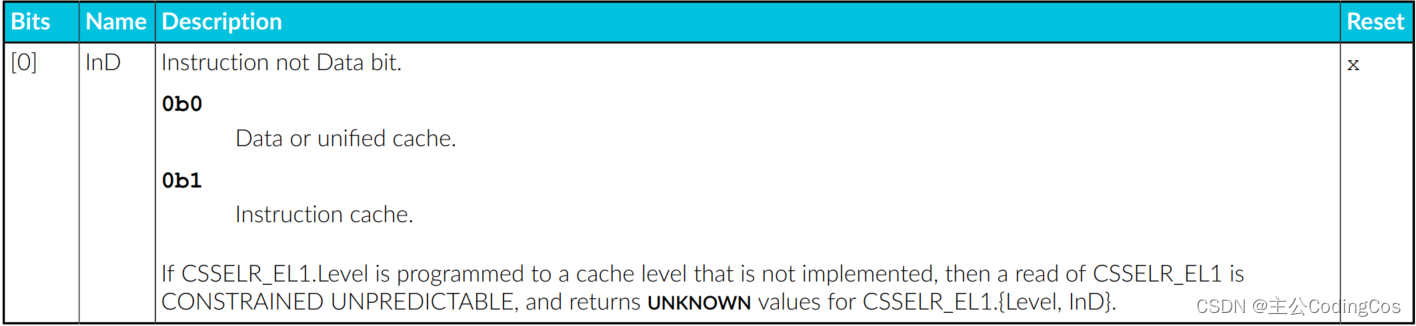

所以通过读取 CCSIDR_EL1, Current Cache Size ID 寄存器,就可以获取 Cache Size 的大小,但是我们知道在一个大的Soc 系统中,Cache 往往是多级的,所以首先我们需要指定要读取哪一级Cache 以及读取Cache 的类型是 Data Cache 还是 Instruction Cache,可以通过配置寄存器 CSSELR_EL1 , Cache Size Selection Register 来决定要操作的寄存器:

接下来以读取L3 Cache Size 的大小为例进行介绍,L2/L1 cache 读取类似于L3 Cache Size 的读取。

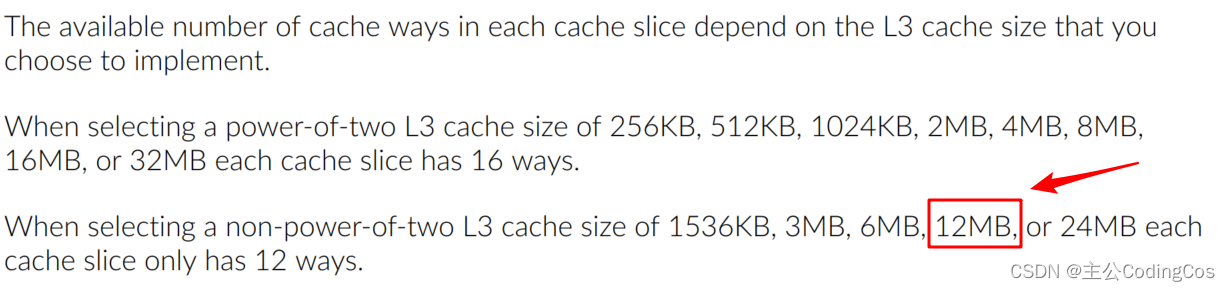

我们知道 在 DSU-120 中 L3 的 Cache Size 在硬件实现的时候可以配置为12M

Cache Size 读取代码实现

获取L3 Data Cache size 的汇编代码实现如下:

func l3_cache_size_get

stp x4, x5, [sp, #-0x10]!

mov x0, xzr

orr x0, x0, 0x4 //select l3 cache

msr csselr_el1, x0

mrs x0, ccsidr_el1

ldp x4, x5, [sp], #0x10

ret

endfunc l3_cache_size_get

声明获取函数:

uint64_t l3_cache_size_get(void);

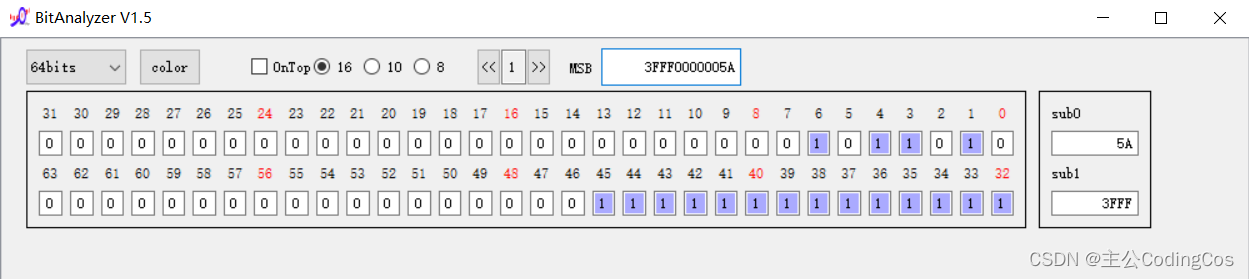

当在执行完函数 l3_cache_size_get() 之后会返回 ccsidr_el1 寄存器的值,如下:

由 bit[2:0] = 0x2 可以知 CacheLine的大小为64bytes;

由 bit[23:3] = 0xB , 可知 一共有 12路;

由 bit[55:32] = 0x3FFF , 可知 一共有 16384组;

所以 L3 Cache Size 的大小为 12 * 16384 * 64B = 12MB

浙公网安备 33010602011771号

浙公网安备 33010602011771号