【ARMv8v9 GIC 系列 1.7 -- GIC PPI SPI SGI LPI 中断使能配置概述】

GIC 各种中断使能配置

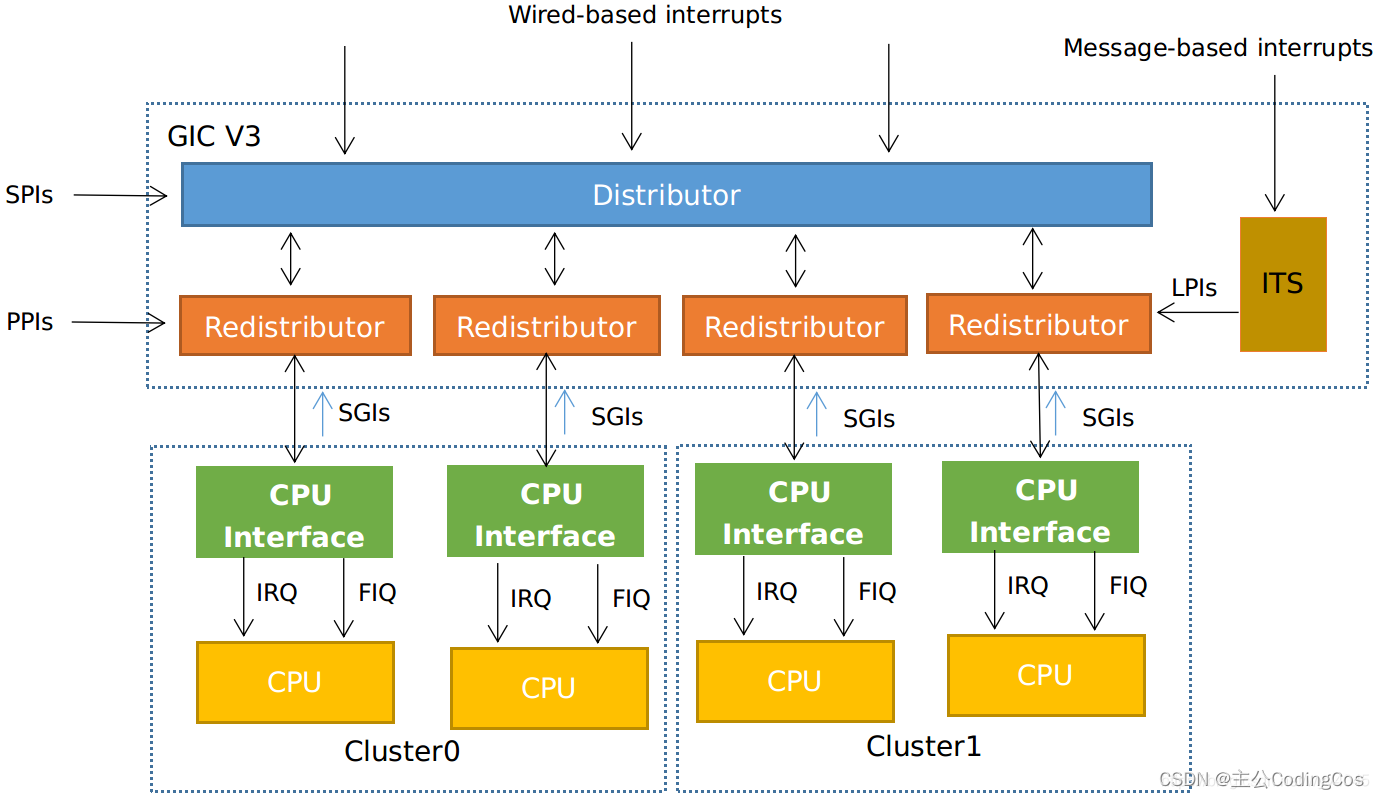

在ARM GICv3和GICv4架构中,不同类型的中断(如PPIs、SPIs、SGIs和LPIs)可以通过 不同的 方式进行启用和禁用。

下面详细介绍这些中断的启用和禁用方法:

PPIs(每个处理器私有中断)

- 启用和禁用PPIs :通过向

GICR_ISENABLER0和GICR_ICENABLER0寄存器写入,可以在启用了亲和性路由的安全状态下,启用和禁用PPIs。

如果支持并配置了物理中断的传统操作,对于PPIsn = 0,也就是只有一个寄存器。可以通过向GICD_ISENABLER<n>和GICD_ICENABLER<n>写入来单独启用和禁用PPIs。

物理中断的传统操作模式 (“Legacy Operation for Physical Interrupts”)通常指的是对早期 ARM架构 的支持,其中中断管理方式可能与最新的GIC规茅有所不同。这种传统操作模式允许兼容旧的中断处理机制,使得新的GIC能够在不完全遵循最新GIC规范的环境下工作,以确保对旧硬件或软件的兼容。

- 扩展PPI范围 :在可选的扩展PPI范围内,PPIs可以通过写入

GICR_ISENABLER<n>E和GICD_ICENABLER<n>E来启用和禁用。

SPIs(共享外设中断)

- 启用和禁用SPIs :通过向

GICD_ISENABLER<n>和GICD_ICENABLER<n>寄存器写入,可以启用和禁用SPIs,其中n > 0对于SPIs。 - 扩展SPI范围 :在可选的扩展SPI范围内,SPIs可以通过写入

GICD_ISENABLER<n>E和GICD_ICENABLER<n>E来启用和禁用。

SGIs(软件生成的中断)

- 启用和禁用SGIs :当启用了亲和性路由时,可以通过向

GICR_ISENABLER0和GICR_ICENABLER0写入来启用和禁用SGIs。

如果支持并配置了物理中断的传统操作,那么对于SGIs,n = 0,也可以通过向GICD_ISENABLER<n>和GICD_ICENABLER<n>写入来单独启用和禁用SGIs。SGIs是否可以通过写入GICR_ISENABLER0和GICR_ICENABLER0永久启用或禁用,取决于具体实现。

LPIs(局部中断)

- 启用LPIs :可以通过在

LPI配置表中设置启用位来启用个别LPIs。关于使用LPI配置表启用LPIs的更多信息,并未在此处详细展开,但基本思路是在LPI配置表中指定每个LPI的配置,包括它们是否被启用。

这种灵活的启用和禁用机制为系统提供了细粒度的中断管理能力,允许根据应用需求和性能考虑,对中断进行精确控制。

浙公网安备 33010602011771号

浙公网安备 33010602011771号