llvm之llc工具

llc 是 LLVM 工具链中的一个核心工具,主要用于将 LLVM 中间表示(IR) 编译为特定目标平台的 可读汇编代码(.s) 或 目标文件(.o)

在LLVM 生态中,llc 是 连接前端(如 Clang)与后端(如汇编器/链接器)的关键工具,支持:

- 多目标编译:覆盖从 x86 到 WebAssembly 的多种架构

- 灵活优化:通过调整优化级别和硬件特性提升代码性能

- 调试与验证:确保生成的代码正确且高效

- 跨平台开发:简化交叉编译流程

与 clang 直接生成目标代码不同,llc 更适用于需要精细控制 LLVM IR 到目标代码转换的场景(如研究编译器后端或定制代码生成)

H:\svn\llvm\bin\llc.exe --version

LLVM (http://llvm.org/):

LLVM version 11.1.0

Optimized build.

Default target: x86_64-pc-windows-msvc

Host CPU: skylake

Registered Targets:

aarch64 - AArch64 (little endian)

aarch64_32 - AArch64 (little endian ILP32)

aarch64_be - AArch64 (big endian)

arm - ARM

arm64 - ARM64 (little endian)

arm64_32 - ARM64 (little endian ILP32)

armeb - ARM (big endian)

thumb - Thumb

thumbeb - Thumb (big endian)

wasm32 - WebAssembly 32-bit

wasm64 - WebAssembly 64-bit

x86 - 32-bit X86: Pentium-Pro and above

x86-64 - 64-bit X86: EM64T and AMD64

注:AArch64 是 ARM 公司对 64 位 ARM 架构的正式命名,而 ARM64 是行业对其的通用化表达。在绝大多数实际应用中,两者可互换使用,但需注意特定语境下的技术准确性

H:\svn\llvm\bin\llc.exe -march=wasm64 -mattr=help

Available CPUs for this target:

bleeding-edge - Select the bleeding-edge processor.

generic - Select the generic processor.

mvp - Select the mvp processor.

Available features for this target:

atomics - Enable Atomics.

bulk-memory - Enable bulk memory operations.

exception-handling - Enable Wasm exception handling.

multivalue - Enable multivalue blocks, instructions, and functions.

mutable-globals - Enable mutable globals.

nontrapping-fptoint - Enable non-trapping float-to-int conversion operators.

reference-types - Enable reference types.

sign-ext - Enable sign extension operators.

simd128 - Enable 128-bit SIMD.

tail-call - Enable tail call instructions.

unimplemented-simd128 - Enable 128-bit SIMD not yet implemented in engines.

Use +feature to enable a feature, or -feature to disable it.

For example, llc -mcpu=mycpu -mattr=+feature1,-feature2

1. 核心功能

将 LLVM IR 编译为目标代码

输入:LLVM IR(文本格式 .ll 或二进制格式 .bc)

输出:目标平台的汇编代码(.s)或目标文件(.o)

# 生成 x86_64 汇编代码

llc input.ll -mtriple=x86_64-pc-linux-gnu -o output.s

# 生成 ARM32 目标文件

llc input.ll -mtriple=armv7-unknown-linux-gnueabihf -filetype=obj -o output.o

支持多种目标架构

通过 -mtriple 或 -target 指定目标平台 如:x86_64, arm, riscv, wasm32 等

# 编译为 WebAssembly 文本格式

llc input.ll -mtriple=wasm32-unknown-unknown -o output.wat

2. llc重要选项

| 选项 | 作用 |

|---|---|

|

-mtriple=<三元组>或-target <三元组> |

指定目标平台(如 x86_64-pc-linux-gnu) |

| -march=<架构> | 指定目标 CPU 架构(如 x86-64),需与 -mtriple 兼容 |

| -mcpu=<CPU型号> | 指定目标 CPU 型号(如 skylake) |

| -O<级别> | 优化级别(0-3,默认 -O2) |

| -filetype=<类型> | 输出类型:asm(汇编)、obj(目标文件)、null(仅验证)等 |

| -o <文件名> | 指定输出文件 |

3. 目标三元组(triple)

通过 llc -mtriple=<目标三元组>,合理设置 Target Triple,可以精确控制 Clang 生成的目标代码,灵活生成不同平台的代码,适配不同硬件和操作系统

Triple形如:<architecture>-<vendor>-<os>-<environment>

① architecture(架构):如 x86_64, armv7, aarch64, wasm32, wasm64

② 操作系统和 ABI:根据目标平台填写(如 linux-gnu, windows-msvc, darwin 等)

ABI(Application Binary Interface,应用二进制接口)是程序二进制层面的接口规范,规定程序模块(如库、可执行文件、操作系统)之间互操作、调用的格式。 与 API 不同:API(应用程序接口)面对源码、而 ABI 面向编译后的二进制。 主要内容包括: ① 数据类型的二进制表示(如 int、struct、float 的对齐方式和长度) ② 函数调用约定(参数和返回值如何传递?用哪些寄存器?栈怎么布局?) ③ 系统调用约定(操作系统接口参数怎么传递?错误码等如何处理?) ④ 名称修饰和链接规范(C++ name mangling、符号导出规则) ⑤ 异常处理机制(跨语言、跨模块时怎么办?)

常见目标三元组

| 架构 | 目标三元组示例 | 说明 |

|---|---|---|

| x86_64 |

x86_64-pc-linux-gnu |

64位 Linux 系统(gnu工具链) |

|

x86_64-pc-windows-msvc |

64位 Windows系统(msvc工具链) |

|

|

x86_64-unknown-linux-gnu |

64位通用Linux系统(gnu工具链) |

|

| ARM |

armv7-unknown-linux-gnueabihf |

ARM 32位(Armv7)通用Linux系统(gnu工具链) |

|

armv7-none-eabi |

ARM 32位(Armv7)嵌入式系统(无操作系统) |

|

| AArch64 |

aarch64-linux-gnu |

ARM 64位(Armv8)Linux 系统(gnu工具链) |

|

aarch64-apple-darwin |

ARM 64位(Armv8)macOS系统 |

|

| aarch64-pc-windows-msvc | ARM 64位(Armv8)Windows系统(msvc工具链) | |

| aarch64-linux-android | ARM 64位(Armv8)Android 应用程序 | |

| aarch64-none-linux-android21 | ARM 64位(Armv8)系统是Linux Android,API级别21 | |

|

ARM64 |

arm64-apple-ios11.0.0 | ARM 64位(Armv8)iOS系统 |

| RISC-V | riscv64-unknown-linux-gnu | RISC-V 64位 Linux 系统(gnu工具链) |

| WebAssembly 32bit | wasm32-unknown-unknown | WebAssembly 32位 |

| WebAssembly 64bit | wasm64-unknown-wasi | WebAssembly 64位 |

| MIPS | mips-linux-gnu | MIPS Linux 系统(gnu工具链) |

4. 优化控制

通过 -O<级别> 指定优化级别(-O0 到 -O3,默认 -O2),控制生成的代码性能

# 启用最高优化级别

llc input.ll -O3 -mtriple=aarch64-linux-gnu -o output.s

5. 输出格式控制

使用 -filetype 指定输出类型:

asm:汇编代码(默认)obj:目标文件(需目标平台支持)null:仅验证输入,不生成输出

# 生成目标文件(需目标后端支持)

llc input.ll -filetype=obj -o output.o

6. 目标平台参数调整

指定 CPU 型号:-mcpu=<型号> 如: -mcpu=skylake

启用硬件特性:-mattr=<特性> 如: +avx2, +simd128

# 为 RISC-V 启用压缩指令扩展 llc input.ll -mtriple=riscv64-unknown-linux-gnu -mattr=+c -o output.s

7. 调试与分析

生成调试信息:通过 -debug 或 -print-after-all 输出编译过程日志

时间报告:-time-passes 显示各编译阶段耗时

# 输出详细的编译过程日志

llc input.ll -mtriple=x86_64-pc-linux-gnu -debug -o output.s

8. 验证 LLVM IR

检查 IR 的合法性,确保其符合 LLVM 规范

# 仅验证 IR,不生成代码 llc input.ll -filetype=null -verify-machineinstrs

9. 跨平台与交叉编译

生成非本机平台的代码(如在 x86 机器上生成 ARM 代码)

# 交叉编译到 ARMv7

llc.exe input.ll -mtriple=armv7-unknown-linux-gnueabihf -o output.s

注:x86机器上的llc.exe工具的Registered Targets中必须有ARM,才能生成ARM代码,详见llc.exe --version命令的输出

10. 插件化架构

支持通过插件扩展目标后端(如自定义芯片架构)

# 加载自定义目标插件

llc -load my_target_plugin.so input.ll -mtriple=my-custom-arch -o output.s

11. 高级功能

分阶段编译(Split Compilation)

将 IR 分割为多个模块独立编译,再链接为完整程序。

链接时优化(LTO)

生成 LTO 兼容的目标文件,支持后续链接时优化。

# 生成 LTO 目标文件

llc input.ll -mtriple=x86_64-pc-linux-gnu -filetype=obj -o output.o -enable-lto

12. 典型应用场景

| 场景 | 命令示例 |

|---|---|

| 生成可读汇编代码 |

|

| 生成x86_64可读汇编代码 |

注1:-O2表示启用优化级别 2 注2:-o output.s表示输出可读汇编代码 |

| 交叉编译嵌入式系统代码,生成 ARM 目标文件 |

注:-filetype=obj表示生成目标文件(.o) |

| 验证 IR 正确性 |

|

| 启用 SIMD 优化,生成 WebAssembly 文本格式 |

注1:-mattr=+simd128表示启用 SIMD 扩展 注2:输出为 WebAssembly 文本格式(.wat) |

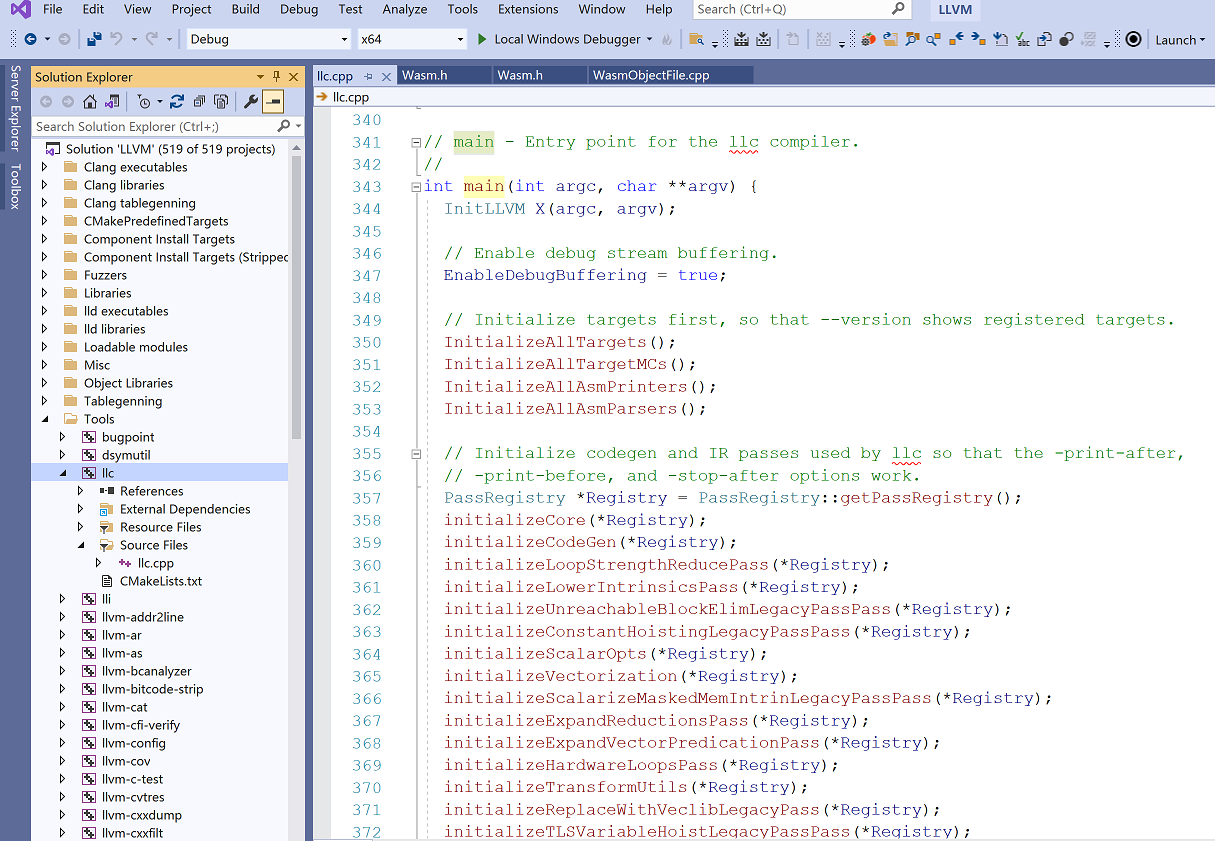

13. 生成的VS工程

注:G:\svn\llvm-project\llvm\tools\llc\llc.cpp

浙公网安备 33010602011771号

浙公网安备 33010602011771号