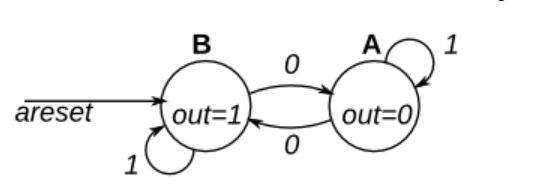

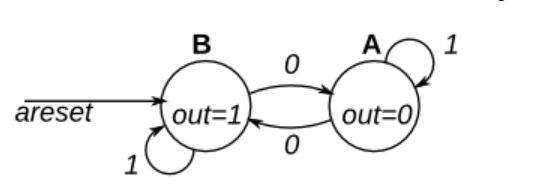

This is a Moore state machine with two states, one input, and one output. Implement this state machine. Notice that the reset state is B.

This exercise is the same as fsm1s, but using asynchronous reset.

题目网站

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

//声明了这是一个组合逻辑电路

// State transition logic

case(state)

A:begin

if(in) begin

next_state=A;

end

else begin

next_state=B;

end

end

B:begin

if(in) begin

next_state=B;

end

else begin

next_state=A;

end

end

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

//实现异步复位

// State flip-flops with asynchronous reset

if(areset)begin

state<=B;

end

else begin

state<=next_state;

end

end

// Output logic

// assign out = (state == ...);

assign out=(state==B);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号