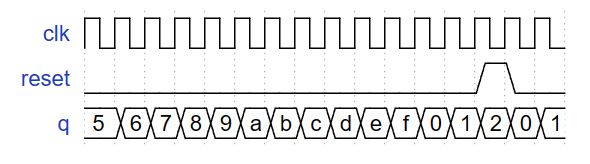

Four-bit binary counter

Build a 4-bit binary counter that counts from 0 through 15, inclusive, with a period of 16. The reset input is synchronous, and should reset the counter to 0.

1 module top_module (

2 input clk,

3 input reset, // Synchronous active-high reset

4 output [3:0] q);

5 always @(posedge clk)begin

6 if(reset)begin

7 q<=4'b0;

8 end

9 else begin

10 q<=q+1'b1;

11 end

12 end

13

14 endmodule

使用了一个if-else语句,但是只是符合这一种情况,可能是我多想了,总觉得如果只是这么书写的话,如果出现毛刺干扰,岂不是直接就变了。

因为重置延迟一拍,所以采用时序逻辑电路实现。

要求比较简单,通常作为大型工程里面的一个总计数器,当做节拍器来使用。

浙公网安备 33010602011771号

浙公网安备 33010602011771号