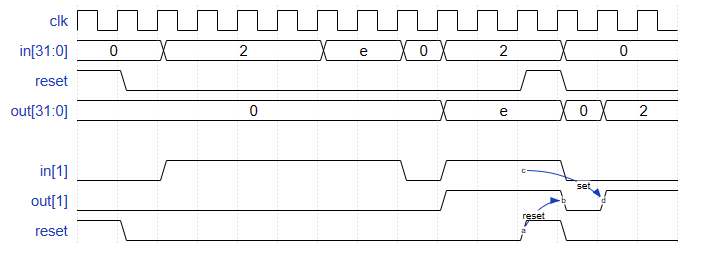

edge capture register

题目如下:

For each bit in a 32-bit vector, capture when the input signal changes from 1 in one clock cycle to 0 the next. "Capture" means that the output will remain 1 until the register is reset (synchronous reset).

代码如下:

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] temp_in;

always @(posedge clk) begin

temp_in <= in;

end

always @(posedge clk) begin

if(reset)begin

out<=32'b0;

//如果复位,则输出变为0

end

else begin

out<=temp_in & ~in | out;

/*temp_in & ~in这一步是检测下降沿,若有下降沿,则触发out为1;然后或逻辑,实际上

实现了保持之前的状态,因为如果之前为1,则无论是否有上升沿或者下降沿,out仍然为1,并不改变

如果out之前为0,那当然也还是不会改变。除非复位发生*/

end

end

endmodule

另外,将两个时序always写在一起没有关系,只不过要明白这一题的复位信号并不管辖暂存信号

module top_module (

input clk,

input reset,

input [31:0] in,

output [31:0] out

);

reg [31:0] temp_in;

always @(posedge clk) begin

temp_in <= in;

if(reset)begin

out<=32'b0;

end

else begin

out<=temp_in & ~in | out;

end

end

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号