detect an edge

题目如下:

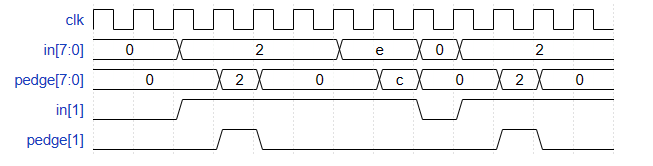

For each bit in an 8-bit vector, detect when the input signal changes from 0 in one clock cycle to 1 the next (similar to positive edge detection). The output bit should be set the cycle after a 0 to 1 transition occurs.

代码如下:

module top_module (

input clk,

input [7:0] in,

output [7:0] pedge

);

reg [7:0]temp;

always@(posedge clk)begin

temp<=in;

pedge<=~temp∈

end

endmodule

要明白题目意思,输入进来一个8位数据,但是我们只要判断其第二位也就是in[1]的变化,当有一个上升沿,则在下一周期pedge变高一次

因为pedge的变化比上升沿慢一拍,所以他的实现应该放在时序always中

浙公网安备 33010602011771号

浙公网安备 33010602011771号