dffs and gates

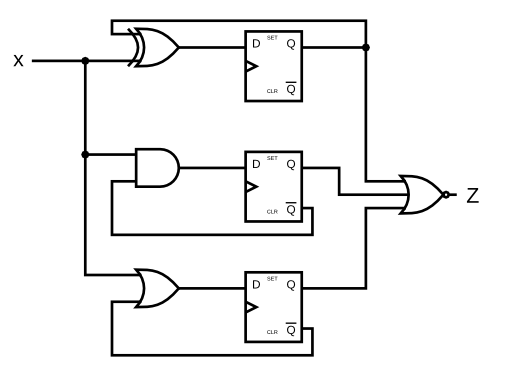

Given the finite state machine circuit as shown, assume that the D flip-flops are initially reset to zero before the machine begins.

Build this circuit.

Exams/ece241 2014 q4 - HDLBits (01xz.net)

1 module top_module ( 2 input clk, 3 input x, 4 output z 5 ); 6 reg Q1,Q2,Q3; 7 always @(posedge clk) begin 8 Q1 <= (x ^ Q1); 9 Q2 <= (x & ~Q2); 10 Q3 <= (x | ~Q3); 11 end 12 assign z = ~(Q1|Q2|Q3); 13 14 endmodule

module top_module ( input clk, input x, output z ); wire q1,q2,q3; wire d1,d2,d3; assign d1=x^q1; assign d2=x&(~q2); assign d3=x|(~q3); assign z=~(q1|q2|q3); always@(posedge clk)begin q1<=d1; q2<=d2; q3<=d3; end endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号