mux and dff(2)

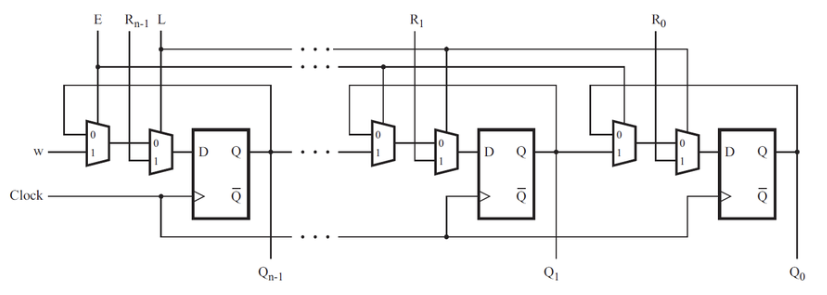

Consider the n-bit shift register circuit shown below:

Exams/2014 q4a - HDLBits (01xz.net)

1 module top_module ( 2 input clk, 3 input w, R, E, L, 4 output Q 5 ); 6 always @(posedge clk) begin 7 case({E,L}) 8 2'b00:Q<=Q; 9 2'b01:Q<=R; 10 2'b10:Q<=w; 11 2'b11:Q<=R; //没有看懂,这里的QRWL怎么使用的 12 endcase //大概理解了什么意思 13 end 14 endmodule

再写:

这里的caseLE,实际上就是将两个选择器放在一起比较了,还是容易理解的

浙公网安备 33010602011771号

浙公网安备 33010602011771号