数字后端要撒哪些sparecell,撒多少合适 ------ 转载

本文转载自: https://mp.weixin.qq.com/s/y2j_dRF672a3VtWrUILDog

从有利于功能ECO、时序ECO,且尽量减少面积比例的角度看,APR阶段要撒哪些sparecell,撒多少合适?

我们下面从几个方面来讨论一下。

一、从必须要包括的逻辑门角度来看

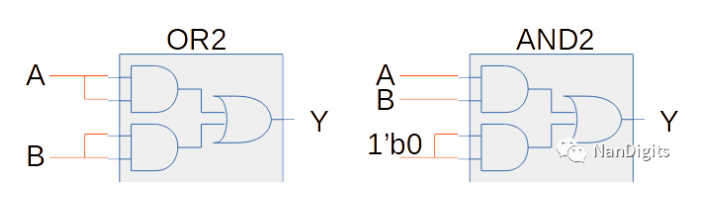

我们知道任何组合逻辑都可以由AND2(二输入与门)、OR2(二输入或门)、INV(反相器)三种门电路实现。那么AND2、OR2、INV就必须都要包括在后端的sparecell列表里。

AND2OR2INV

二、再加一些常用的CELL

有些搭电路需要与非门,可以用AND2+INV来实现。但考虑到AND2和INV可能离得稍远,不如直接插入NAND2。并且电路上AND2正是由NAND2+INV组合而来,所以同样驱动能力的NAND2的面积小于AND2,当然更小于AND2+INV的组合。

同理,为了简化搭逻辑的复杂度,我们就需要再加入NOR2、XOR2、MUX2等。

关于MUX2,可以再进一步讨论一下。我们知道在做综合时,DC几乎不用选择器来实现,更多的是用AO、AOI这种。如下图,MUX与AO是可以等价变换。

并且,我们可以看出,AO可以更直观地变换成AND2和OR2。如下图:

NAND2NOR2XOR2MUX2AO

三、时序DFF、LATCH

经常遇到ECO要打拍,或者是加寄存器,所以我们提前撒一些DFF也是必要的。但数量不需要太多,根据具体设计的情况来定。

这里有个建议,可以选DFF功能最全的类型,就是同时带SET和RESET,且同时带Q和QC的。时钟边沿选上升沿触发的,因为大部分情况下需要上升沿。如果偶尔需要下降沿,可以在时钟端加一个INV。

LATCH呢,可加可不加,不是必须的。ECO时一定需要LATCH的情况并不多。

DFF_R_S_Q_QCLATCH

四、集成门控时钟ICG

最近遇到一个需求,需要ECO来插入门控时钟,降低功耗。如果sparecell list里没有提前放置ICG将会比较麻烦。

一种可能的方法是把综合自动插入ICG挪来用用。但综合时一般是多bit一起插一个ICG,要挪出来的话,就需要把多个DFF的D端全部加MUX。而sparecell list里的MUX一般也不会太多,所以这种方法能不能实现就看运气了。

所以,能提前放置几个ICG是有必要的。

ICG五、考虑max tran、max cap、长线、setup、hold等DRC和时序的优化

一般逻辑sparecell不要选最小的驱动能力,可以用X2的。毕竟ECO时,sparecell离得有点远,附近不会刚好就有需要的类型。

另外,还需要加入一些大驱动的INVX4、INVX6、BUFX4、BUFX6、BUFX12来优化时序。

插少量的DELAY cell也是很多帮助的,常常用来修改hold,或者做一些特别的延时。

INVX4INVX6BUFX4BUFX6BUFX12

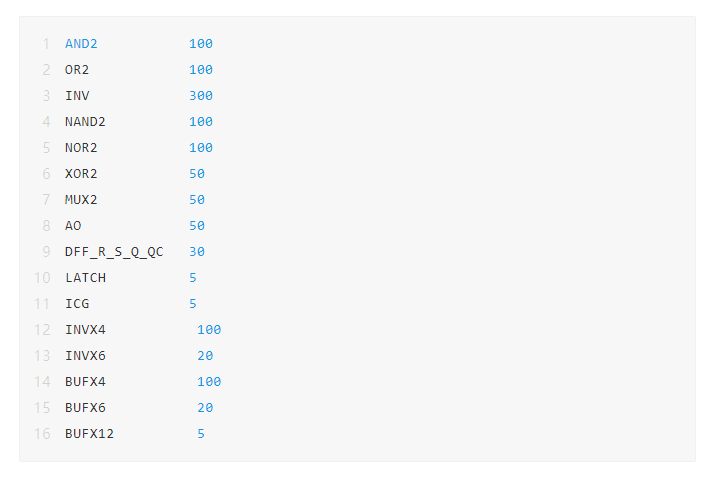

六、各种sparecell的比例

上面提到这些sparecell的比例也是有讲究的。一般情况下,可以从综合结果里提取各种cell的比例。

也可以根据以往的经验,或者设计的特点来调整。尤其是可以大概估一估DFF可能的个数。

我这里也给一个参考:

七、sparecell总面积占整个digital的面积比例

这个通常来说与设计的成熟度有关。对于第一版,肯定要多加一些,比如sparecell占整个数字面积的8~10%。第二版可以少加一些,4~5%。第三版可以只加3%。

如果项目中大部分是买的IP,集成起来做soc,可以比例稍低一些。

浙公网安备 33010602011771号

浙公网安备 33010602011771号