PL中断PS

新建工程:

首先在ZYNQ芯片里添加自己需要使用的模块和PL端中断,一共有16个PL端的IRQ中断供我们添加。

这里介绍一下ARM 中的基本中断类型,包括软件中断(SGI)、 CPU 私有外设中断(PPI)以及共享外设中断(SPI)。区别在于私有外设中断和共享外设中断中含有 PL 侧引入的中断。

arm总共有7种中断模式,最常见的两种是FIQ(Fast Interrupt Request )和IRQ(Interrupt Request),ARM为了支持这两种不同的中断,提供了对应的叫做FIQ和IRQ处理器模式。FIQ具有更高的优先级。

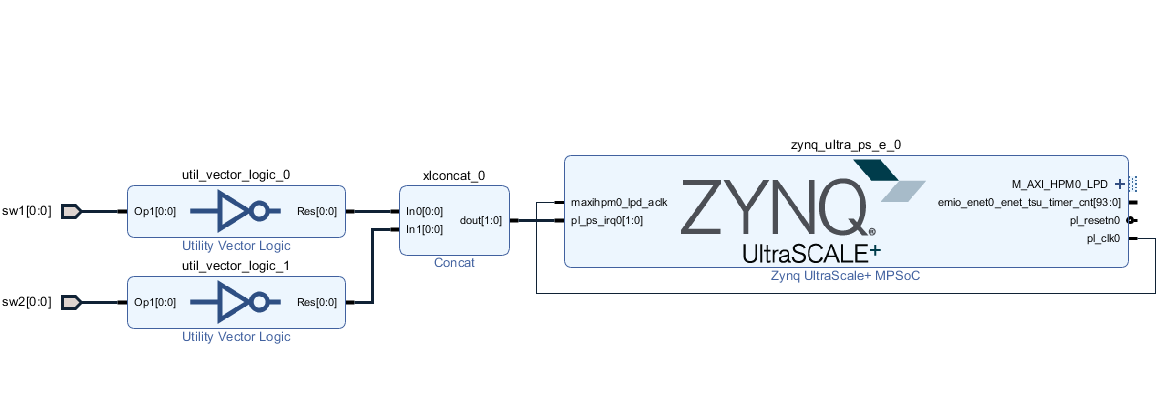

ZYNQ配置好后,单击添加 IP 按钮,添加两个逻辑门(vector)和一个连接(concat) IP。因为我们使用的按键是一位的所以把逻辑门也配置成一位的并把输入make external连接到按键,把cooncat也配置成对应的位宽和输入输出个数。如图所示,连接好整体电路。可以右键点击Regenerate layout让布局变得好看一点。点击上方的√可以校验连接有没有错误,最后记得检查每个端口的位宽是否正确。

如果是在之前的工程上修改,先右键单击 Block 文件,reset output products,然后再右键单击 Block 文件,Generate the Output Products,选择Global,Generate。

右键单击 Block 文件, Create a HDL wrapper(生成 HDL 顶层文件),勾选Let vivado manager wrapper and auto-update(自动更新)

因为我们定义了两个按键,所以要添加管脚约束文件,约束文件的模板可以在左边操作栏的Language templates中查看。

在导入SDK前,如果我们的project是复制原来的工程,需要把project文件中的sdk文件删掉再导入。

浙公网安备 33010602011771号

浙公网安备 33010602011771号