UVM寄存器模型

1.创建流程

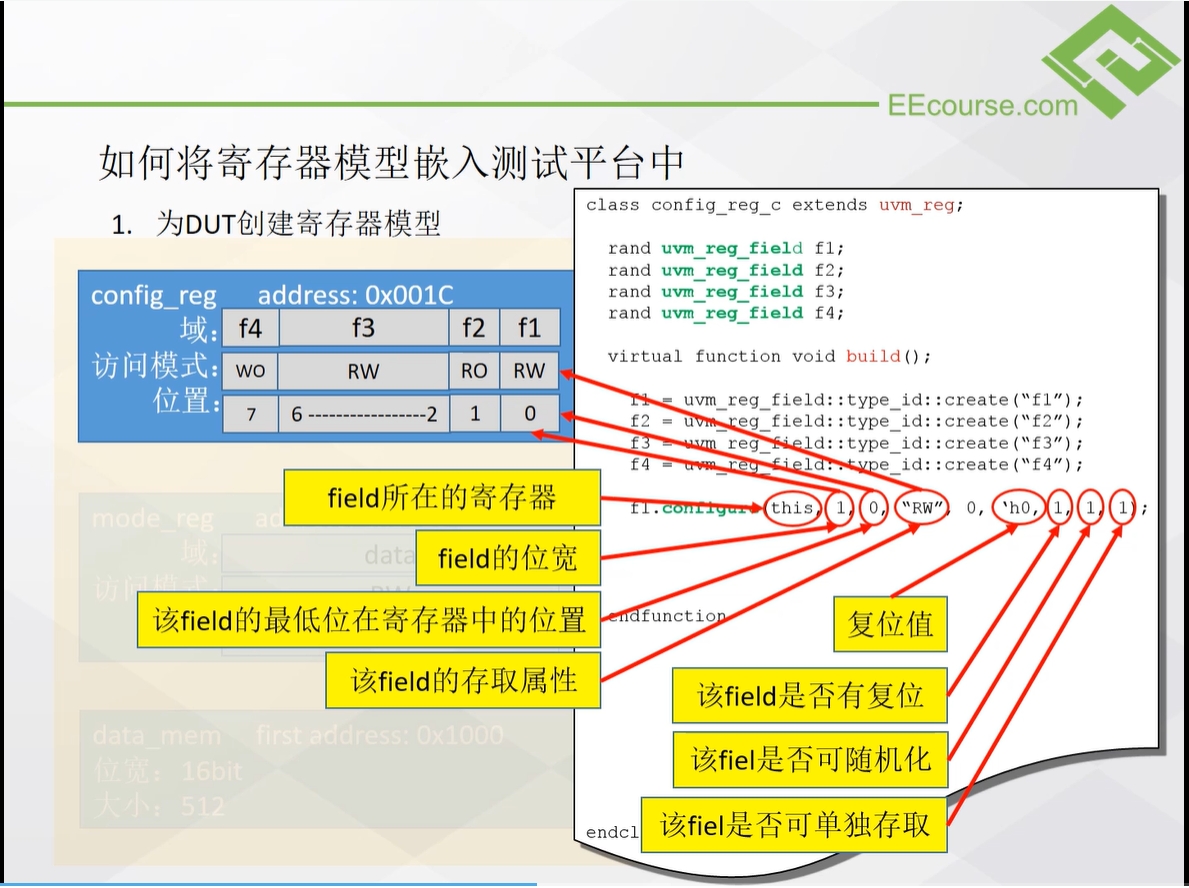

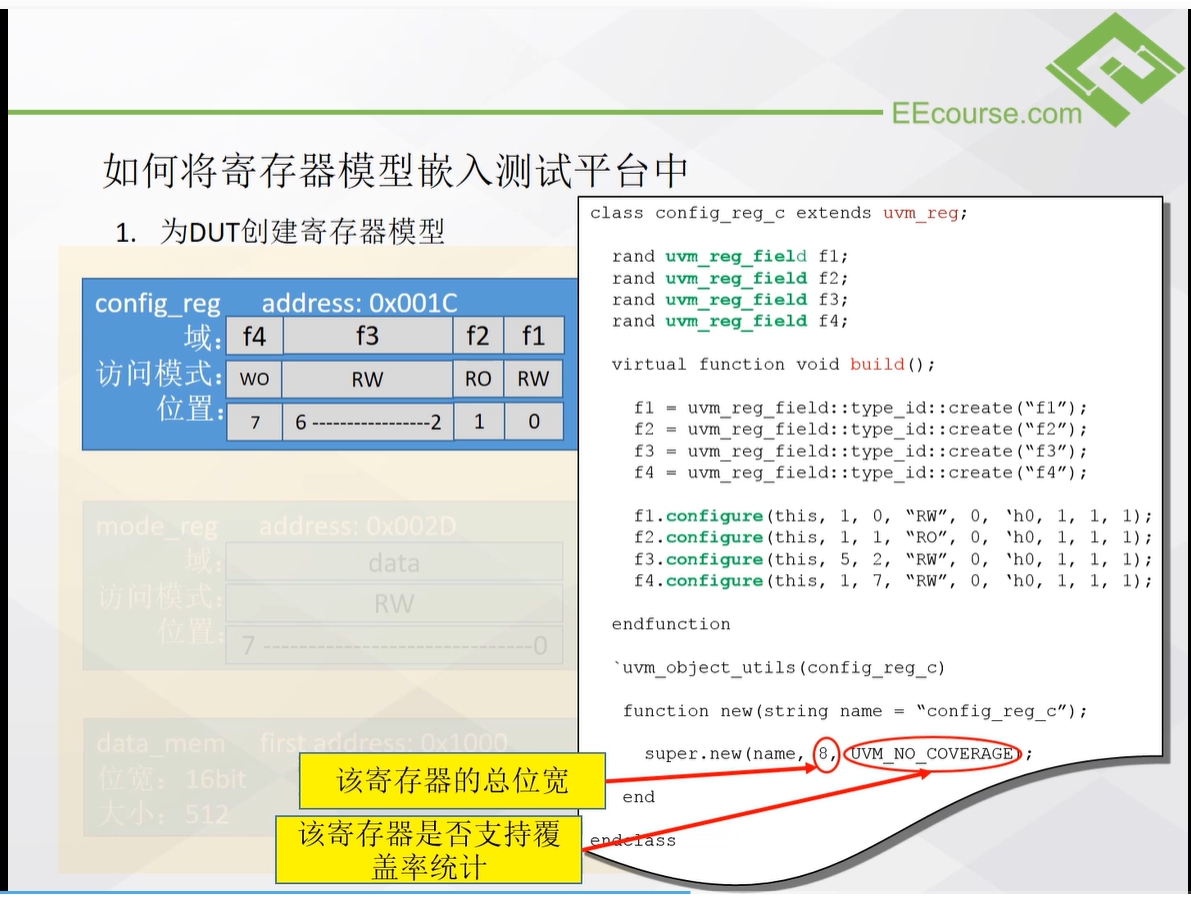

2.创建一个寄存器基类要extends uvm_reg,然后创建寄存器的域

3.调用`uvm_object_utils()注册基类

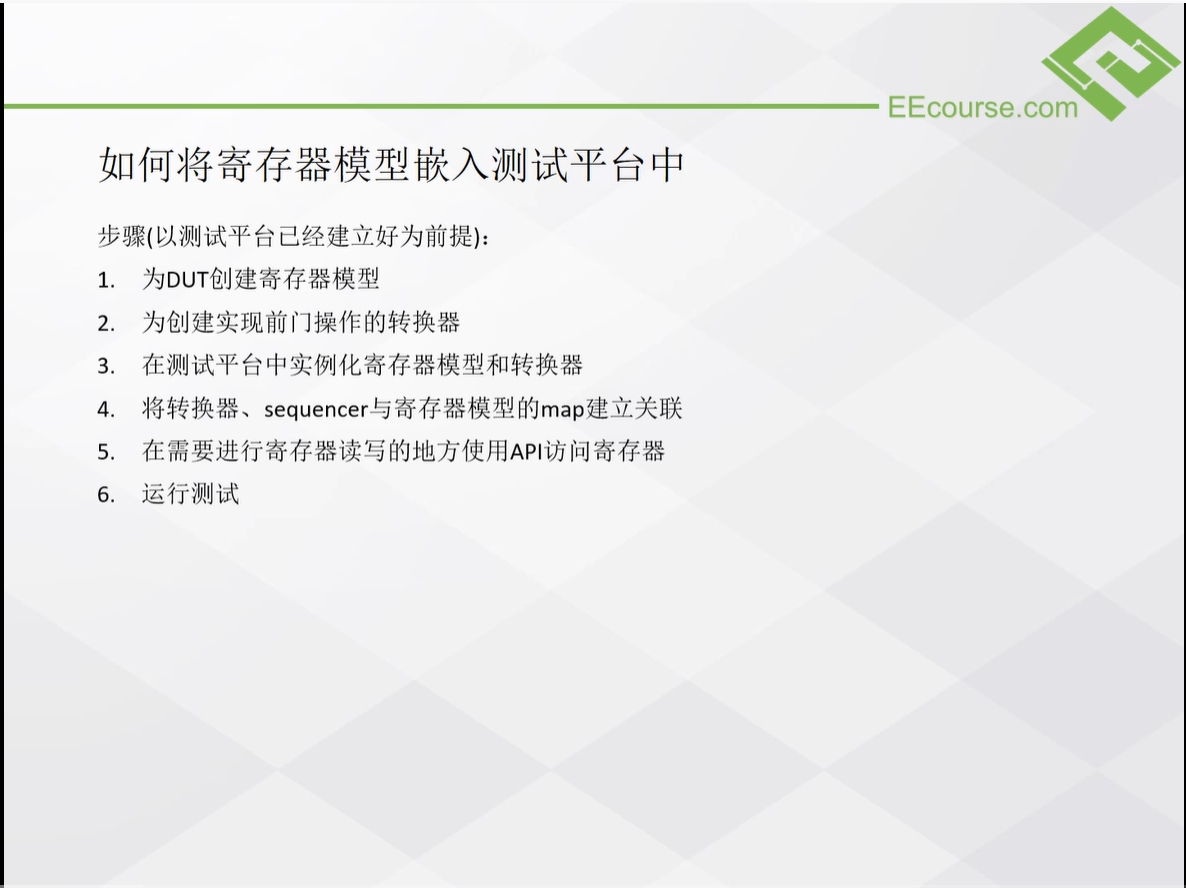

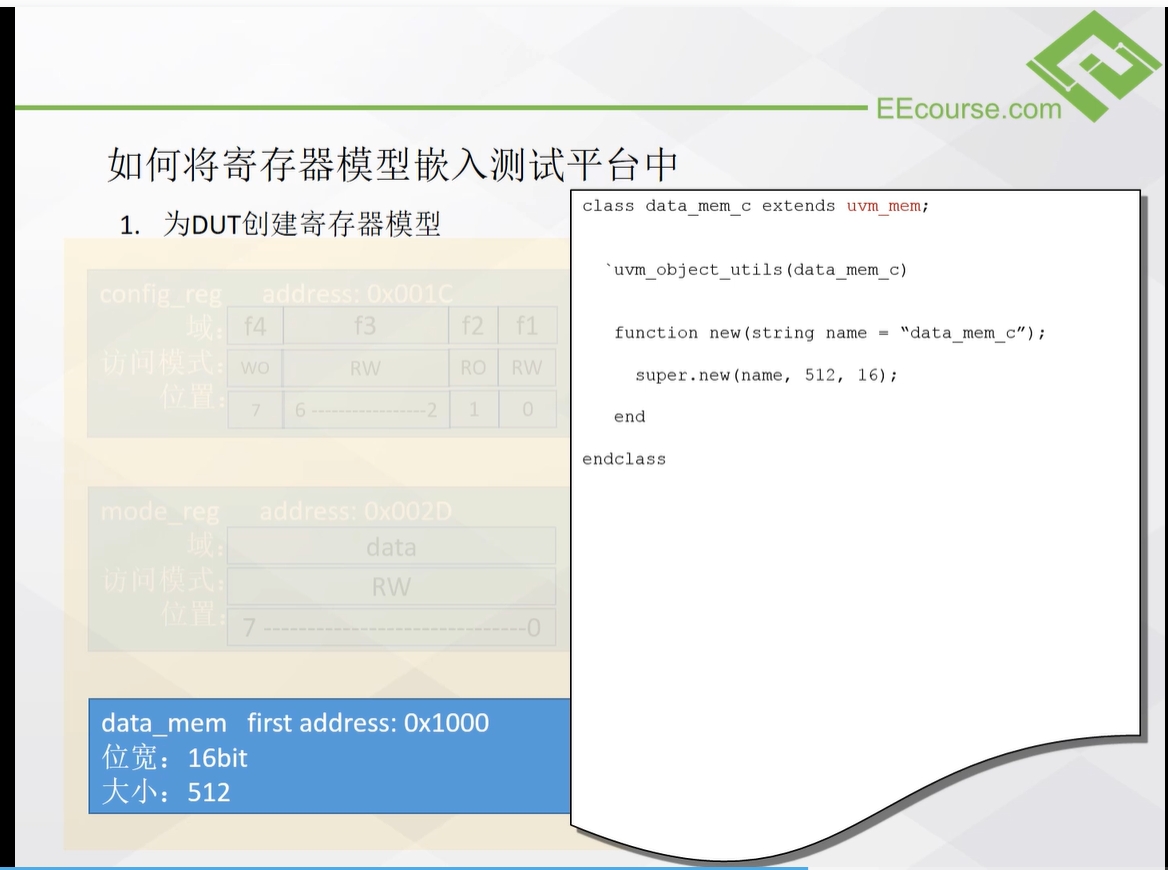

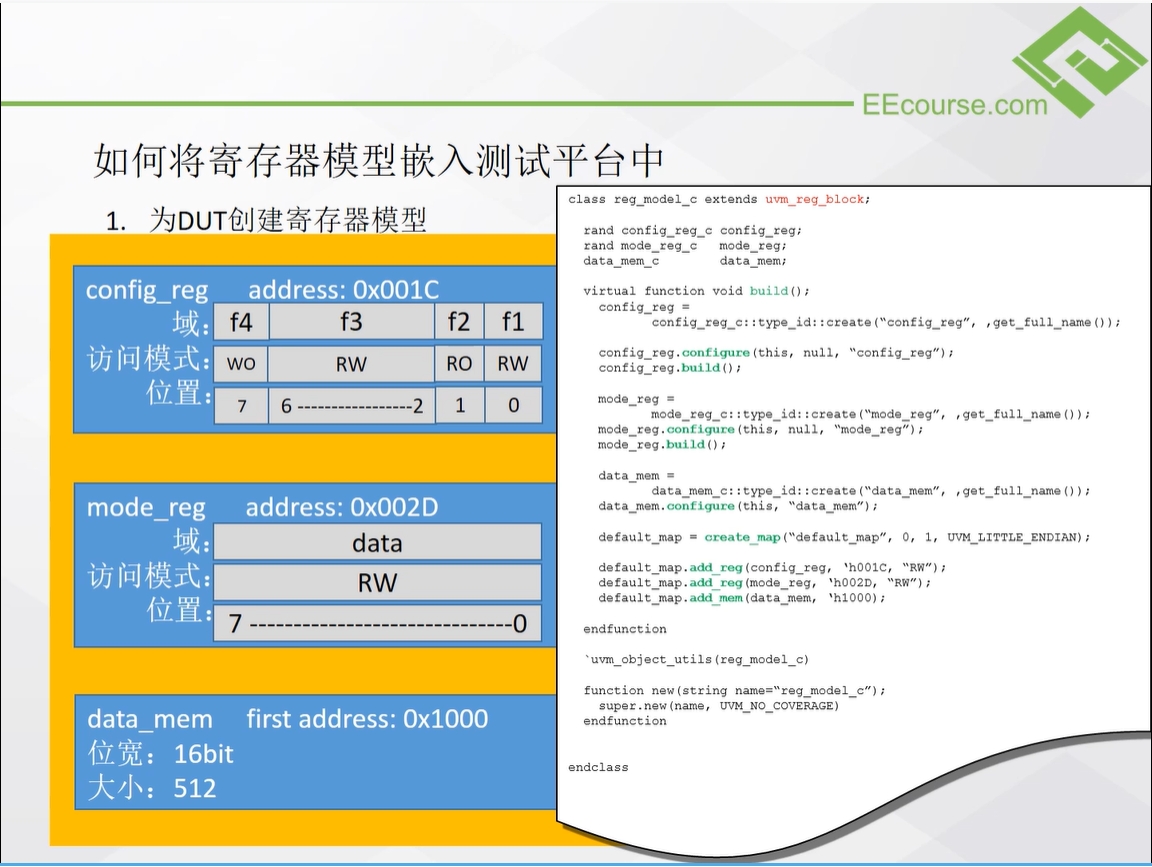

4.创建DUT存储器模型

5.封装到一起组成一整个寄存器

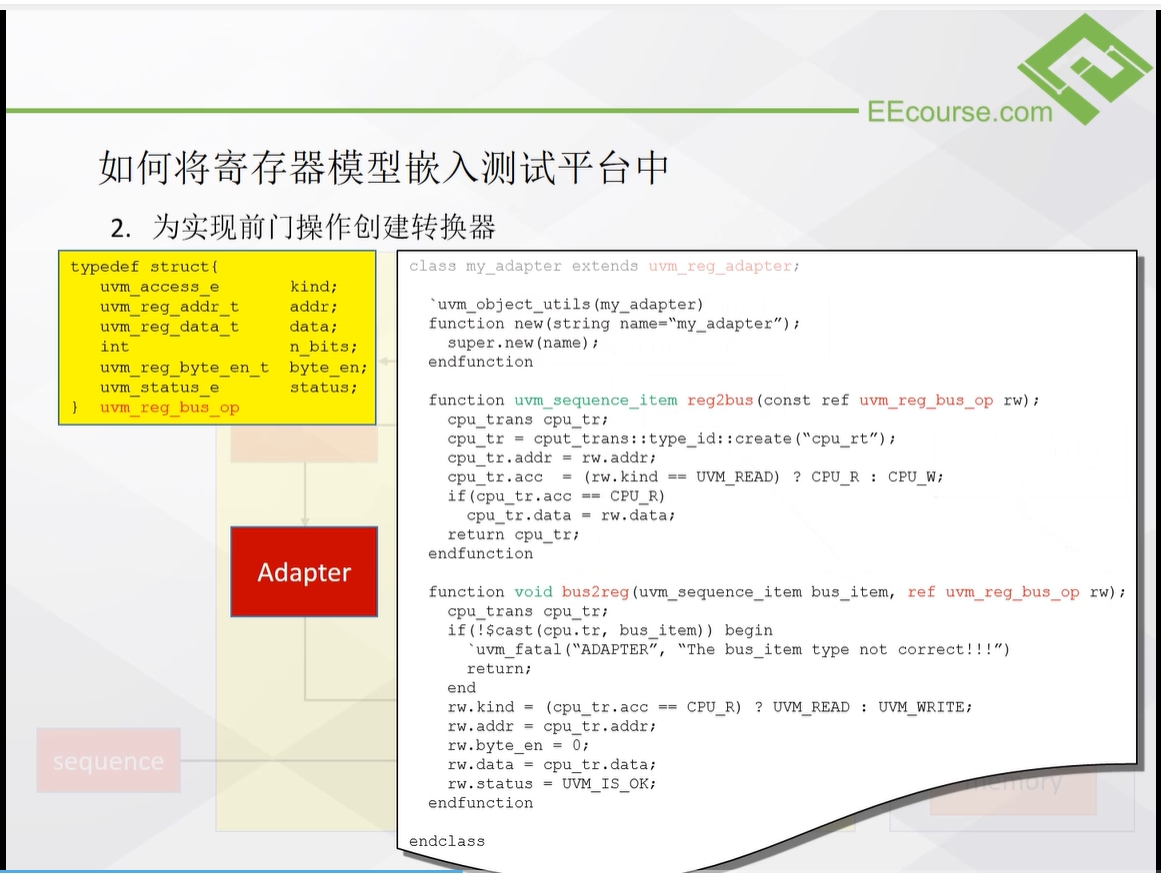

6.为实现前门操作创建转换器

uvm_sequence_item reg2bus可以返回一个sequence_item数据类型,可以将寄存器类型的事务转换为sequencer可以接受的事务

bus2reg转化过程相反,将总线上的事务转换为寄存器类型的事务

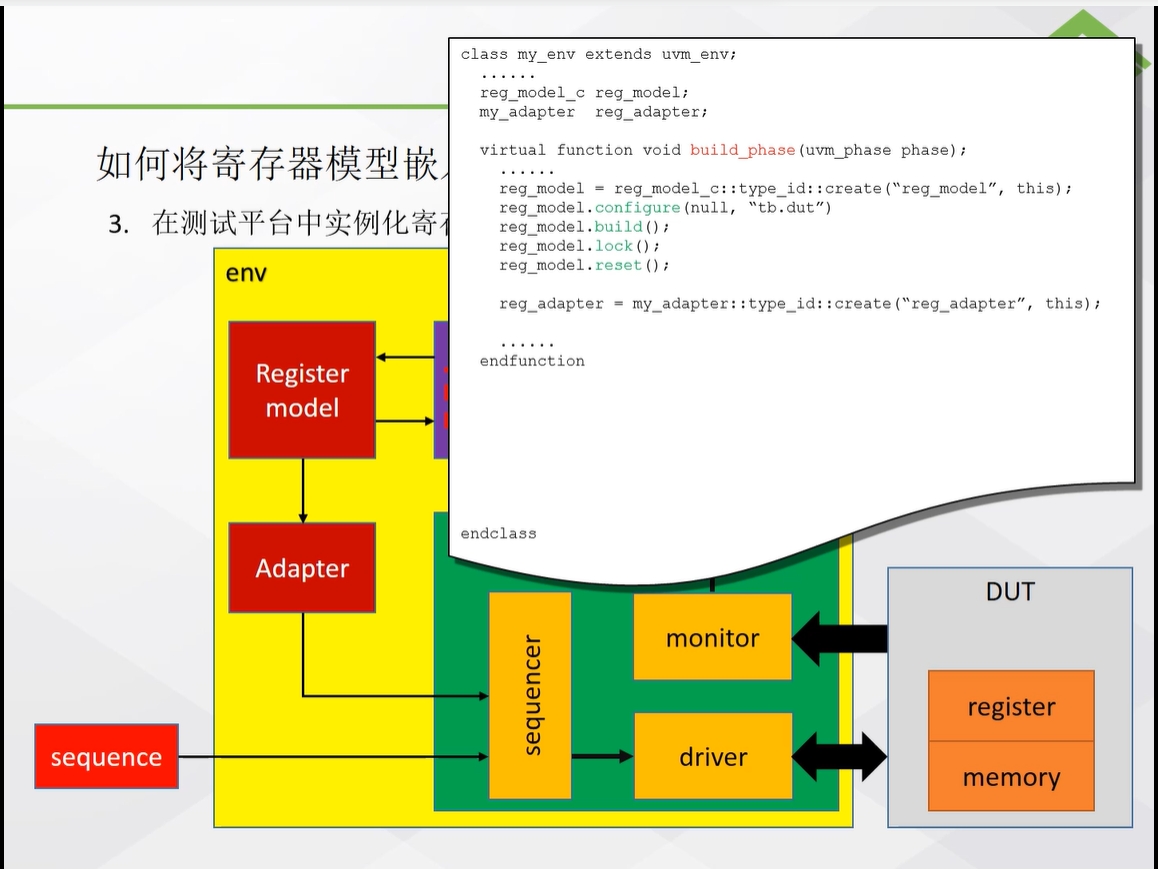

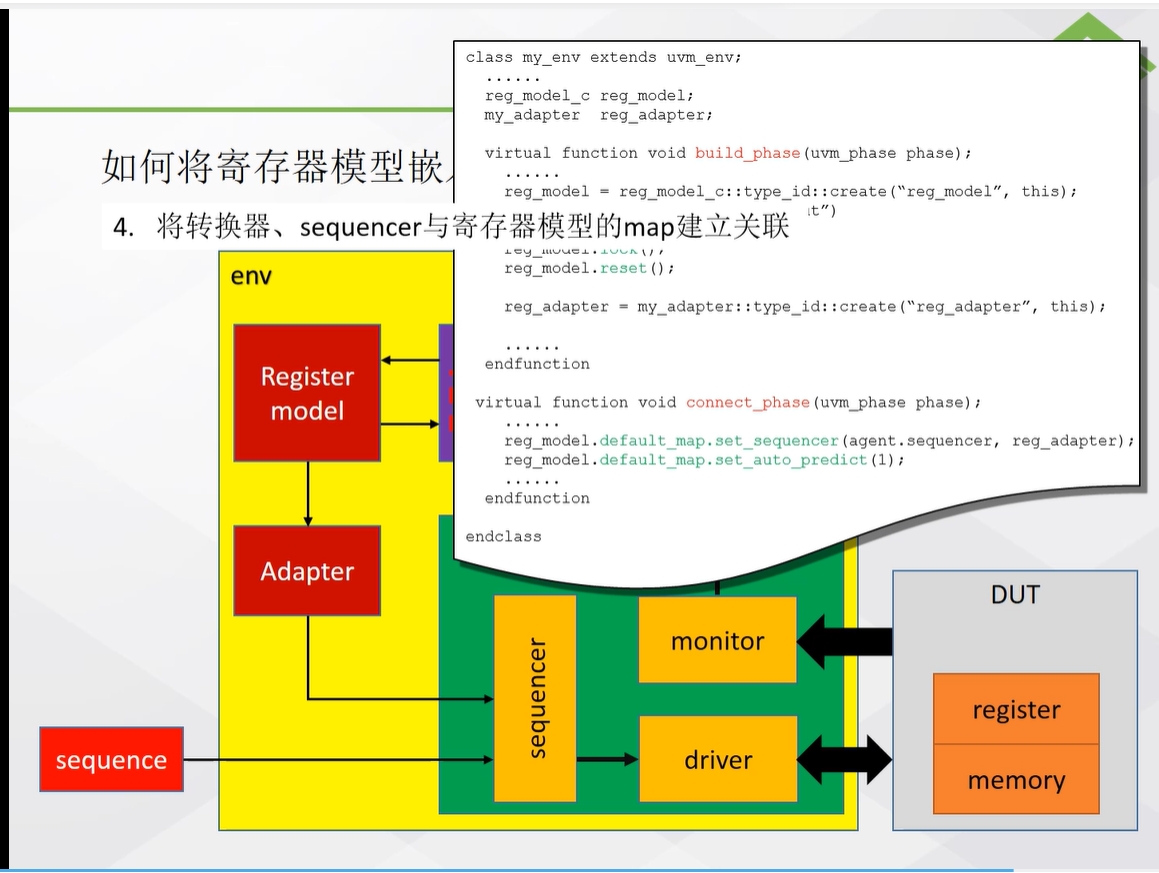

7.在env中声明寄存器和转换器的句柄,在build里实例化寄存器模型,调用lock锁用寄存器模型

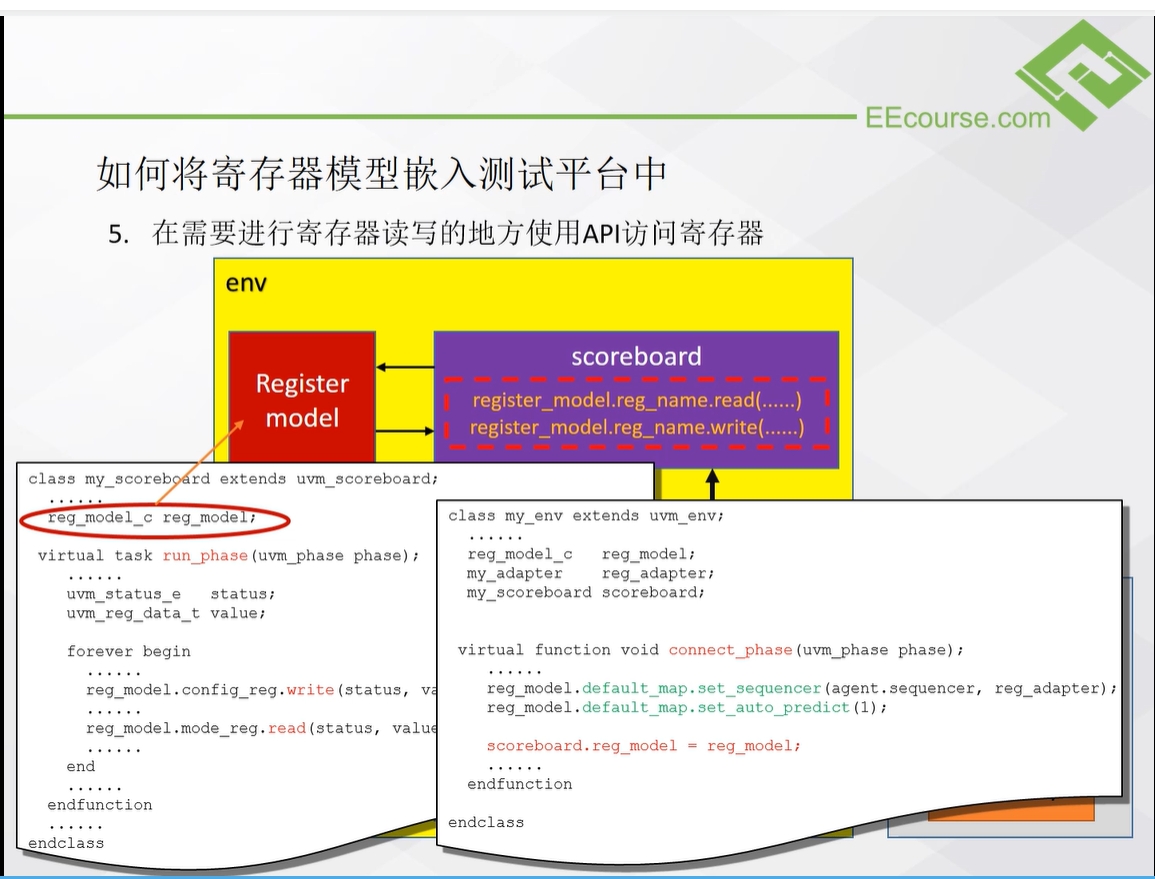

8.在scoreboard中进行访问,使用API访问寄存器,在sb中例化寄存器,在env中对寄存器赋值

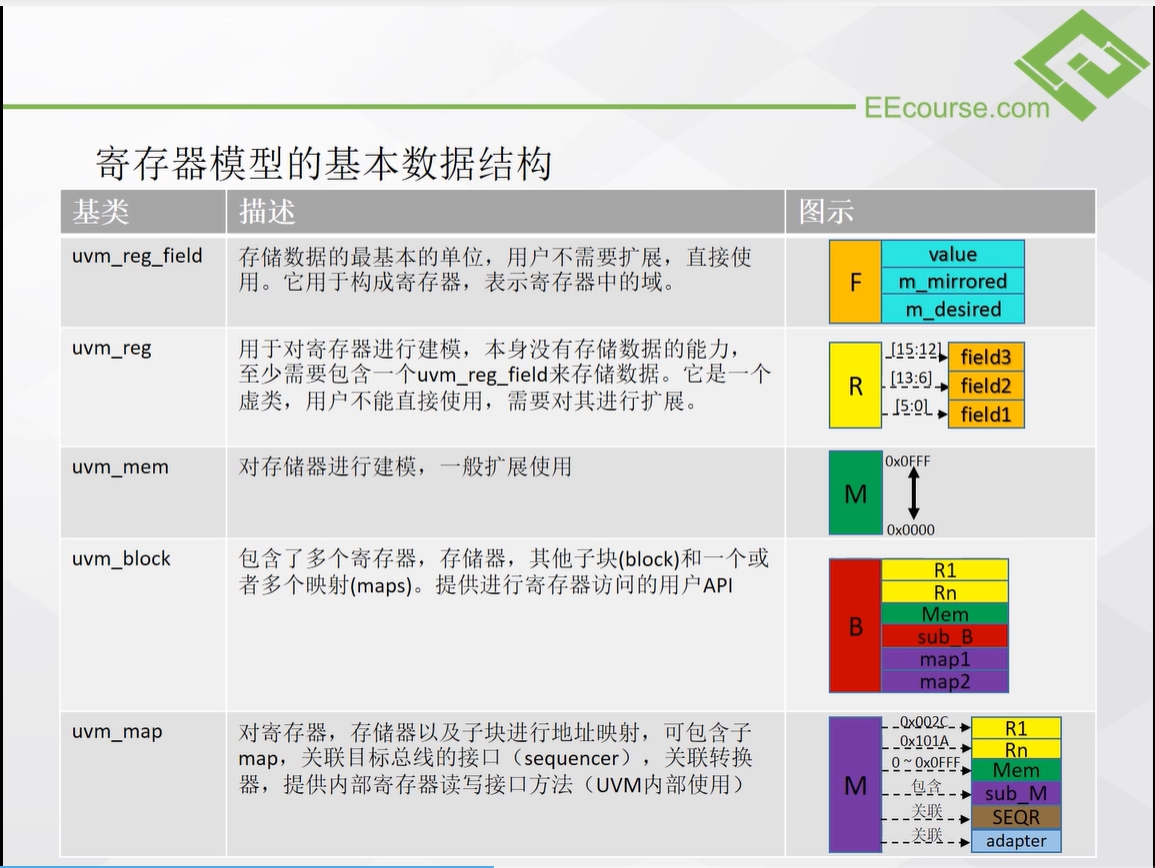

寄存器模型的基本数据结构

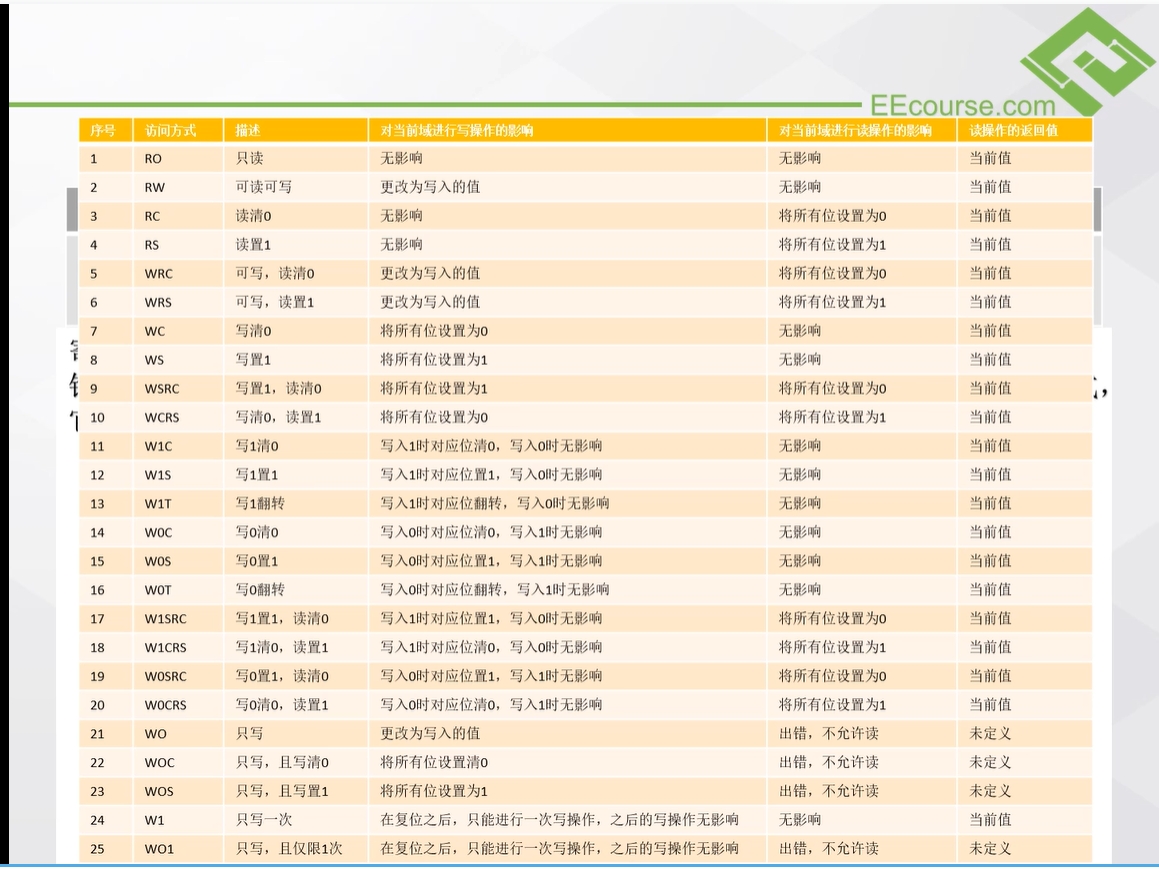

访问模式仅供参考

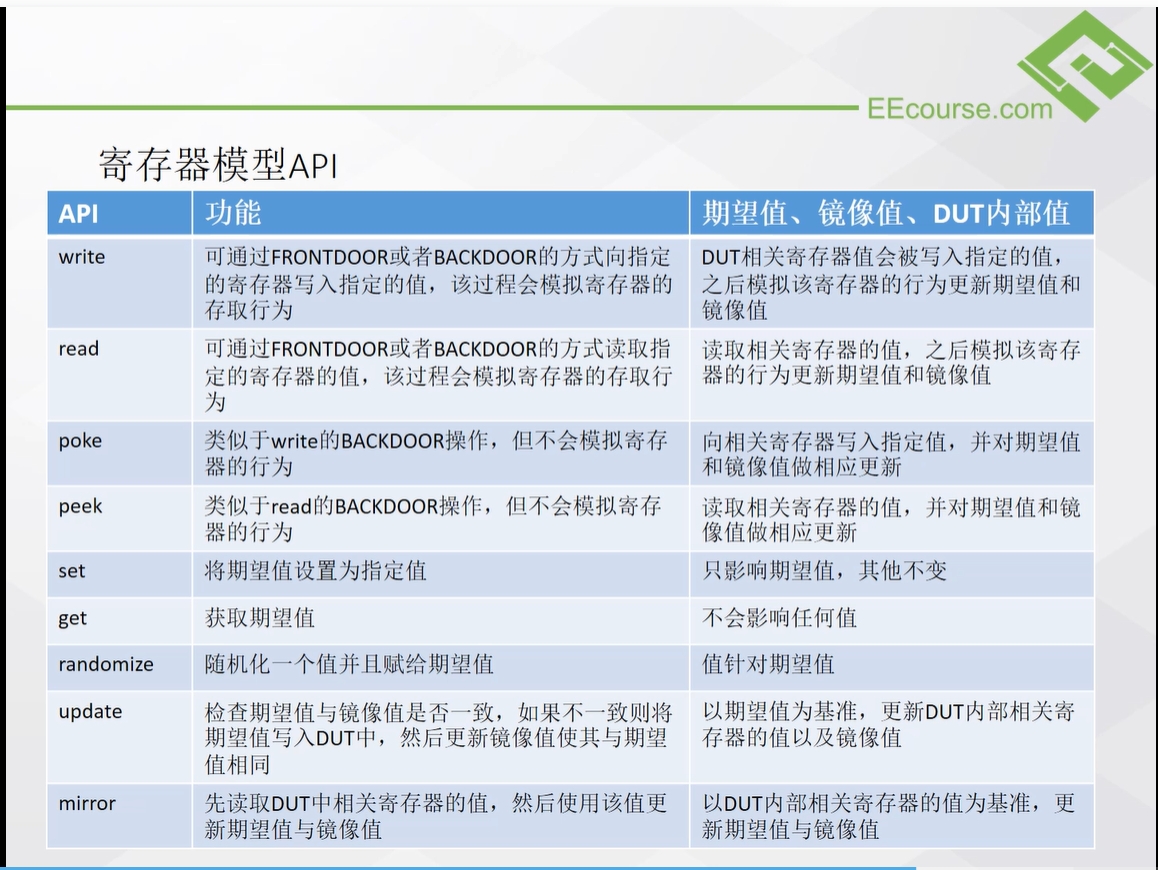

寄存器模型API

1.write&read

2.peek&poke(back door模式)peek/poke不会模拟寄存器的行文而是直接操作(与write/read区别)

3.randomize&updata&mirror

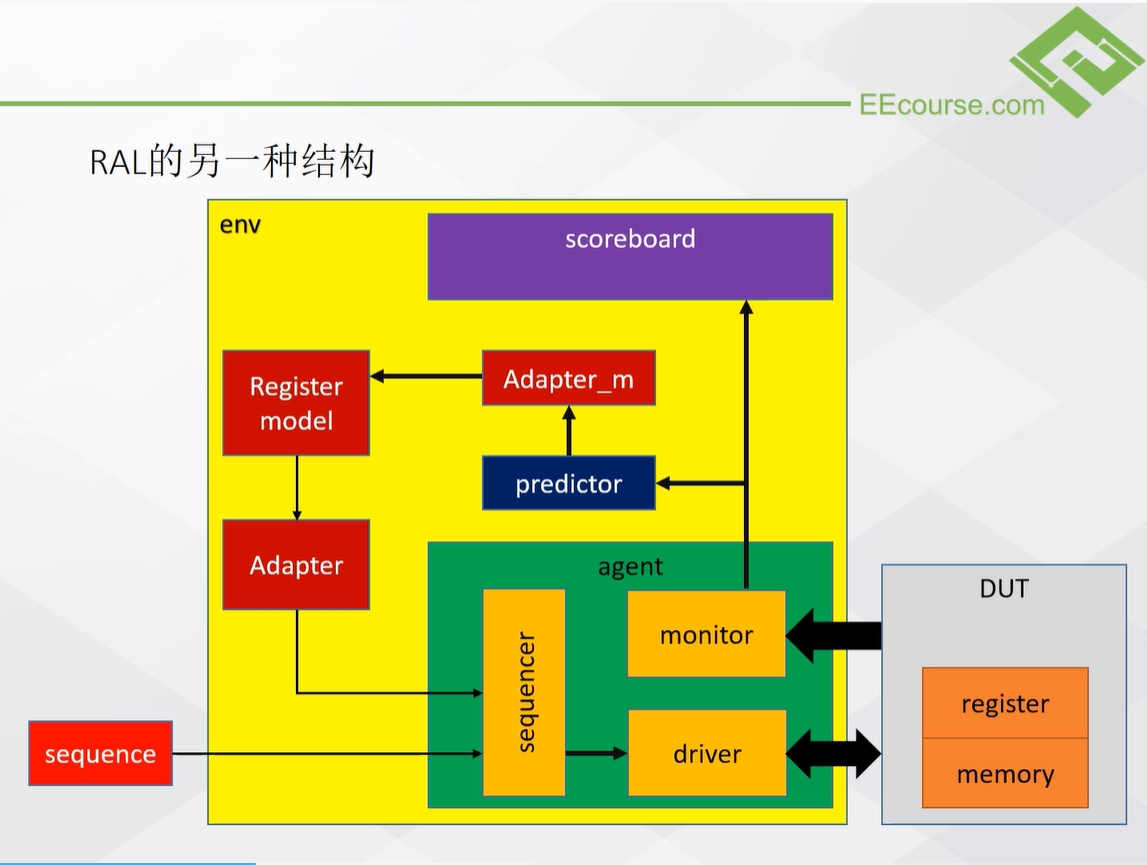

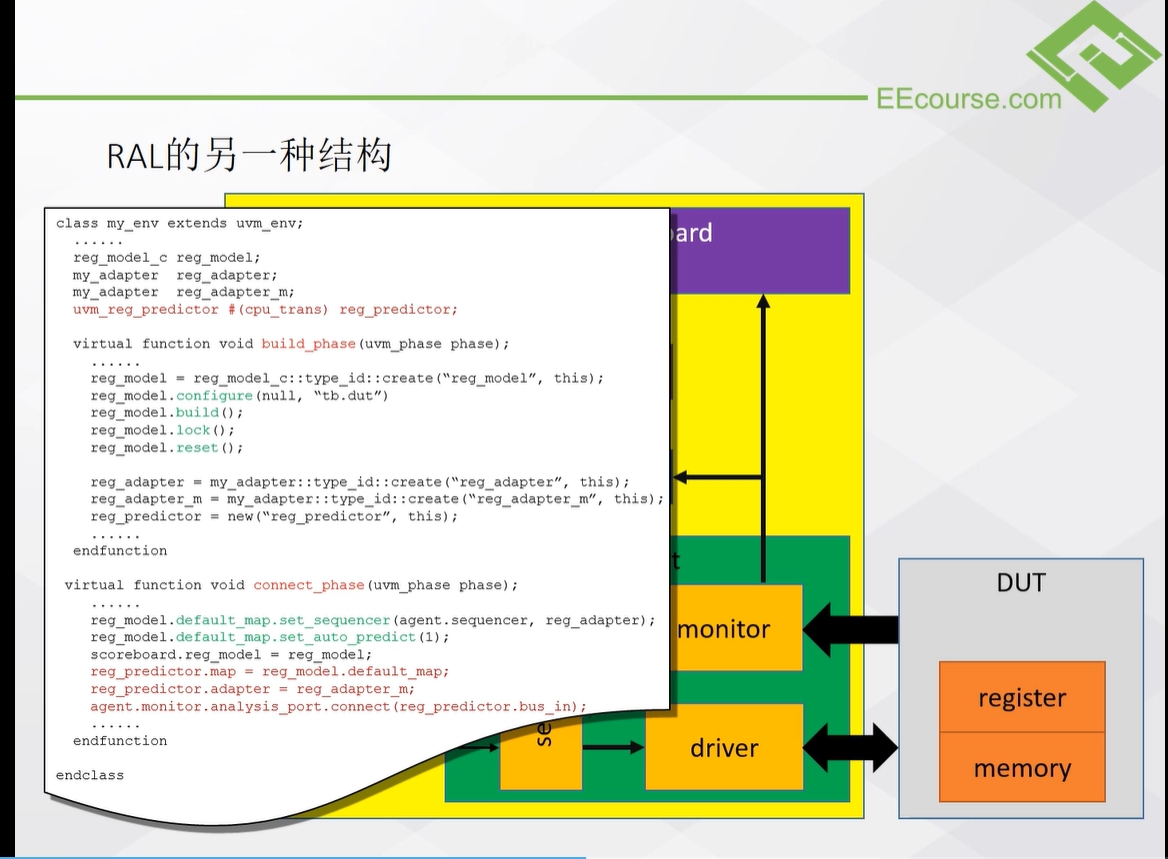

寄存器模型的另一种结构

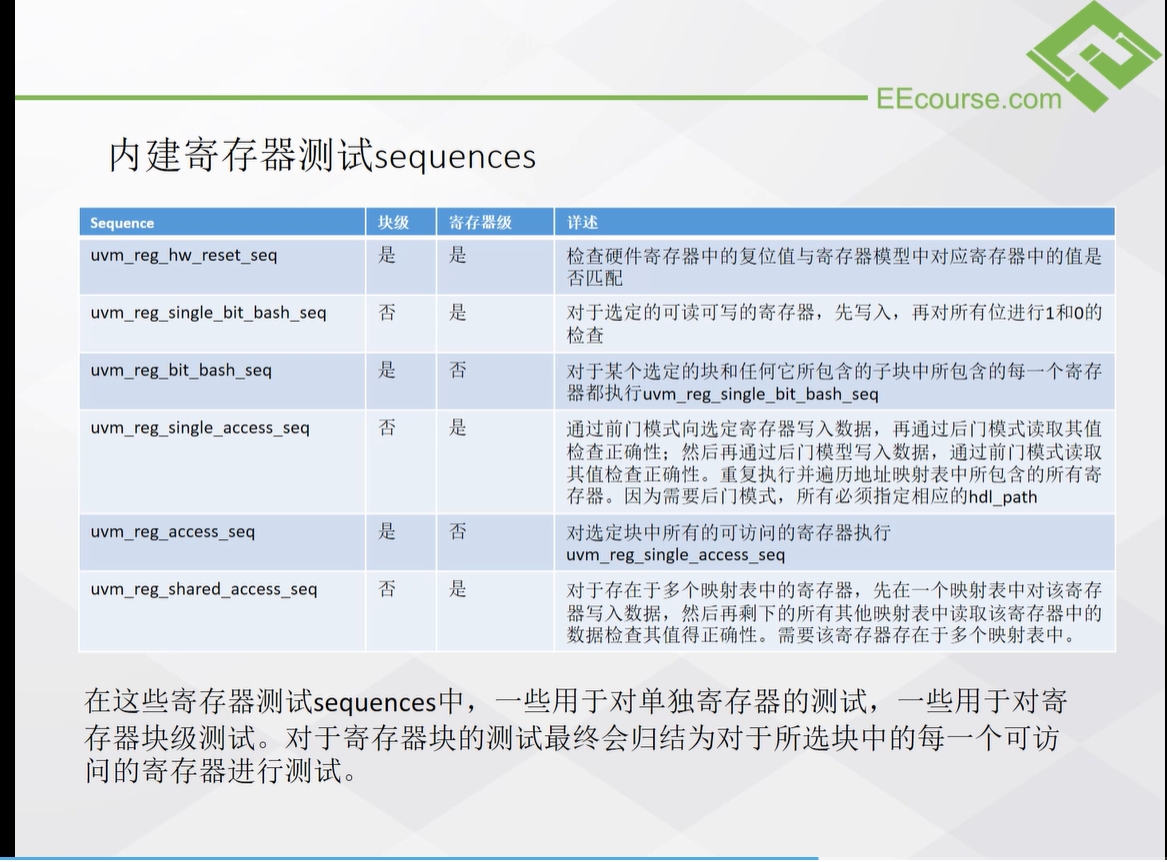

内建寄存器测试sequences

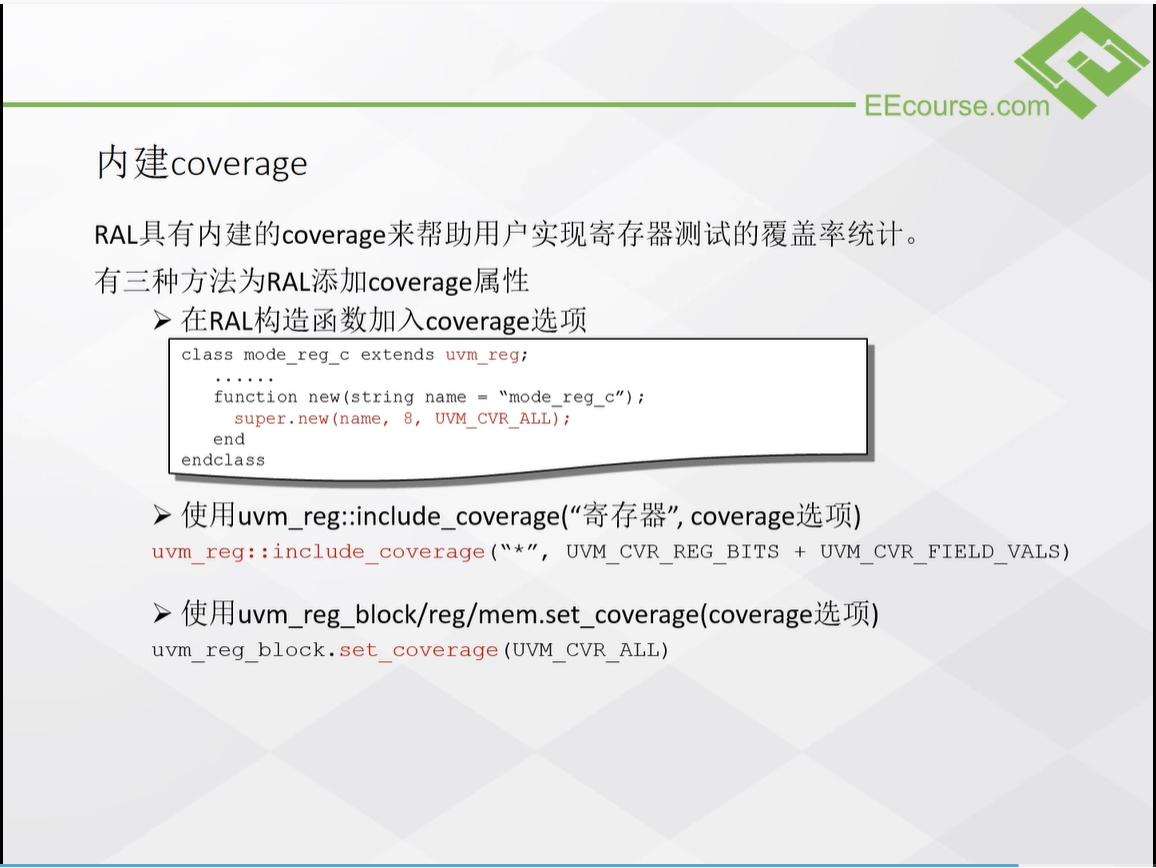

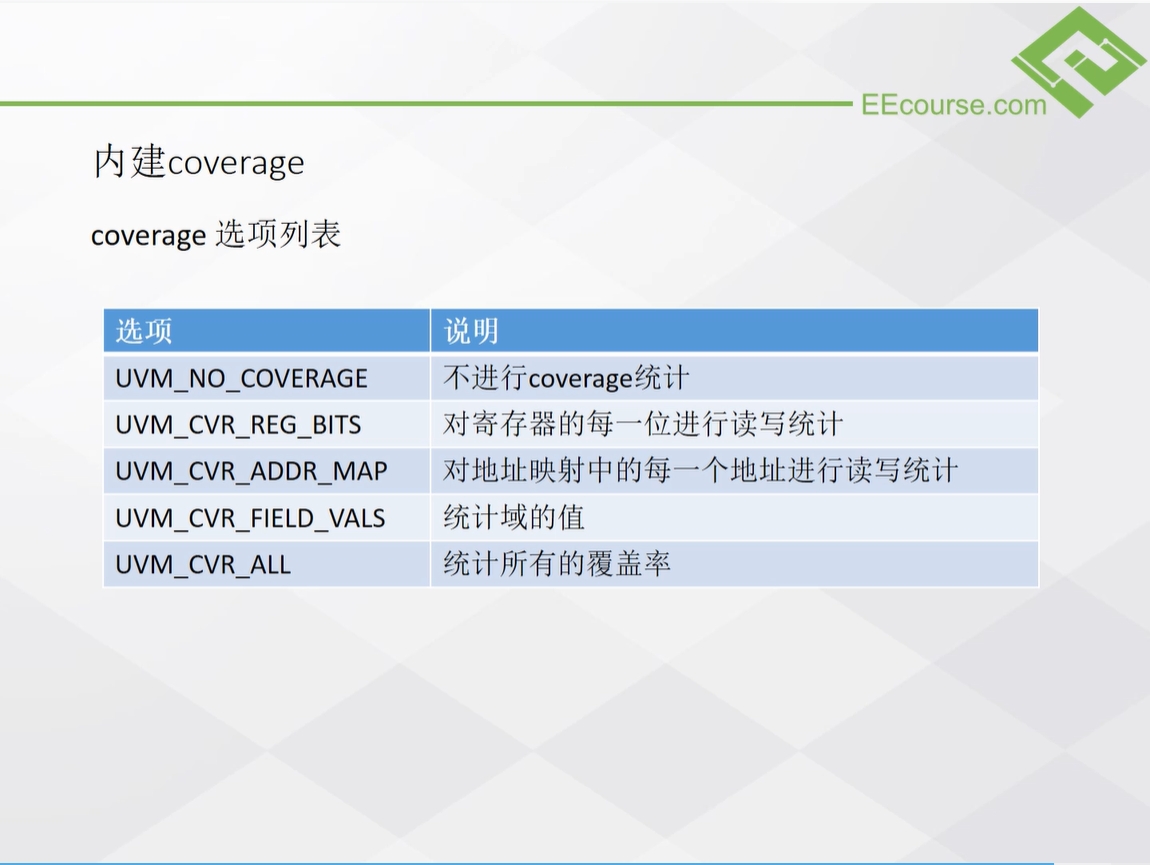

内建coverage

1.什么是UVM RAL

2.RAL的工作原理

3.如何构建寄存器模型

4.如何将寄存器模型嵌入测试平台中

5.使用寄存器模型进行API访问

浙公网安备 33010602011771号

浙公网安备 33010602011771号