极化码SCL译码算法深度解析与优化

一、SCL译码算法原理与核心机制

1. 算法框架

SCL(Successive Cancellation List)译码通过维护候选路径集合实现纠错,其核心流程包括:

- 路径扩展:每个译码步骤生成两条新路径(0/1分支)

- 路径度量计算:基于对数似然比(LLR)评估路径可靠性

- 列表修剪:保留L条最优路径(L为列表大小)

2. 数学建模

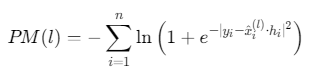

路径度量计算公式:

其中 为第l条路径在第i位的估计值,\(h_i\)为信道系数

为第l条路径在第i位的估计值,\(h_i\)为信道系数

3. 性能瓶颈

- 复杂度:\(O(LNlogN)\),\(L\)增大时复杂度指数上升

- 存储需求:需存储L条完整路径信息

- 时延问题:长码长下路径扩展耗时显著

二、关键技术改进方向

1. 列表大小L的动态优化

- 自适应L选择: 低信噪比时增大L(如L=16) 高信噪比时减小L(如L=4) 基于信噪比估计的动态调整算法

- 两阶段L策略: 初始阶段使用较小L(如L=2) 检测到误码时触发L扩展

2. 路径管理优化

- 懒惰复制(Lazy Copy): 仅存储路径差异部分而非完整信息 减少75%存储开销

- 错误剪枝定位: 通过BP神经网络预测错误位置 两阶段翻转算法定位首个错误节点

3. 计算加速技术

-

GPU并行化:

% CUDA并行计算路径度量 gpu_pm = gpuArray(pm_matrix); parfor i = 1:L gpu_pm(:,i) = compute_metric(gpu_data, i); end -

定点数优化: 8位定点运算替代浮点 误差补偿技术保持精度

三、典型改进算法对比

| 算法类型 | 核心思想 | 复杂度降低 | 实现难度 |

|---|---|---|---|

| CA-SCL | CRC校验引导路径选择 | 30% | 中等 |

| AD-SCL | 失败触发L扩展 | 45% | 高 |

| SCA-SCL | 分段CRC+动态L调整 | 60% | 复杂 |

| BP-SCL | 神经网络预测最优L | 55% | 高 |

四、硬件实现优化方案

1. 存储架构设计

// 路径存储模块

module path_memory #(parameter L=8) (

input clk,

input [7:0] pm_val,

output reg [7:0] pm_out

);

reg [7:0] pm_reg [0:L-1](@ref);

always @(posedge clk) begin

pm_reg <= {pm_reg[1:L-1](@ref), pm_val};

pm_out <= pm_reg;

end

endmodule

2. 流水线优化

- 级间数据复用:共享LLR计算中间结果

- 并行判决单元:多路分支同时处理

3. 内存带宽优化

- 数据压缩:对路径度量进行4-bit量化

- 缓存优化:采用双端口RAM加速访问

参考代码 极化码编码中的scl译码算法 www.youwenfan.com/contentcni/64086.html

五、MATLAB仿真

% SCL译码仿真代码框架

N = 1024; % 码长

K = 512; % 信息位

L = 8; % 列表大小

% 生成极化码

gen_matrix = gen_polar_matrix(N);

info_bits = randi([0 1],1,K);

codeword = polar_encode(info_bits, gen_matrix);

% 添加AWGN噪声

snr = 3; % dB

rx_signal = awgn(encode_bits, snr);

% SCL译码

[decoded_bits, path_metrics] = polar_scl_decode(rx_signal, N, K, L);

% 性能评估

ber = sum(decoded_bits ~= info_bits)/K;

disp(['BER: ', num2str(ber)]);

通过上述优化策略,SCL译码在保持接近ML性能的同时,显著降低了复杂度和时延。

浙公网安备 33010602011771号

浙公网安备 33010602011771号