AD9434BCPZ-500

https://item.szlcsc.com/529326.html?lcsc_vid=QQBdVQZfE1cKAVRfTlBfBFJVQgRWVwUHQQBXXwVWQ1QxVlNTQ1RbUlRRRVJcVTsOAxUeFF5JWAIASQYPGQZABAsLWA%3D%3D

参考案例 https://oshwhub.com/jianxissss/fmc_9434

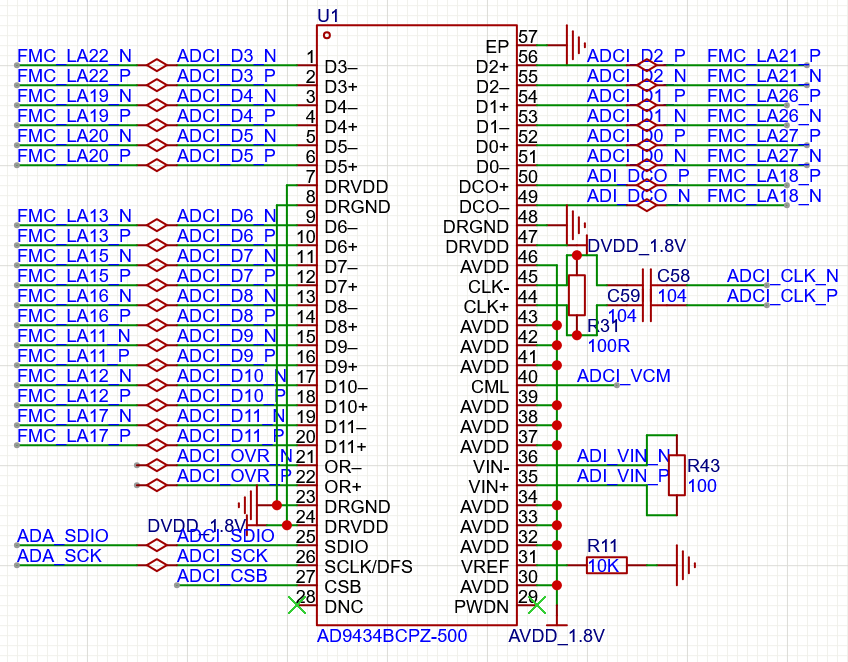

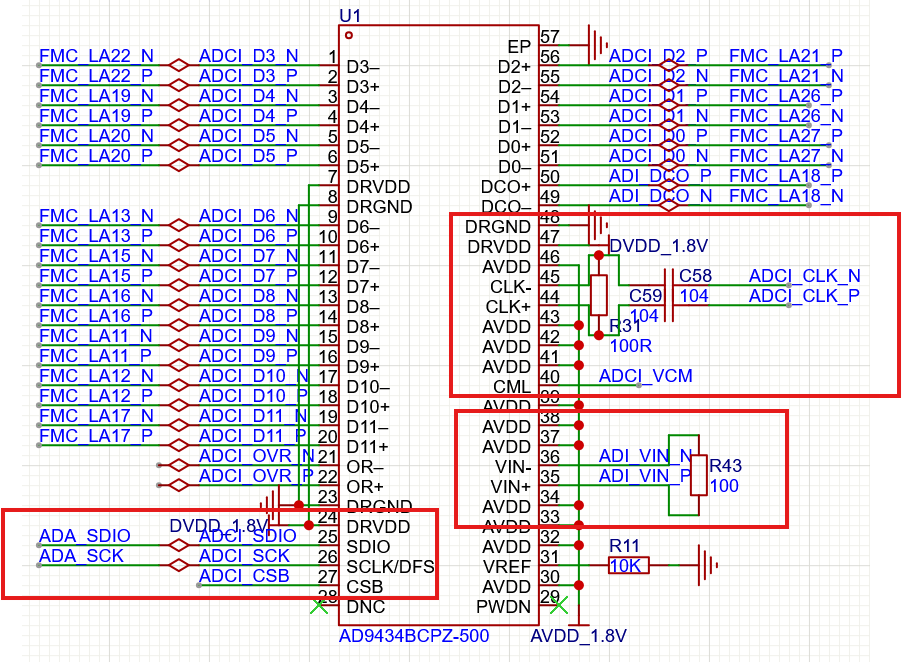

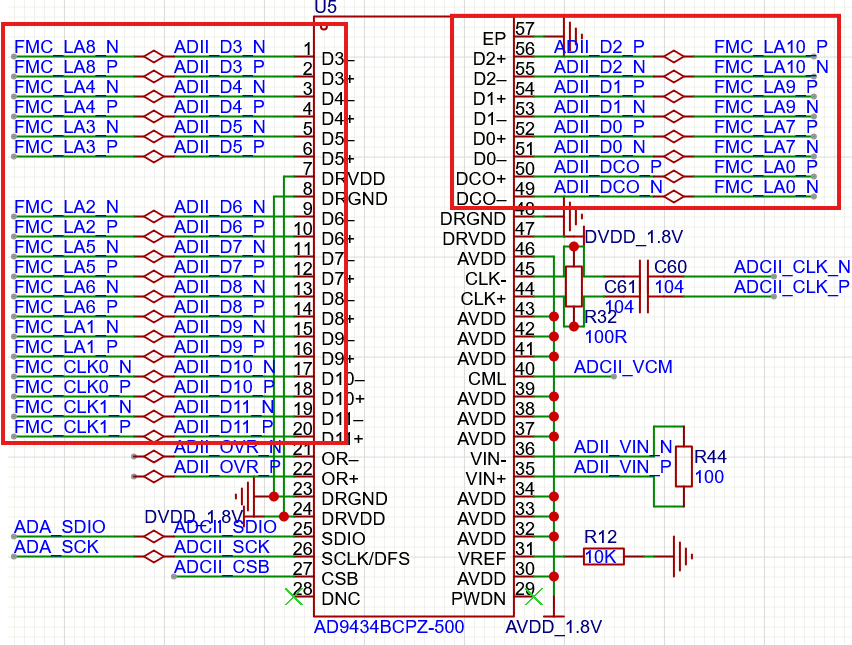

随路时钟和数据引脚随后再讲,前端比较重要的是这几组引脚。

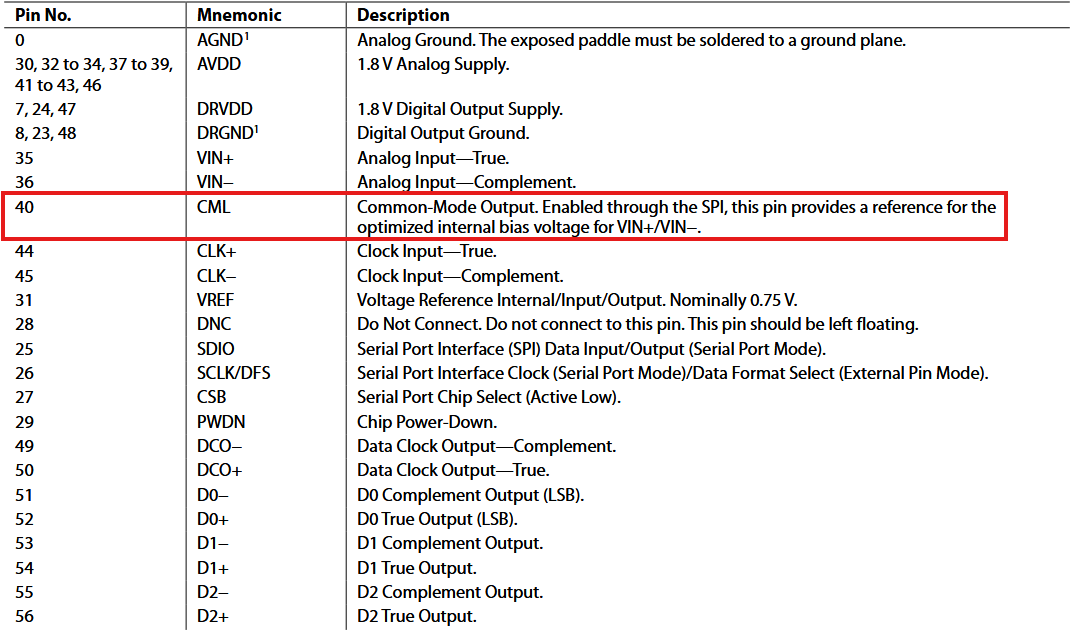

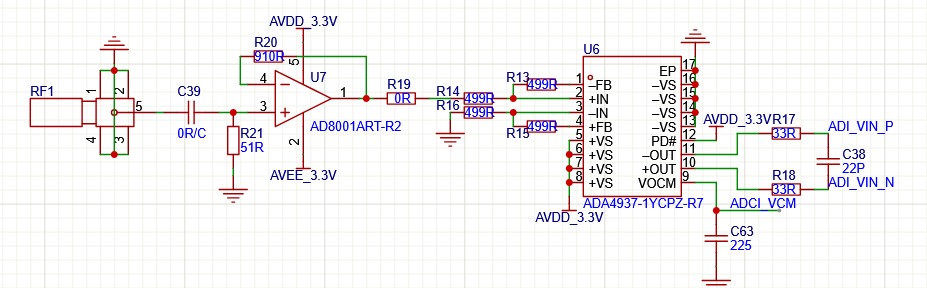

蟹老板这边采样时钟和信号输入都做了100R的阻抗处理(后面采访了蟹老板,说信号输入的100R可以不要),左边的是SPI信号引脚,用于ADC的SPI配置,40号引脚CML在说明书里这样介绍,与前端运放有关。

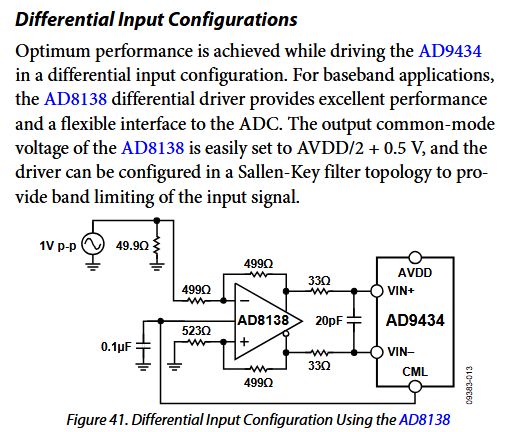

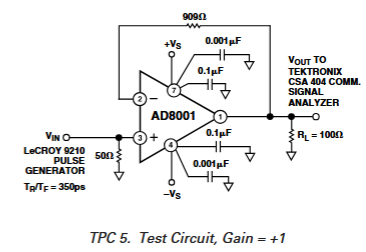

这里有一个参考前端运放电路。

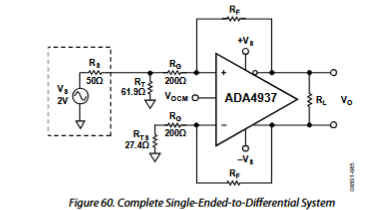

蟹老板的是这个,两个运放,第一个运放做阻抗变换,第二个是单端转差分,与说明书示例电路基本一致,不要第一个的话,需要做匹配源端和全差分的阻抗。

VOCM是共模电压,来自9434。

下面是FPGA相关,DCO是随路时钟,与采样率一致。

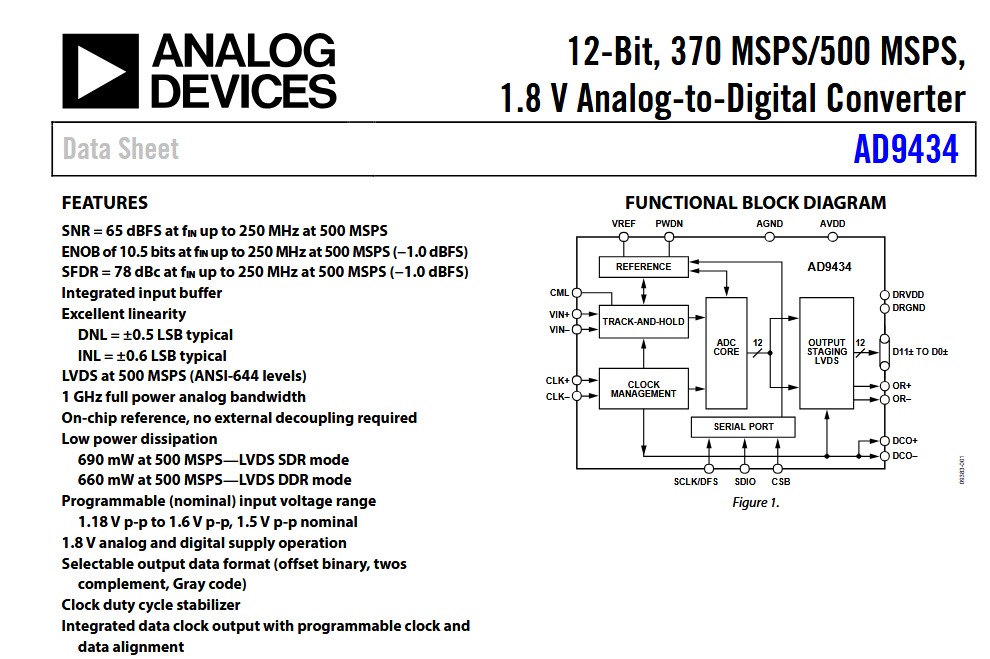

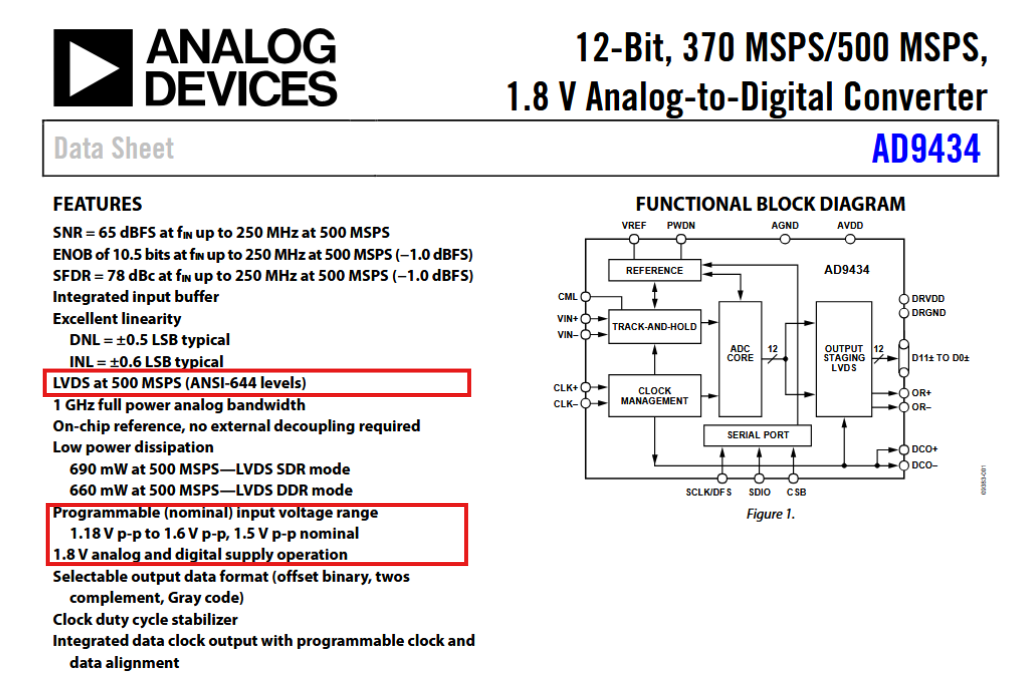

关注这几个部分,模拟/数字电源1.8V,意味着SPI电平标准1.8V,ADC驱动为并行LVDS,输入电压范围可编程,默认1.5V。

看看代码,这里重点关注原语部分,OD0和OD1,确定了外部时钟为500MHz。

点击查看代码

module ad9434_dri#(

parameter F_CLK = 200_000_000

)(

input i_gclk_p ,

input i_gclk_n ,

input i_grst_n ,

//ADC1

input [11:0] i_adc1_data_p ,

input [11:0] i_adc1_data_n ,

input i_adc1_dco_p ,

input i_adc1_dco_n ,

//ADC1

input [11:0] i_adc2_data_p ,

input [11:0] i_adc2_data_n ,

input i_adc2_dco_p ,

input i_adc2_dco_n ,

//SPI

output o_adc_sclk ,

output o_adc_sdio ,

output o_adc1_ncs ,

output o_adc2_ncs ,

//tri

input i_tri_0 ,

input i_tri_1 ,

//clk

output o_clk_od0 ,

output o_clk_od1

);

wire clk_locked;

wire ila_clk ;

wire vio_clk ;

wire dco_sel ;

wire [11:0] adc1_data ;

wire [11:0] adc2_data ;

wire adc1_dco ;

wire adc2_dco ;

assign ila_clk = dco_sel? adc1_dco : adc2_dco;

assign o_clk_od1 = 'd0;

assign o_clk_od0 = 'd0;

genvar num;

generate

for(num = 0;num < 12;num = num + 1) begin : ibuf

IBUFDS #(

.DIFF_TERM ("FALSE" ),

.IBUF_LOW_PWR ("TRUE" ),

.IOSTANDARD ("DEFAULT" )

) ibuf_data1 (

.O (adc1_data[num] ),

.I (i_adc1_data_p[num] ),

.IB (i_adc1_data_n[num] )

);

IBUFDS #(

.DIFF_TERM ("FALSE" ),

.IBUF_LOW_PWR ("TRUE" ),

.IOSTANDARD ("DEFAULT" )

) ibuf_data2 (

.O (adc2_data[num] ),

.I (i_adc2_data_p[num] ),

.IB (i_adc2_data_n[num] )

);

end

endgenerate

IBUFDS #(

.DIFF_TERM ("FALSE" ),

.IBUF_LOW_PWR ("TRUE" ),

.IOSTANDARD ("DEFAULT" )

) ibuf_dco1 (

.O (adc1_dco ),

.I (i_adc1_dco_p ),

.IB (i_adc1_dco_n )

);

IBUFDS #(

.DIFF_TERM ("FALSE" ),

.IBUF_LOW_PWR ("TRUE" ),

.IOSTANDARD ("DEFAULT" )

) ibuf_dco2 (

.O (adc2_dco ),

.I (i_adc2_dco_p ),

.IB (i_adc2_dco_n )

);

ila_0 ila_0_u0 (

.clk (ila_clk ),

.probe0 (adc1_data ),

.probe1 (adc2_data ),

.probe2 (i_tri_0 ),

.probe3 (i_tri_1 )

);

vio_0 vio_0_u0 (

.clk (vio_clk ),

.probe_out0 (dco_sel )

);

clk_wiz_0 clk_wiz_0_u0(

.clk_in1_p (i_gclk_p ),

.clk_in1_n (i_gclk_n ),

.vio_clk (vio_clk ),

.locked (clk_locked )

);

endmodule

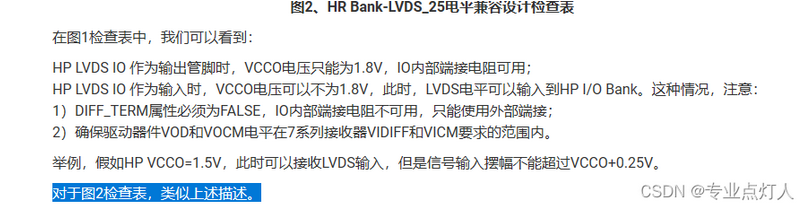

例化 IBUFDS(差分输入缓冲器)用于处理 AD9434 的差分数据(data)和时钟输出(DCO)信号,将 AD9434 输出的 差分 LVDS 时钟信号(DCO_P/DCO_N) 和差分数据信号转换为 FPGA 内部可用的单端时钟和数据信号。

.DIFF_TERM ("FALSE" ),

.IBUF_LOW_PWR ("TRUE" ),

.IOSTANDARD ("DEFAULT" )

分别为不启动100欧姆差分电阻,启动低功耗模式,电平标准依赖 FPGA 工程的全局约束,及xdc文件指定。

但是原理图里没有端接100欧姆电阻。所以其实建议这里改为ture,但是fpga内部终端电阻据ds说精度不行,所以还是建议外部使用100欧姆电阻。

这里建议使用HR bank 理由如下:

浙公网安备 33010602011771号

浙公网安备 33010602011771号