CDCM61002

https://item.szlcsc.com/542872.html?lcsc_vid=QQBdVQZfE1cKAVRfTlBfBFJVQgRWVwUHQQBXXwVWQ1QxVlNTQ1RbVlVUQVBYVDsOAxUeFF5JWAIASQYPGQZABAsLWA%3D%3D

参考链接 https://blog.csdn.net/mcupro/article/details/127211449

参考链接 https://oshwhub.com/jianxissss/fmc_9434

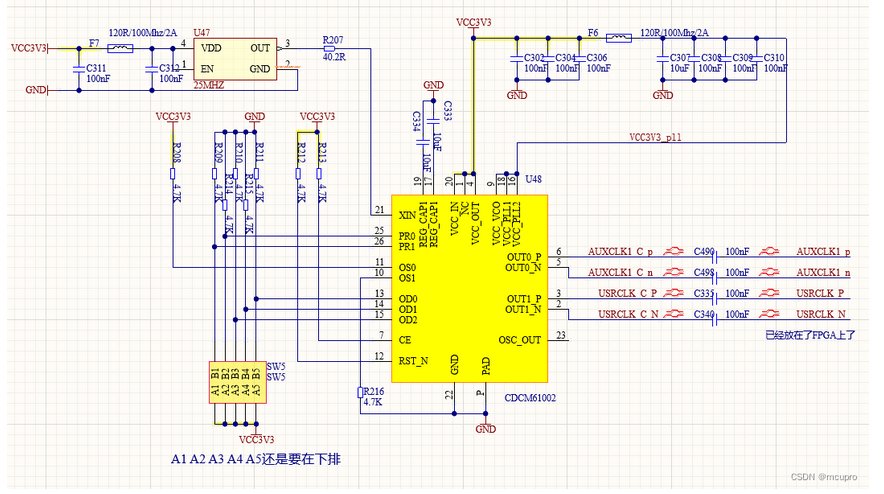

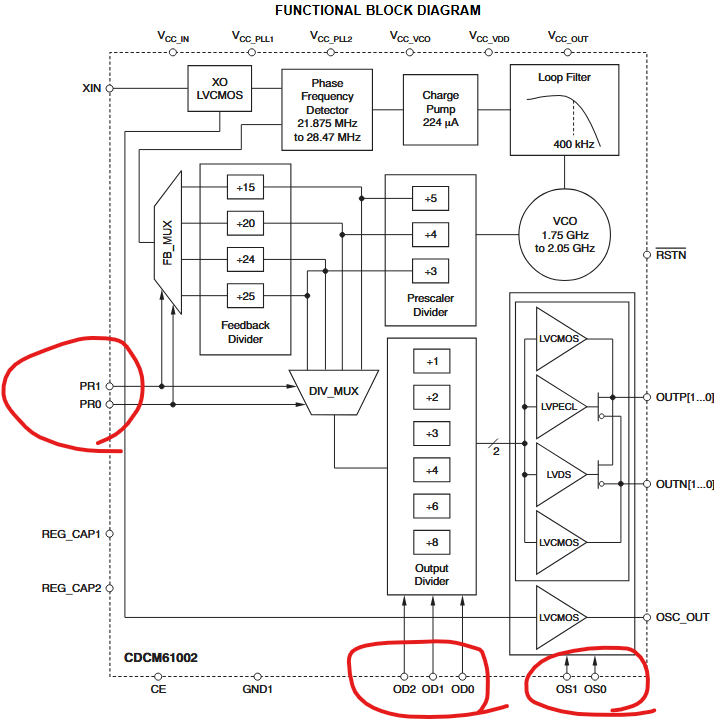

比较重要的应该是这几个引脚。

不同的上下拉组合对应不同的使用选择,但是不支持软编程切换,只能改变不同的组合重新上电切换。

两个案例的参考输入都是25MHz晶振,OS10组合为01,表明输出时钟为LVDS标准,且关闭OSC_OUT,在输出频率方面,天嵌通途支持拨码开关断电切换,蟹老板则是固定使用,先看蟹老板的。

OD210为001,PR10组合为11,对应OUTPUT DIVIDER为2,PRESCALER DIVIDER为4,FEEDBACKDIVIDER为20,对应输出频率如下,为250MHz,这边蟹老板OD0接了一个FPGA信号,想用FPGA来控制采样率,因为AD9434是给多少的时钟信号,就是多少的采样率,最高500MHz,OD210为001是250MHz,改成OD210为000,理论上是500MHz,但手册里没有这个组合,可能需要实测一下。。

浙公网安备 33010602011771号

浙公网安备 33010602011771号