官方文档如下https://byu-cpe.github.io/ecen330/media/interrupts/pg099-axi-intc.pdf

介绍如下,简单来讲,这是一个将多个外部中断合并为一个中断输出的IP核,存储有中断向量地址、检查、启用和确认中断的寄存器并可以通过AXI4 Lite接口访问。

特点如下,简单来讲,1-使用AXI4-Lite协议访问寄存器,2-快速中断模式,3-支持高达32个外部中断输入,并且支持级联,4-总线或单线输出(这个体现在中断输出上,我是用的single),5-输入中断之间,低位优先级最高,6-可自定义开启某个输入中断,7-主使能寄存器用于全局控制中断请求输出。只有当主使能寄存器被启用时,中断请求才会被传递到处理器。 8-输入中断支持电平和边沿触发,9-输出中断同意支持电平和边沿,GUI界面可设置,10-AXI INTC 支持软件中断功能,允许软件通过写寄存器来触发中断,应该可以理解为模拟外部触发,有在vitis里xitc.h的example里看到过,11-嵌套中断,即在高优先级中断处理过程中可以响应更高优先级的中断,12-旧版本的软件可以在新硬件上运行,反之亦然。。

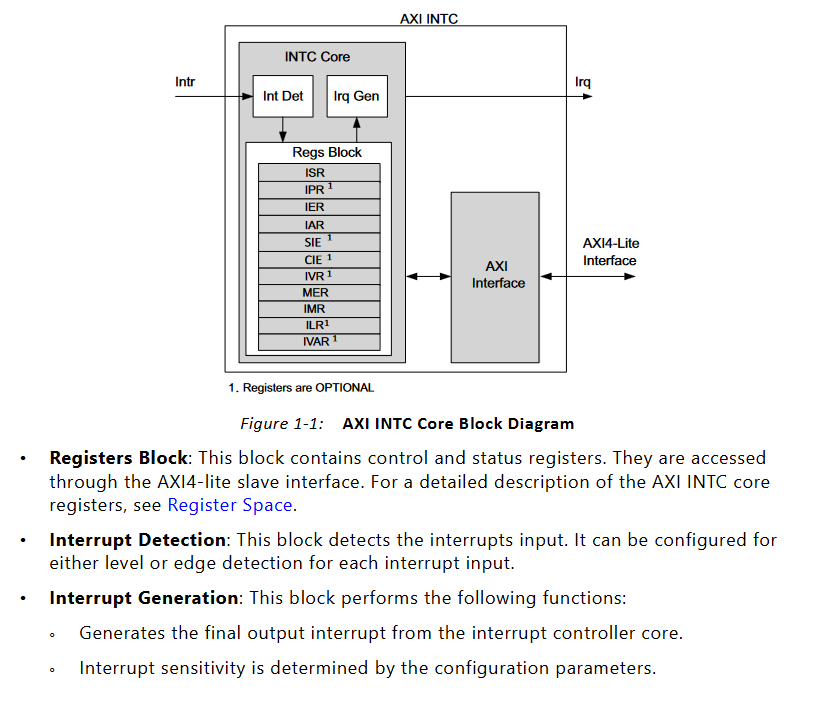

IP核内部架构如下,Registers Block就是通过AXI4-Lite协议访问的寄存器,Interrupt Detection用于检测连接的外部输入中断,至于Interrupt Generation,一、中断生成:中断控制器核心生成最终的中断输出信号,触发方式由配置参数决定。二、使能条件检查:通过 MER 和 IER 寄存器控制中断的全局和局部使能。三、中断复位:在中断被确认后,复位中断状态以允许后续中断。四、向量地址写入:将活动中断的向量地址写入 IVR 寄存器,并启用 IPR 寄存器记录挂起中断。

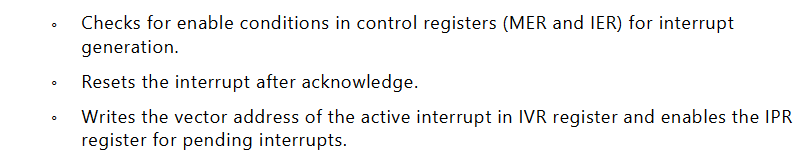

而在输入检测方面,有以下特点,第一是对于某一外部中断输入,无论是边沿检测还是电平检测,无论是否使能,当有中断条件时,都会被记录直到被清除,二是对于不同检测情况,有以下区分: 异步中断检测通过时钟同步后采样中断输入信号,确保信号的稳定性。边沿敏感中断检测需要信号在一个时钟周期内从无效变为有效,才能被检测到。电平敏感中断检测需要信号至少在一个时钟周期内保持有效电平,才能被检测到。手册里给了一个边沿触发的示意图如下。

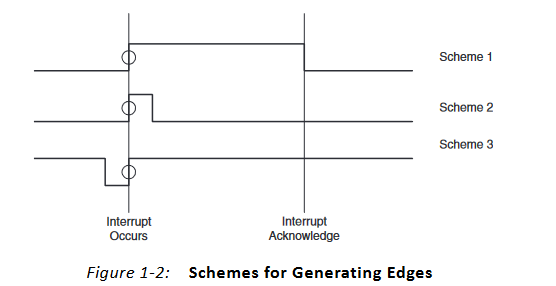

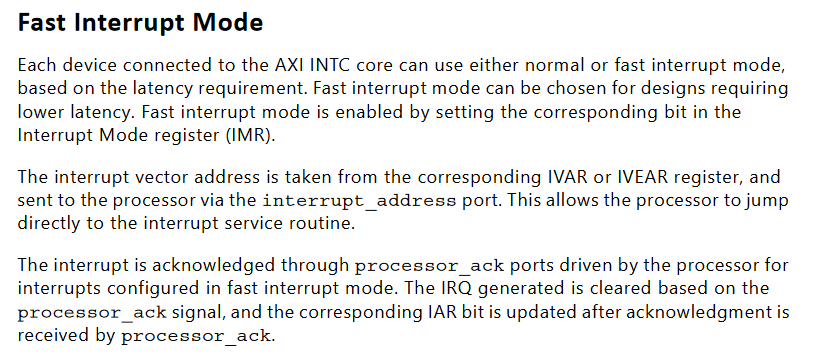

对于快速中断模式:适用于需要低延迟的设计,通过设置 IMR 寄存器启用。中断向量地址:从 IVAR 或 IVEAR 寄存器获取,通过 interrupt_address 端口发送给处理器,直接跳转到 ISR。中断确认:处理器通过 processor_ack 端口确认中断,清除 IRQ 信号并更新 IAR 寄存器。

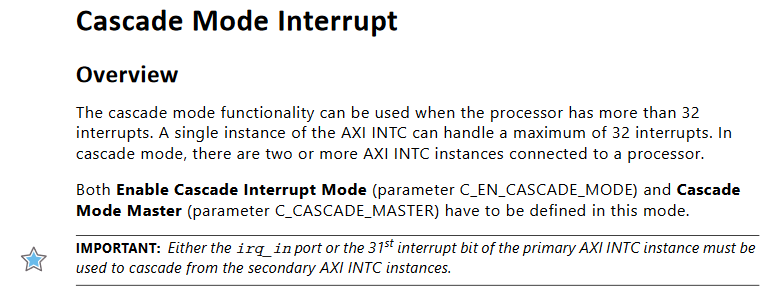

当系统需要处理超过32个中断时,可以通过级联模式扩展 AXI INTC 核心的能力。具体方法是实例化一个或多个额外的 AXI INTC 核心,并相应地设置级联模式参数。级联模式允许多个中断控制器协同工作,以支持更多的中断输入。

AXI INTC 核心还支持可配置数量的软件中断,主要用于多处理器系统中的处理器间中断(IPI)。软件中断通过向中断状态寄存器(Interrupt Status Register)写入数据来触发,允许软件直接控制中断的生成和处理。

AXI INTC 核心通过实现中断级别寄存器(Interrupt Level Register)来支持嵌套中断。软件可以利用该寄存器在处理中断时阻止低优先级中断的发生,从而允许在处理中断期间启用中断以立即响应更高优先级的中断。软件必须保存和恢复中断级别寄存器和返回地址。在使用快速中断模式时,处理器会直接跳转到唯一的中断向量地址以服务特定中断。因此,用户的中断服务程序(ISR)代码必须自行保存和恢复中断级别寄存器和返回地址。在普通中断模式下,这些操作由软件驱动程序处理。

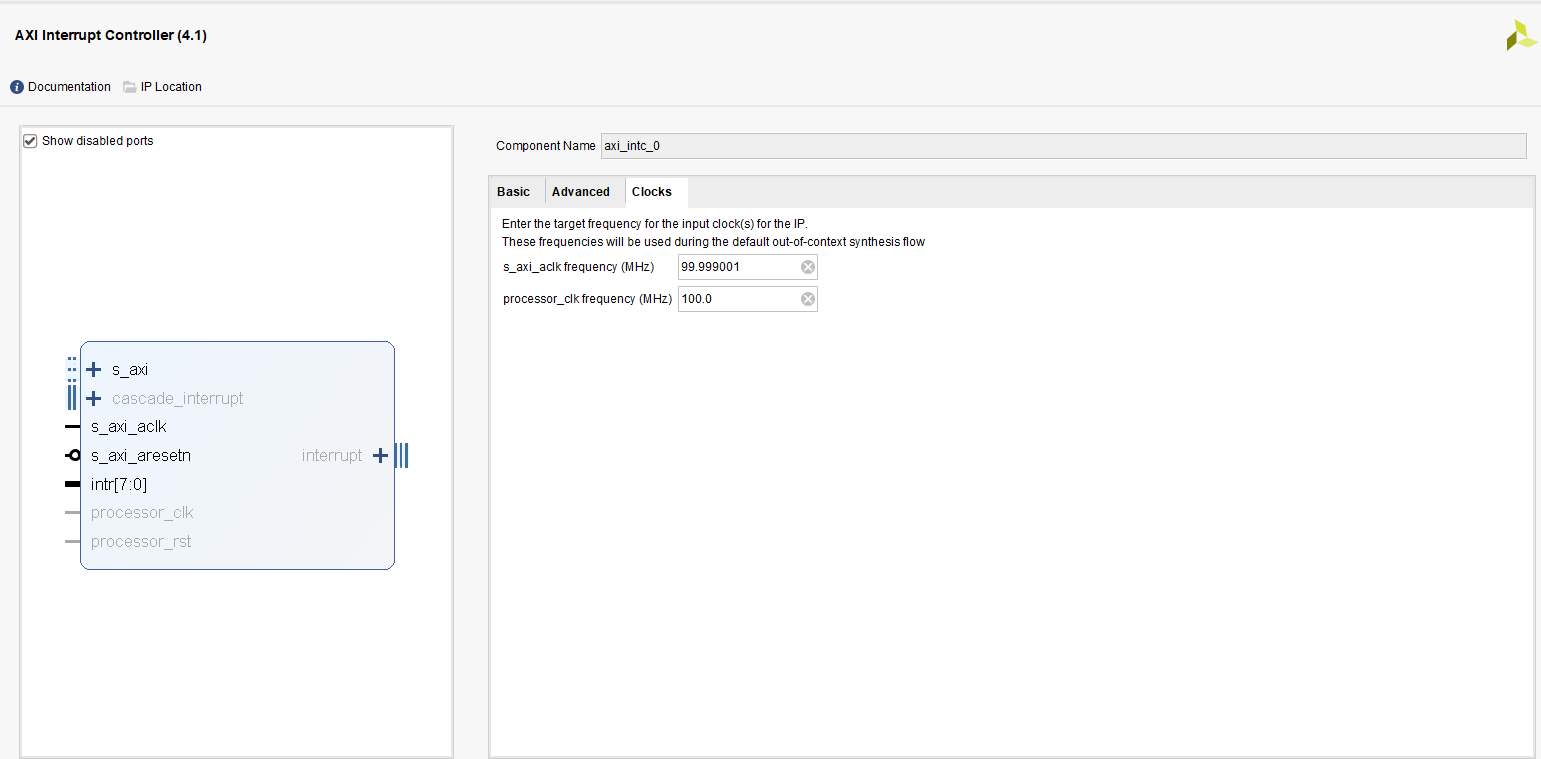

这里是IP核的所有使用引脚,同时也贴出一张调用时的实际使用GUI界面。

当然,为了更好的使用和最大化利用,除GUI之外我们还可以参数化定制,不过菜鸟(比如说我)一般不这样做,这里贴一下表示可以这样做。

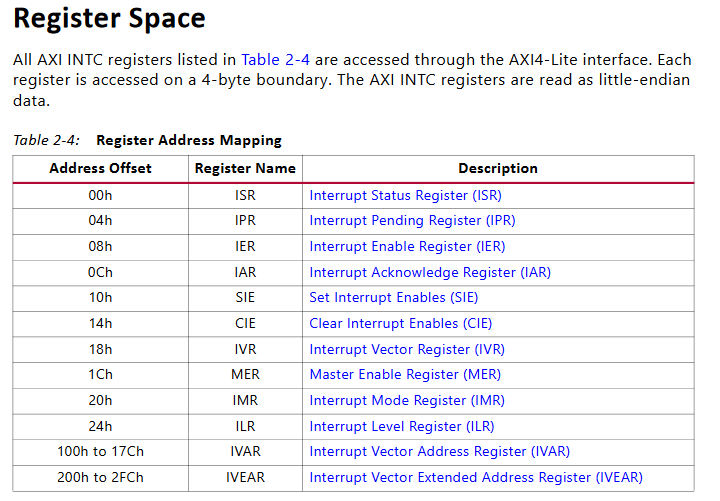

表 2-4 中列出的所有 AXI INTC 寄存器都通过 AXI4-Lite 接口访问。每个寄存器在 4 字节边界上访问。AXI INTC 寄存器以小端格式读取数据。具体详情可在开头链接中查询

关于时钟和复位方面如下

在上电或复位时,AXI INTC 核心会初始化为所有中断输入和中断请求输出被禁用的状态。为了使 AXI INTC 核心能够接受中断并请求服务,需要执行以下步骤:将 IER(中断使能寄存器) 中与中断对应的每个位设置为 1。这使得 AXI INTC 核心能够开始接受中断输入信号和软件中断。INTO 具有最高优先级,对应于 IER 中的最低有效位(LSB),根据 AXI INTC 核心的预期用途配置 MER(主使能寄存器)。MER 中有两个位:硬件中断使能(HIE) 和 主中断请求使能(ME)。必须设置 ME 位以启用中断请求输出。如果需要对硬件中断进行软件测试,HIE 位必须保持其复位值 0。现在可以通过向 ISR(中断状态寄存器) 中与现有中断输入或软件中断对应的任何位写入 1 来进行软件测试。如果该中断已启用,则会生成相应的中断请求,中断处理正常进行。在完成硬件中断的软件测试后(或如果未进行测试),必须向 HIE 位写入 1,这将启用硬件中断输入并禁用任何进一步的软件生成的硬件中断。最后向 HIE 位写入 1 后,对该位的任何进一步写入都不会产生影响。

级联模式使用及注意事项:级联一般用于外部中断数量超过32个的情况,首先就是GUI界面中红框的两处要选上,其次,第二个 AXI INTC 实例的输出必须连接至irq_in端口(选中才能看到)或第31个端口

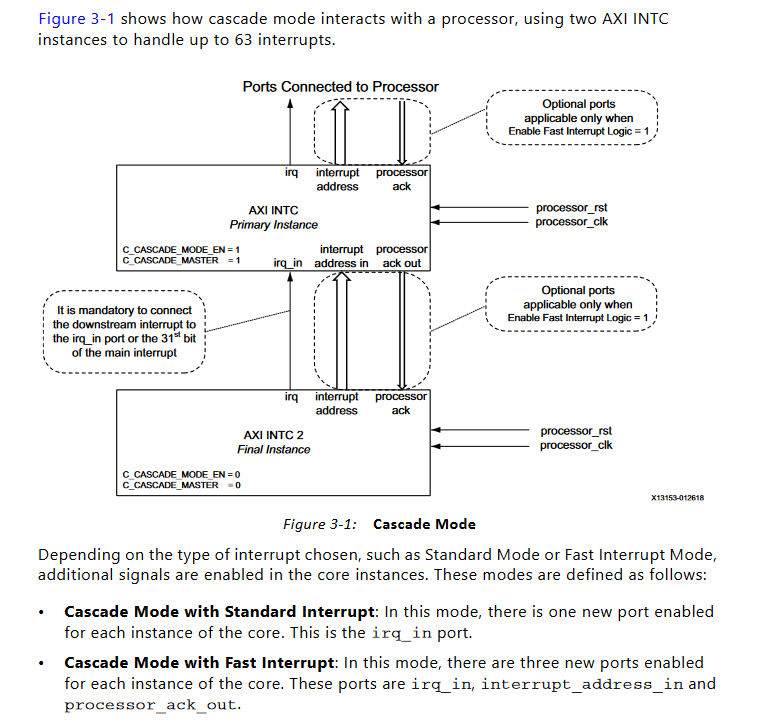

图 3-1 展示了级联模式如何与处理器交互,使用两个 AXI INTC 实例来处理最多63个中断。主 AXI INTC 实例:配置为级联模式(C_CASCADE_MODE_EN = 1)和级联主控(C_CASCADE_MASTER = 1)。从 AXI INTC 实例:配置为级联模式禁用(C_CASCADE_MODE_EN = 0)和级联主控禁用(C_CASCADE_MASTER = 0)。可选端口仅在启用快速中断逻辑时适用。根据选择的中断类型(标准模式或快速中断模式),核心实例中会启用额外的信号:标准中断级联模式:每个核心实例启用一个新端口 irq_in。快速中断级联模式:每个核心实例启用三个新端口 irq_in、interrupt_address_in 和 processor_ack_out。

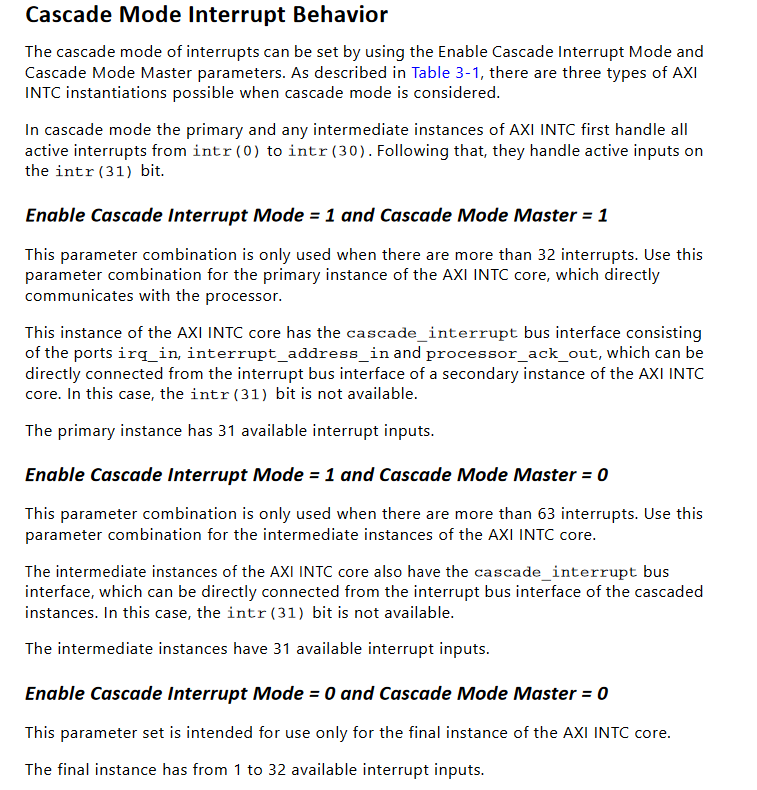

通过使用 启用级联中断模式(Enable Cascade Interrupt Mode) 和 级联模式主控(Cascade Mode Master) 参数,可以设置中断的级联模式。如表 3-1 所述,在级联模式下,AXI INTC 实例可以分为三种类型。在级联模式下,主 AXI INTC 实例和任何中间实例首先处理从 intr(0) 到 intr(30) 的所有活动中断,然后处理 intr(31) 位上的活动输入。参数组合 1:启用级联中断模式 = 1 和级联模式主控 = 1,此参数组合仅在需要处理超过32个中断时使用。用于直接与处理器通信的主 AXI INTC 核心实例。此实例具有 cascade_interrupt 总线接口,包括 irq_in、interrupt_address_in 和 processor_ack_out 端口,可以直接连接到次级 AXI INTC 核心实例的中断总线接口。在这种情况下,intr(31) 位不可用。参数组合 2:启用级联中断模式 = 1 和级联模式主控 = 0, 此参数组合仅在需要处理超过63个中断时使用。用于 AXI INTC 核心的中间实例。中间实例也具有 cascade_interrupt 总线接口,可以直接连接到级联实例的中断总线接口。在这种情况下,intr(31) 位不可用。 参数组合 3:启用级联中断模式 = 0 和级联模式主控 = 0, 此参数集仅用于 AXI INTC 核心的最终实例,前两个实例仅有31个可用中断输入,最终实例有1到32个可用中断输入。

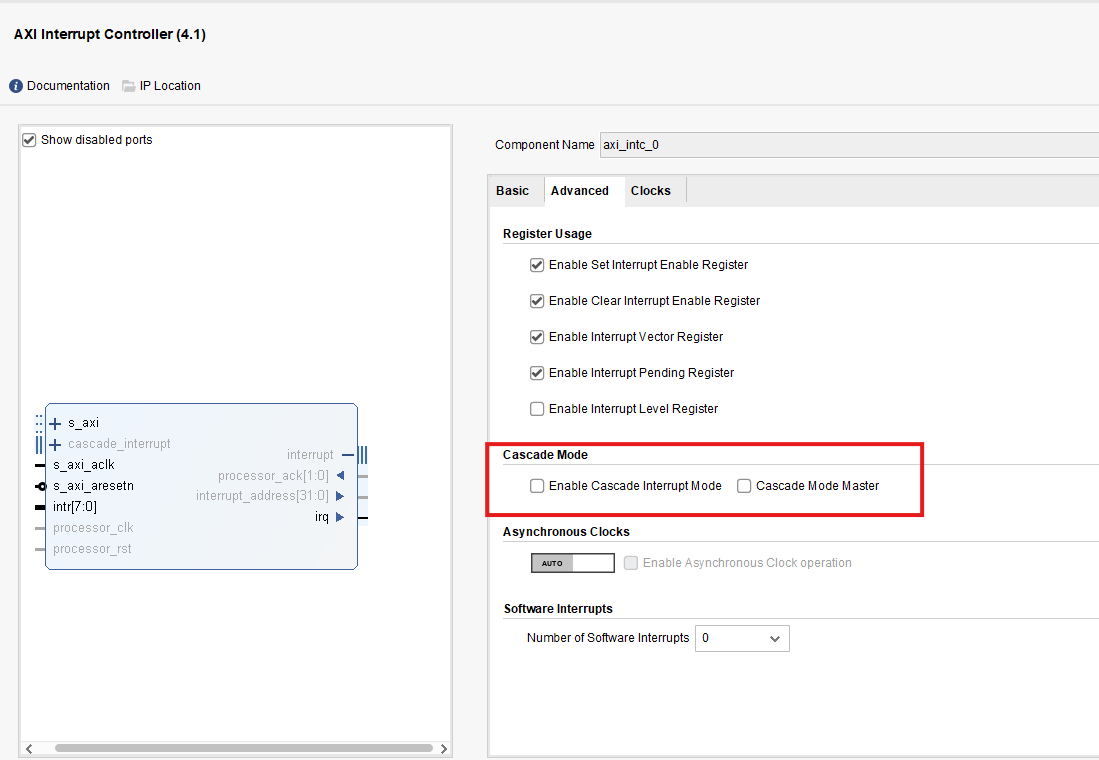

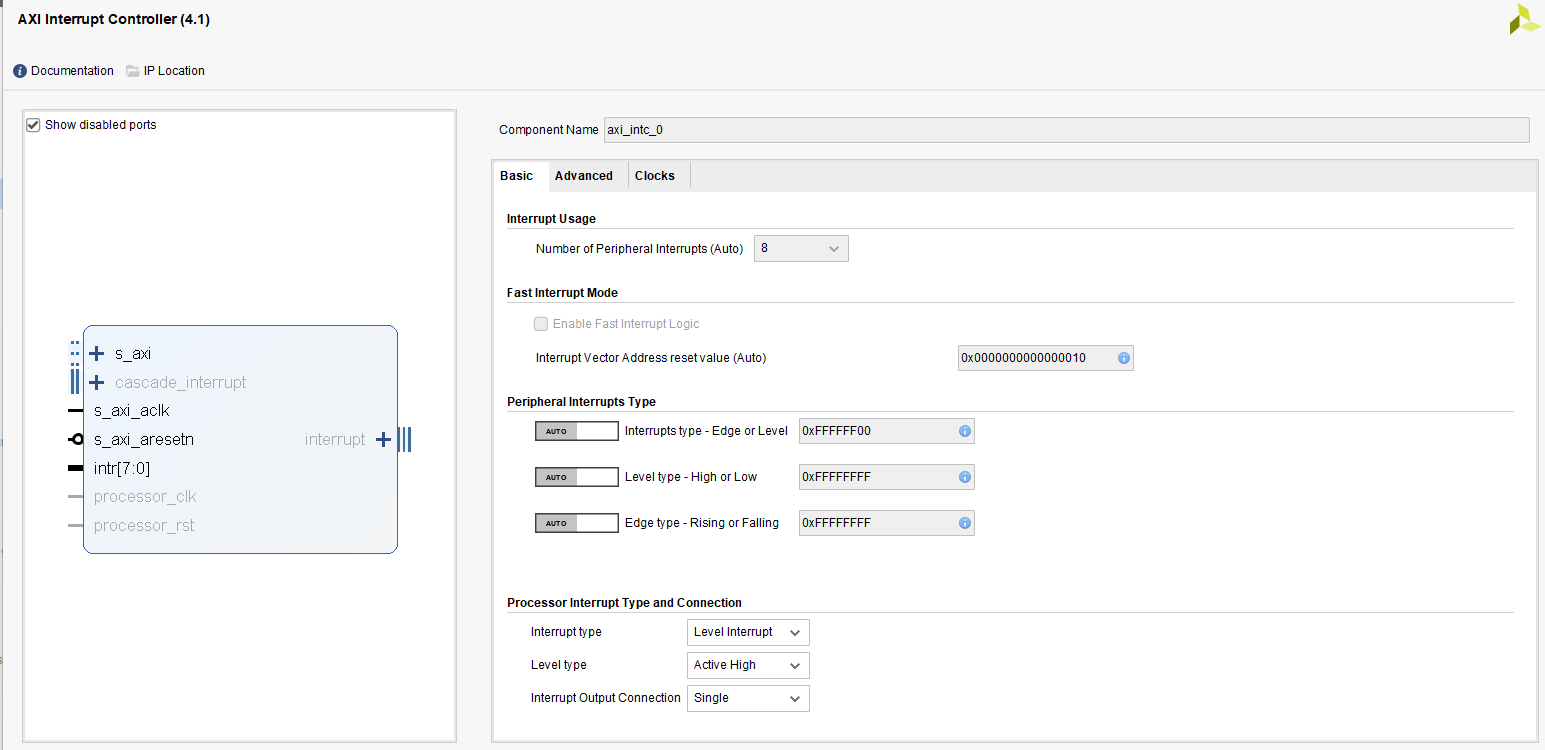

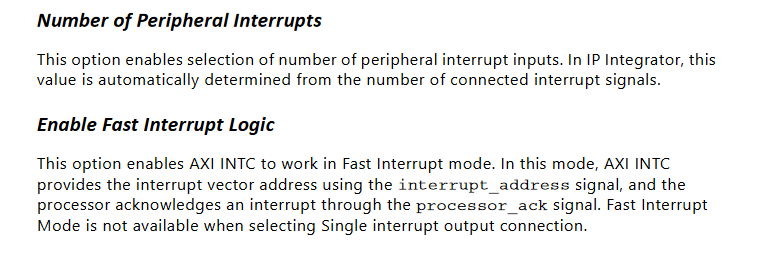

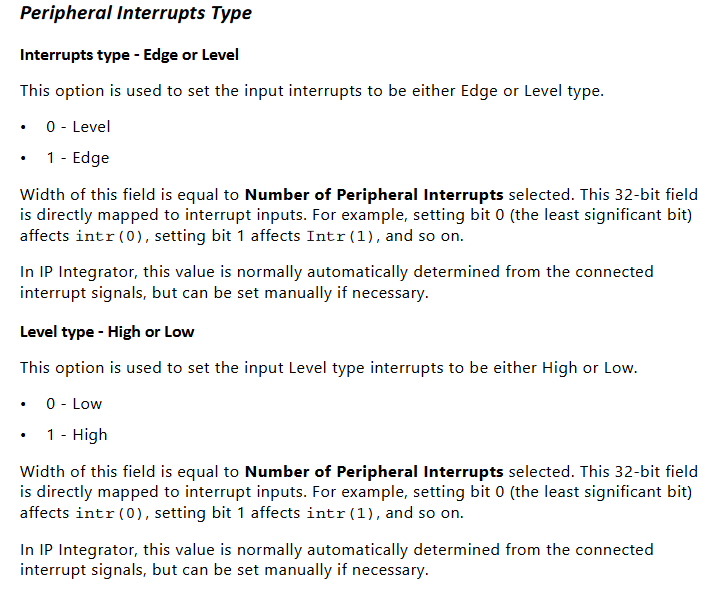

最后是GUI界面配置指南,我这边vivado使用的是2020.2版本,首先是Basic界面,前面灰色都是可以自动识别对应,这边无须担忧,包括输入中断数量,是否启用快速中断,以及输入中断的性质,高低电平还是上下升沿,而在中断输出配置这边,通常,Bus 用于连接到 MicroBlaze 和级联的 AXI 中断控制器。否则,当未启用快速中断模式且目标设备具有单个中断输入时,可以使用 Single。

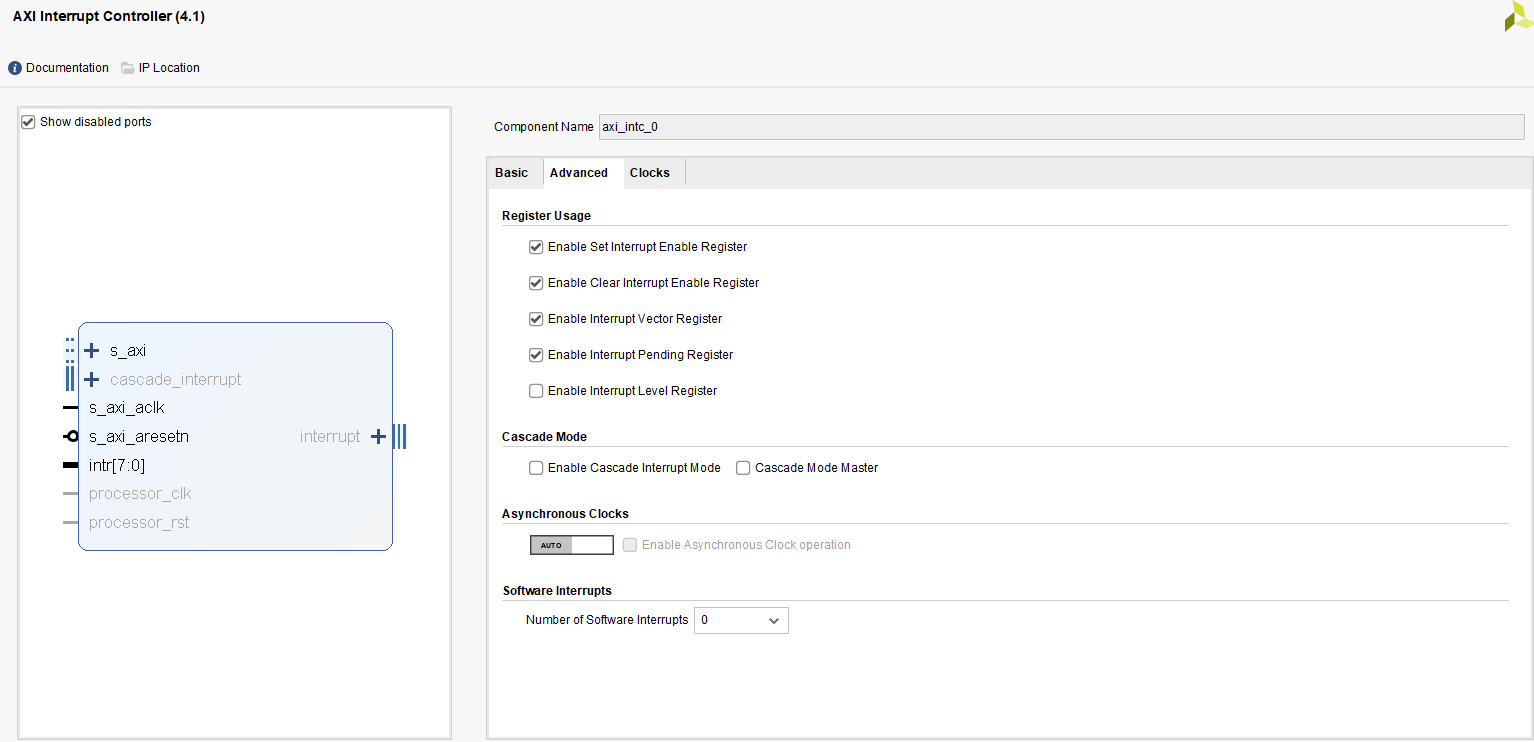

Basic界面之后是advanced界面,一般保持默认即可,如果要用嵌套就使能Enable Interrupt Level Register,如果要级联就使能Enable Cascade Interrupt Mode和Cascade Mode Master,Enable Asynchronous Clock Operation用于启动异步时钟,启用此选项允许 AXI 时钟和处理器时钟异步运行,Number of Software Interrupts为选择软件中断的数量。最大中断数量为 外设中断数量 + 软件中断数量,且总和不超过32。看个人使用情况。

最后是clocks界面,一个是axi4协议时钟,一个是处理器时钟,看个人情况,一般上述的大多数都会自动调整,如无特别需求,如嵌套、级联、软触发、异步,基本就可以默认设置进行使用。

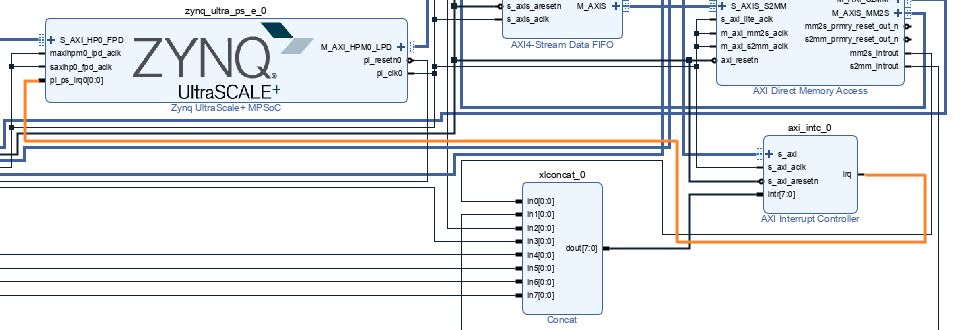

最后是我个人用的block design 界面,我连了8个外部中断,使用了single输出 axi interrupt controller的irq最后连接到MPSOC的pl_ps_irq[0]。

浙公网安备 33010602011771号

浙公网安备 33010602011771号