voltus的IR drop分析(简单流程&脚本设置)

run Voltus的前提:

当前Voltus版本为新版本

(之前使用旧版本run的时候出现bug,具体体现为:工具提示pg mesh全是断开的;更新软件为最新版本后OK)

当前的power mesh未出现问题(比如site row和PG net匹配)

一:文件准备

voltus的环境文件配置

voltus需求文件

pgv库(将PR中用到的库文件转为voltus可使用的文件类型,用于dynamic&static analysis)

sdc file(用于static analysis)

spef(static分析时,对应corner的spef file)

vcd file(static分析时,对应的波形文件)

1:pgv库配置

pgv库分别配置std库;mem库;IP库

配置库命令:

libgen_stdcell.tcl(生成std cell PGV)

read_lib -lef “ \****

”

set_pg_library_mode \

-ground_pins ** \

-power_pins ** \

-decap_cells ** \

-filler_cells ** \

-celltype stdcells \

-spice_models ** \

-spice_corners ** \

-spice_subckts **(stdcell库的.spi文件) \

-lef_layermap ** \

-current_distribution propagation \

-temperature ** \

-extraction_tech_file **

set_advanced_pg_library_mode -libgen_command_file libgen.inc

generate_pg_library \

-output stdcell_pgv_tt

ps:

1,spice_subckts和spice_models要对应(常用工艺低一个版本也可以,因为工厂的Cell很少大改)

2,lef_layermap:是需要手写的一个带有金属层信息的文件,文件格式如下

#layer type tech layer name lefdef layer name

metal ME1_C lefdef ME1

via VIA1 lefdef VI1

3,tech_file:工艺库下的Tech file

4,在read_lib_lef的时候,将tech lef放在第一位

-----------------------------------------------------------------------------------

libgen_techonly.tcl (生成IP的pgv)

read_lib -lef "

\

"

set_pg_library_mode \

-celltype techonly

-extraction_tech_file *****(文件路径)

-power_pins {VDD 0.74 VDDH 1.98}

-ground_pins {VSS GND]

-default_area_cap 0.5

-temperature 125

generate_pg_library \

-output tech_pgv

二:执行脚本(voltus在进行IR分析的时候分为dynamic和static)

1,power_func.tcl

2,rail_func.tcl

-------------------------------------------------------------------------------------------------------1,power_func.tcl

source read_design.tcl

##read sdc

read_sdc **

##read spef

read_spef **

####read_vcd

##set vcd_file ***.vcd

##read_activity_file $vcd_file -format VCD -scope ***/*** -start ***ns -end ***ns(scope指的是vcd中波形的top;例:soc_top/u_top)

(run动态分析时需要吃的vcd文件)

###load pgv file(run dynamic analysis时需要)

#set pgv_list [list \

#

#]

set_default_switching_activity -reset

####

set_power_analysis_mode -reset

####

set_power_analysis_mode \

-method static (dynamic_vectorbased)\

-create_binary_db true (false)\

#-disable_static false \ (dynamic)

-write_static_currents true (false)\

#-power_grid_library $pgv_list \(dynamic)

-report_missing_nets true \

-disable_ecsm_interpolation true \

-honor_negative_energy true \

-transition_time_method true \

-default_frequency 200 \(参数根据需求设置,建议参考上一版)

#-default_slew 0.5 \ (dynamic参数,参数根据需求设置,建议参考上一版)

-enable_slew_based_ccs_pin_cap true \

-report_missing_inout true \

-disable_leakage_scaling true \

-clock_source_as_clock true \

#-x_transition_factor 1 \(dynamic参数)

#-z_transition_factor 1 \(dynamic参数)

#-report_missing_nets true(dynamic参数)

####

set_power_output_dir -reset

set_power_output_dir staticPowerResultFunc(power分析文件存储位置,里面是一些电流文件)

report_power -outfile **.rpt

report_power -instances {*} -outfile all.rpt

-------------------------------------------------------------------------------------------------------------2,rail_func.tcl

set_multi_cpu_usage -localCpu 8 -remoteHost 2 -cpuPerRemoteHost

set_distribute_host -local -timeOut 100

set pgv_list [list \

********

********]

###static设置

set_rail_analysis_mode -method static -accuracy hd \

-power_grid_library $pgv_list \

-temperature 125 \

-enable_rlrp_analysis true \

-rlrp_threshold 60 \

-em_temperature 120 \

-ignore_fillers true \

-ignore_decaps true \

-extraction_tech_file *****/qrctechfile(文件路径)

-temp_directory_name .***(文件路径)

-ignore_incomplete_net true \

-ignore_shorts true \

-filler_cell_list {****} \

-decap_cell_list ***

-process_techgen_em_rules true

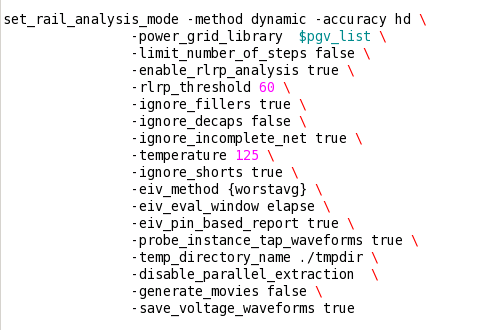

###dynamic设置

###

####

set top_power " \

****xxx.ptiavg(此处放之前power_func.tcl run出的PowerResultFunc中的.ptiavg)

例:

PowerResultFunc/static_VDD.ptiavg

PowerResultFunc/static_VSS.ptiavg

(run dynamic的时候改成dynamic的ptiavg)

"

set_power_data -reset

set_power_data -format current -scale 1 $ top_power

###设置power点

set_power_pads -net * -format xy -file ******(net对应的pin的点坐标,电源实际提供多少就写多少组)

###设置power ground net的电压值

set_pg_nets -net VSS -voltage 0.0 -threshold 0.010

set_pg_nets -net VDD -voltage 1.32 -threshold 1.310

###设置rail_analysis,进行IR drop分析

set_rail_analysis_domain -name allDomains -pwrnets "VDD" -gndnets VSS

set_multi_cpu_usage -localCpu 8 -remoteHost 2 -cpuPerRemoteHost 4

set_distribute_host -local -timeout 100

analyze_rail -type domain -results_directory ./ allDomains

ps:

read_design.tcl文件结构

source lef.list

source lib.list

read_verilog ***.v

set_top_module **** -ignore_undefined_cell

read_def ***.def

--------------------------------------------------------------------------------------------------------------------

浙公网安备 33010602011771号

浙公网安备 33010602011771号