阅读<All Digital VCXO Replacement for Gigabit Transceiver Applications>笔记---XAPP589

Posted on 2017-10-11 09:42 沉默改良者 阅读(363) 评论(0) 收藏 举报阅读<All Digital VCXO Replacement for Gigabit Transceiver Applications>笔记---XAPP589

1.

2.

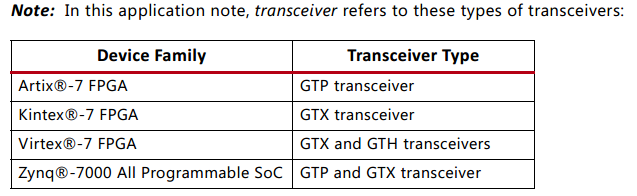

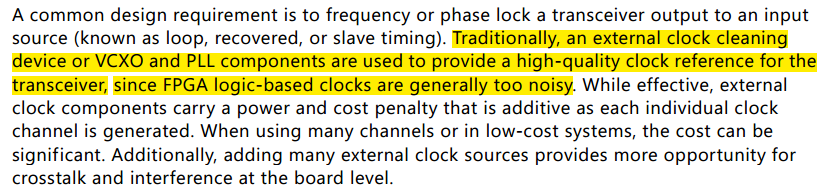

外部设备能为transceiver提供高质量的参考时钟,但是基于FPGA逻辑生成的时钟通常有较大噪声。同时,外部时钟太多,也会增大窜扰的几率。

3.

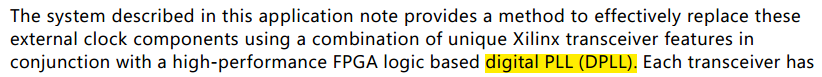

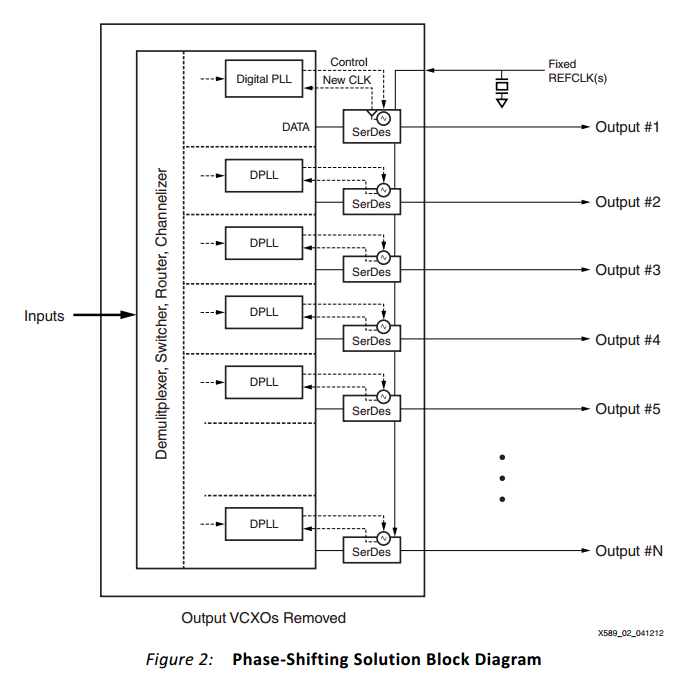

此例程介绍了一种高质量的DPLL,基于FPGA逻辑设计的DPLL。

4.

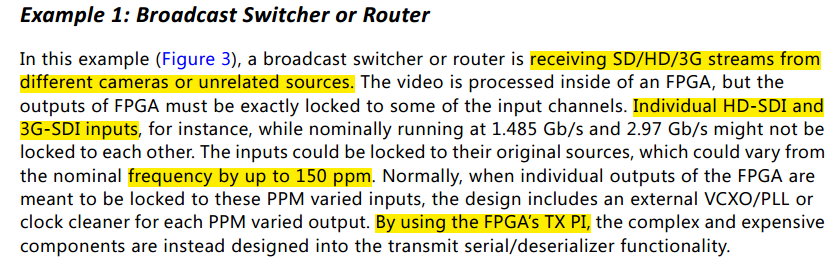

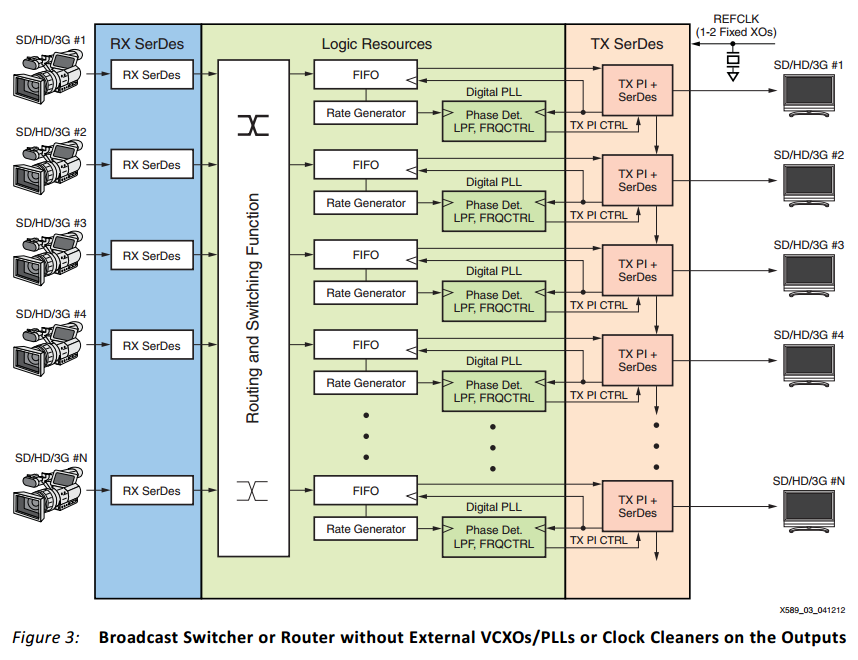

此设计运用在哪些领域。

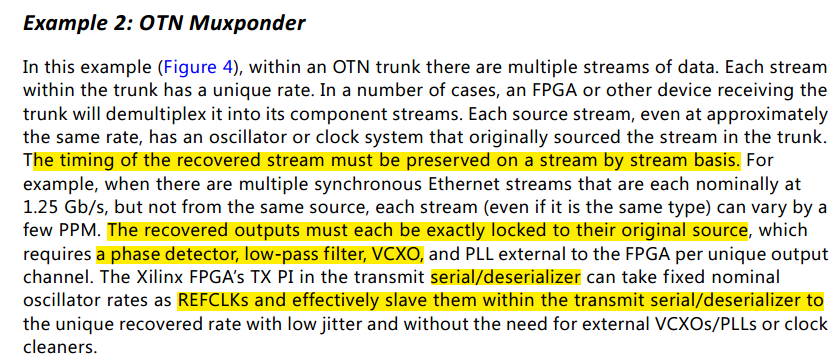

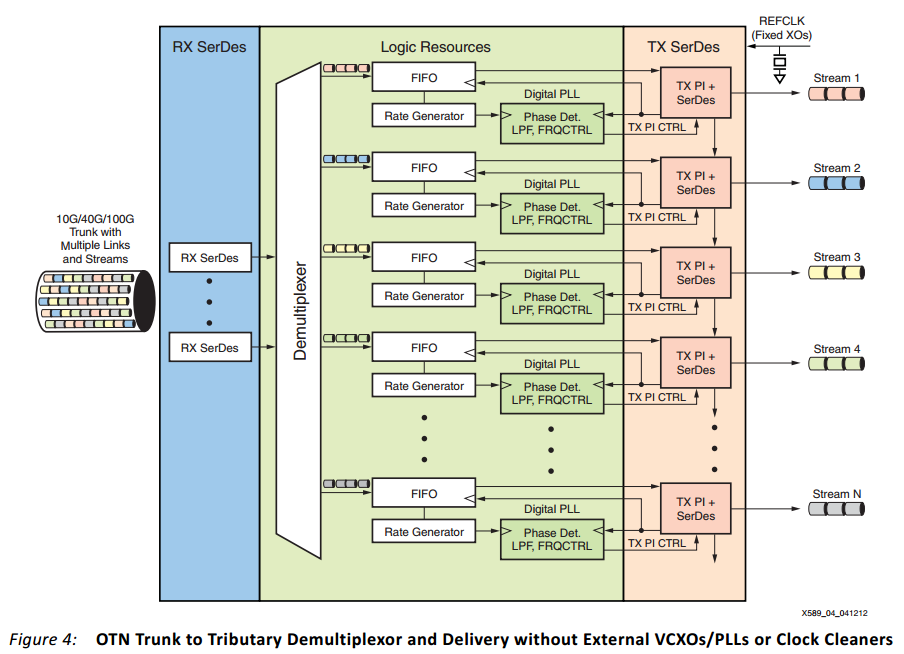

5.

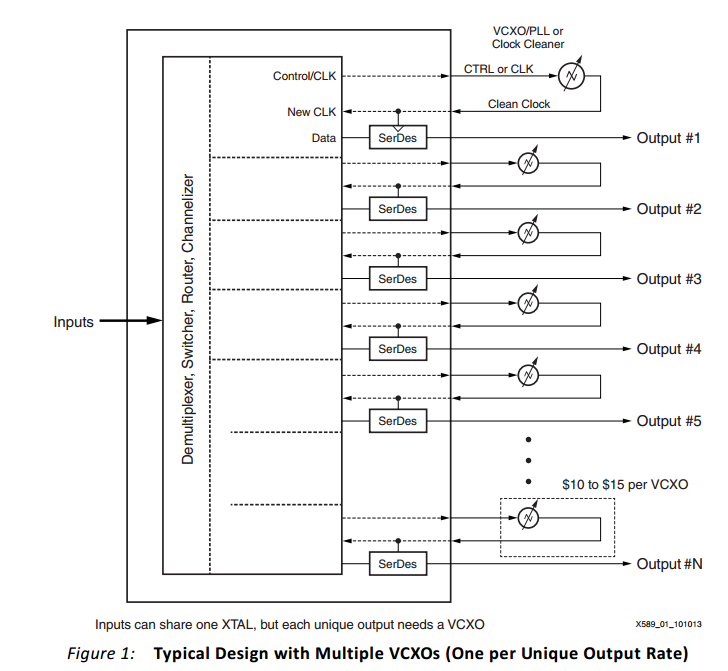

外部VCXO,一方面是增加了成本,增加了PCB布线的复杂度。

6.采用外部VCXO(硬件)

7.7 series FPGA (TX PI)

8.

9.

浙公网安备 33010602011771号

浙公网安备 33010602011771号