SciTech-EECS-Manufacturing-PCB Layout基础知识

SciTech-EECS-Manufacturing-PCB Layout基础知识

PCB Layout基础知识

PCB Layout是硬件电子设备必不可少的一个环节.

PCB Layout的规范及质量直接影响硬件设备的功能、性能、可靠性等.所以应对PCB Layout加以重视。

本文章对针对大厂PCB Layout的情况做一个简单的介绍。

1.PCB Layout工程师的工作内容

- 设计新元件封装和维护现有封装库;

- 布局元器件:

- 布局走线;

- 调节等长;

- 布局丝印文字;

- 检查和消除DRC;

- 输出Gerber文件。

2.与PCB Layout工程师相关的人员

- Electronic Engineer;

- 提供电路图及零件资料;

- 提出电气回路要求;

- 提出布局位置要求;

- 提出走线方式要求。

- Mechanical Engineer

- 提供机构尺寸图;

- 提供输入输出装置;

- 提供Heat Sink资料;

- 提供结构限制注意事项。

- EMI Engineer

- 提供电磁辐射要求及注意事项。

- PCB板制造厂商

- 提供PCB制程能力要求,如:可达最小线宽、线距。

3.PCB Layout Placement考虑点

- 电气特性:

在布局元器件时希望将某些元器件靠在一起摆放,

以缩短电路上的回路路径,降低干扰,减少电感量。 - 布线:

关系密切的元器件或相关电路模块应放在一起,

否则会增加布线的距离、难度和复杂度。 - 测试性:

需要测试的元器件最好摆放在板边,以方便测试和拆换。

保证测试点能被看得到、接触到为原则。 - 结构组装:

依据机构工程师提供的要求进行特殊元器件的布局,

比如依据限高区域、输入输出位置等要求进行布局。 - 散热性:

会产生热量的元器件不要紧靠摆放,务必将它们分散;

元器件尽量平行于风流方向,不要阻挡到风以提高散热。

电路板会因为热不平衡造成弯翘现象,进而使焊点受损,降低可靠性。 - 制程:

元器件排列方向, 决定波焊方向。若有元器件的阻隔(元器件太高或太靠近),

会使得后面的焊点(波焊方向)得不到良好的焊接, 而产生阴影效应或吃锡不均匀产生墓碑效应。

另外,尽量使元器件的极性方向同向,同一轴向、同一孔距、仅需一个置件头,

以提高SMT自动插件效率,增加产量、减少错误,增加可靠度。 - 美观性:元器件排列整齐,不但美观,还能有较好的散热效果。

4.PCB Layout相关资讯

-

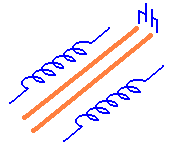

Cross Talk(串扰):

指当布线密度增加、平行走线距离过长,会使得两线传输线的互容、互感,将能量耦合至相邻的传输线上。

![]()

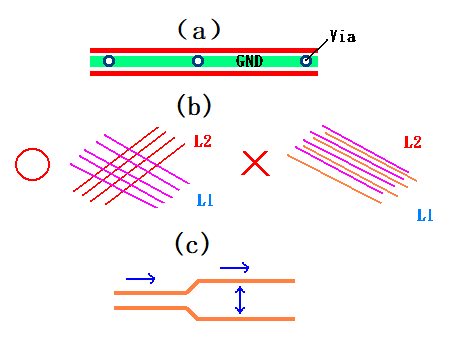

针对串扰的Layout对策有:- 在平行线间加入地线,且每一段距离就打Via至GND,可降低互容及具屏蔽效用;

- 不同层(特别使相邻层)时要互相垂直走线;

- 每走一段距离平行线,两者间的间距加大;如下图。

![]()

-

反射现象:

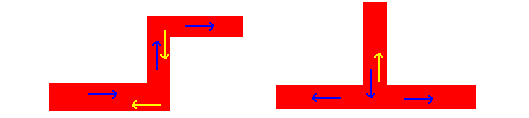

布线的弯角、分歧的线路太多所造成,使传输线上产生阻抗不匹配, 如图4

Layout对策是减少线路上的弯角及分歧线(或避免直角走线及分歧线补强), 如图5- 图4 弯角、分歧造成反射

![]()

- 图5 反射Layout对策

![]()

- 图4 弯角、分歧造成反射

-

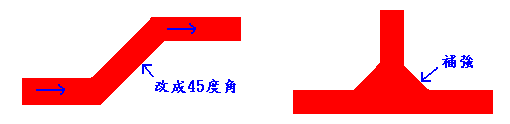

滤波电容和旁路电容走线:

Layout布线时,一旦忽略摆放在IC旁边的旁路电容、输入输出的滤波电容,

将使得电容功用失效,无法抑制电路所产生的杂讯。所以走线时:- 一定要注意走线顺序,主要有:

- 外部电源输入→滤波电容→旁路电容→后级电路;

- 内部电源→滤波电容→输出;

- 内部电源→旁路电容→IC引脚。

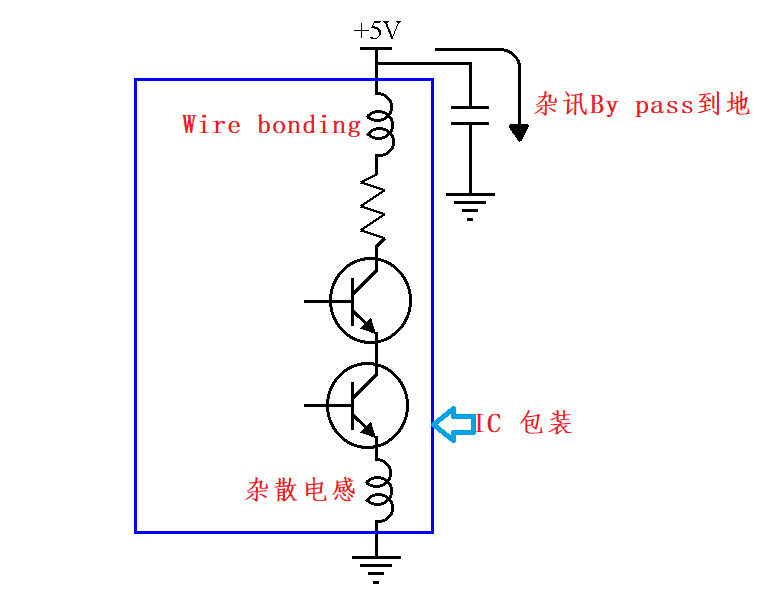

- 旁路(By pass)电容的作用:,

"IC的 OFF→ON": 会使电感产生反电压: V=-L(di/dt), 造成VCC电压略降,GND电压略升;

"IC的 ON→OFF": 则反之。如此升降关系, 杂讯便传出去了.

在VCC引脚旁加上一个小电容滤波,引导杂讯进入GND。

![]()

- 一定要注意走线顺序,主要有:

-

3W原则:

指为减少Cross talk(串扰)的与EMI, 线路间距需大于线宽的3倍以上。

注意3W算的是两邻线的中心距离; 但"差分线对"的最小中心距离可以是2W。

图7 3W间距

![]()

-

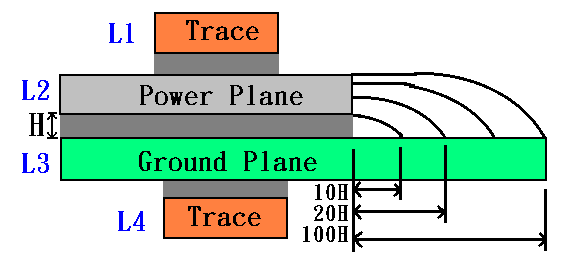

20H法则:

Fringing(层间耦合)效应: 多层板内VCC与GND两参考层的边缘对齐时, 会向外界发射RF电磁波.

将VCC内缩20倍的介质厚度(H),即可消除70%的边缘磁通量,故其称为20H法则。

若做到100H则可消除90%的磁通量.- 图8 层间耦合

![]()

- 图9 VCC内缩消除磁通量

![]()

- 图8 层间耦合

-

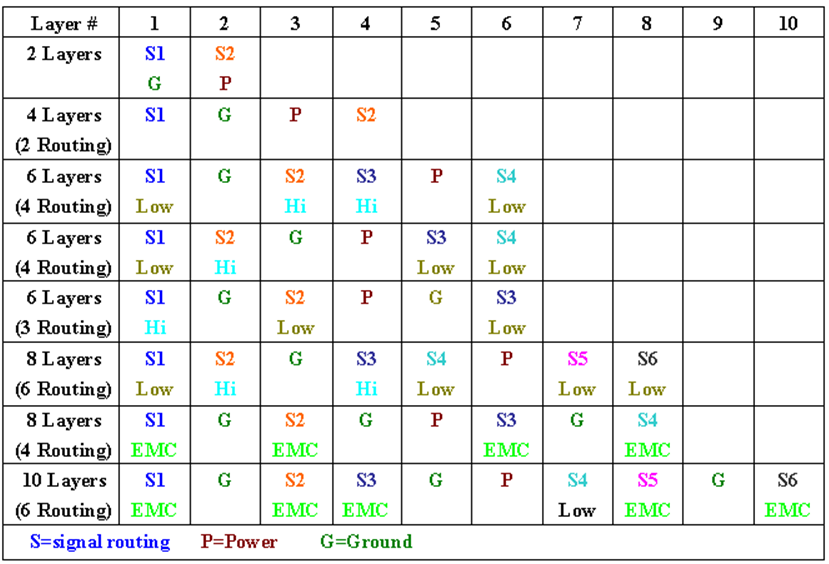

层序安排:

多层板Layout时,- 需确定各层易受干扰的信号位置,将较敏感信号放中间;

- 选出上、下层来提供较佳的屏蔽;

- 可将敏感较高电路与高杂讯电路用地隔离;

- 如走线空间不足,可考虑走内层VCC层,若不能走VCC层就走GND层,但走线要短。

下图10 是多层板Layout各层别的规划参考,并标识了高速、低速和EMC优先走线层别。

![]()

-

孔的类别:

![]()

Layout线路用到的孔有上图所示的三种。

- 通孔: 为贯穿整个板子用于连接各层线路的导通孔,为最常用孔。

优点是制板成本低;缺点是较浪费走线空间。

内径可选的最小值与板厚和板厂制程能力有关,1.6mm的板厚建议孔最小内径用10mil。

信号线最好选择可用的最小内径孔,而大电流线最好选择16mil/28mil的孔。

常见通孔尺寸有: 8mil/16mil(内径/外径)、10mil/20mil、12mil/22mil,16mil/28mil, - 盲孔:用于多层板,为连接板子最上两层或最下两层的线路。

优点是可增加走线、布局空间;缺点是制板成本高。 - 埋孔:用于多层板,为连接板子内层走线。

优点是可增加走线、布局空间;缺点是制板成本高。

- 通孔: 为贯穿整个板子用于连接各层线路的导通孔,为最常用孔。

-

接地:Layout接地一般分浮点接地、单点接地和多点接地;

- 浮点接地:多应用于测量仪器、医学仪器等。

优点是使设备和外壳绝缘,外壳感应杂讯不导入电路;

缺点是 设备与外壳 要保持 绝缘阻抗在1M以上,对大系统及高频线路不易达到.

若系统感应高电压,因无法接地By pass,可能对操作者会产生危险。

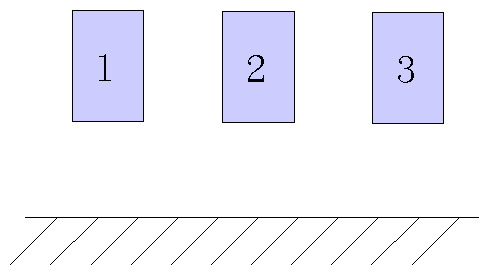

浮点接地如下图12

![]()

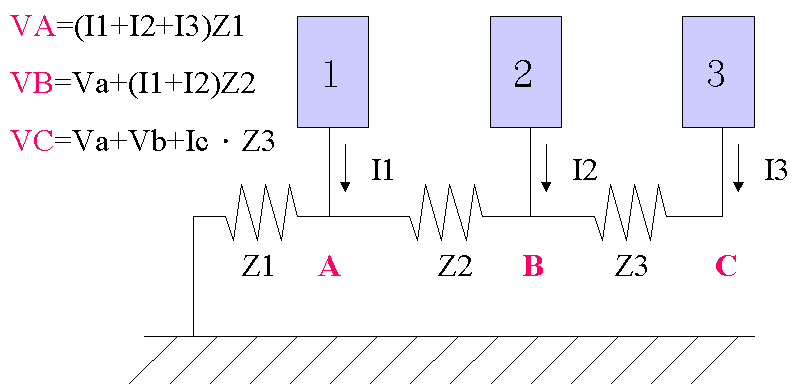

- 单点接地(串接):多应用于低频电路(0-30KHz)。

优点是最经济;

缺点是导入的杂讯最多,有电压降的问题。

单点接地串接法如下图13所示。

![]()

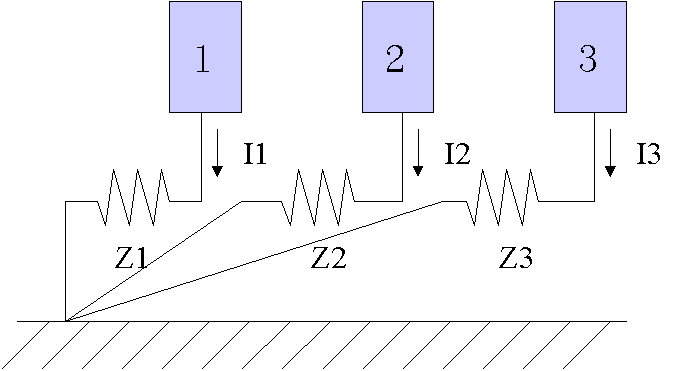

- 单点接地(并接):多应用于低频电路(0-300KHz)。

优点是可避免串接时所造成接地电压降的问题;

缺点是使接地线配长度增加。单点接地并接法如下图14所示。

![]()

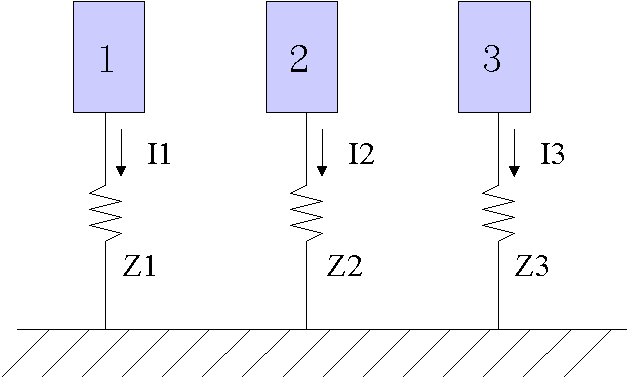

- 多点接地:多应用于多层板电路和高频电路。

优点是接地的导线短,减少R、L的阻抗,各部分电路连接到最近的阻抗地;

缺点是制造成本高。多点接地法如下图15所示

![]()

- 浮点接地:多应用于测量仪器、医学仪器等。

浙公网安备 33010602011771号

浙公网安备 33010602011771号