Gate-All-Around MOSFETs based on Vertically Stacked Horizontal Si Nanowires in a Replacement Metal Gate Process on Bulk Si Substrates

Abstract

8nm直径垂直堆叠的Si 纳米线,通过RMG(Replacement Metal Gate)工艺在体硅上生长,短沟道特性非常好(SS=65mV/dec,DIBL=42mV/V当LG=24nm),Si 纳米线下的寄生沟道通过GP(Ground Plane)得到了有效抑制

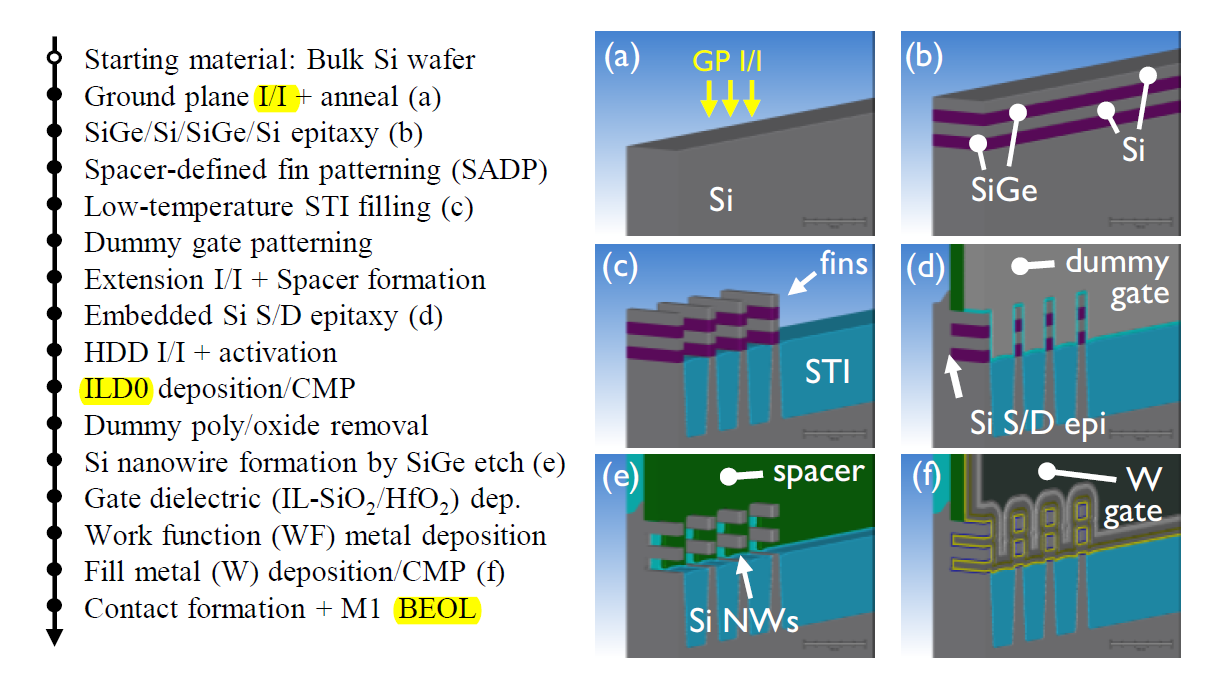

1.以体硅进行生长

2.GP

3.SiGe/Si/SiGe/Si外延,主要是为了之后通过刻蚀SiGe来形成Si纳米线

4.低温STI填充,制造短沟道隔离

5.栅牺牲层形成

6.Spacer隔离层的形成

7.源漏外延嵌入

8.HDD高掺杂注入激活

9.ILD0淀积/CMP

10.栅牺牲层的移除

11.对应于第3步,通过刻蚀SiGe来形成Si纳米线

12.栅介质的淀积(SiO2/HfO2),其中SiO2为了分压,因为HfO2是High-K介质,不耐压,而HfO2则是为了通过提升栅氧化层电容,从而增强栅对沟道的控制能力

13.WF金属淀积,主要是为了对单个栅进行导电

14.W淀积/CMP,主要是为了能对所有的栅进行控制

15.接触形成+M1 BEOL

浙公网安备 33010602011771号

浙公网安备 33010602011771号