FPGA_DDR3(2-2)

在上一篇博文中,写的比较乱,也确实是乱,因为我是这样走过来的,那是我的基本劳动经历。上一篇博文的结果我得到了教程的结果,也许是我不够聪明,我还是拿到了一堆的信号时序图,但我竟然不知道我要啥信号。

下一步,我想起我手里有点灰的AX545的开发板,这上面有DDR3,试一下吧,然后按照黑金Spartan-6开发板Verilog教程,以及DDR3的Demo测试代码,(这里就不上传手册和代码了,毕竟这是人家的劳动成果),只能说,网上有的地方有,自己找找可以找到的。

毕竟是公司型的指导手册,很快我就把工程建立起来,并且用ChipScope抓到了波形。

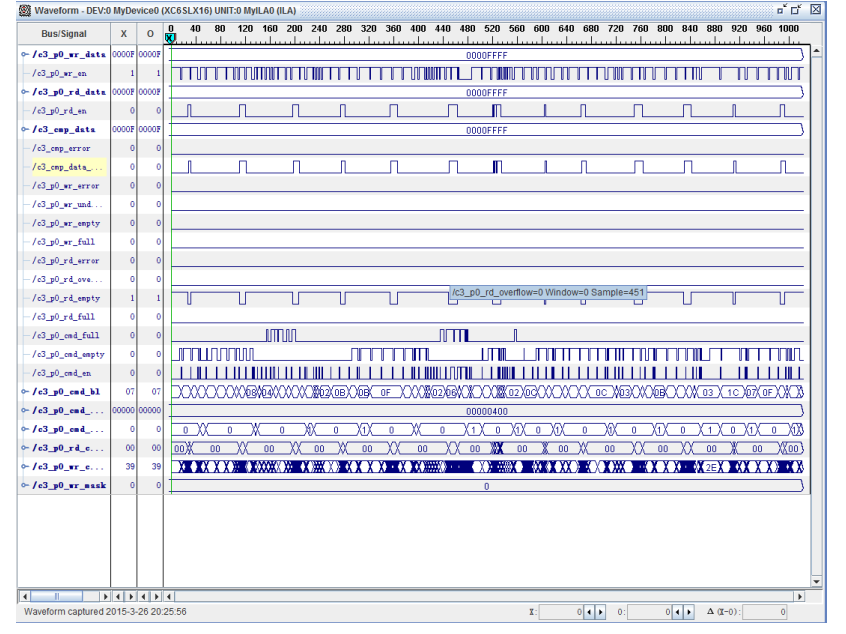

波形图,这里就摘个图,就是例程的最终的效果图。

好吧,其实到这里,我还是没明白我要的信号在哪里,我感觉是下面两个原因。

1.我这两天接触的代码有点多

2.DDR3的测试代码,全是软件自带的,包括仿真文件、引脚约束文件等等,做完一堆后,得到了以为正确的结果,其实自己啥都不知道。

3.不明白DDR3或者MIG的驱动本质

然后,没法了,直接猛读了两篇文章。

链接:https://pan.baidu.com/s/1LXWCdCkbQ3VAL60c7moSwA

提取码:pzcu

这两篇Xilinx的文档,好好读读,读完什么你就什么都明白了,关于那个什么app_X那一堆信号在另一个文档里面,那个文档我用不到也没去读,这里就不给链接了。

读完就知道了,MIG(Memory Interface Solution)具体的东西了

1.MIG的配置参数的具体意义

2.DDR3控制器接口信号的物理含义

3.MIG的控制接口以及含义

4.MIG的时钟配置

5.MIG的FIFO控制机制

6.MIG的强大,那真的是6端口32bit访问控制,自带仲裁,不失为一个数据交互中心,因为一般的SRAM控制器接口,物理上的就一个,某些FPGA内置的也就3端口还是1写2读(或者2个个双向)

7.你也会明白为啥网络上的教程都是用的C3,文档里写得清清楚楚的。

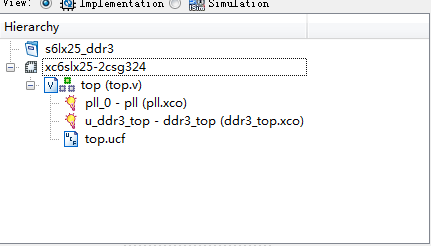

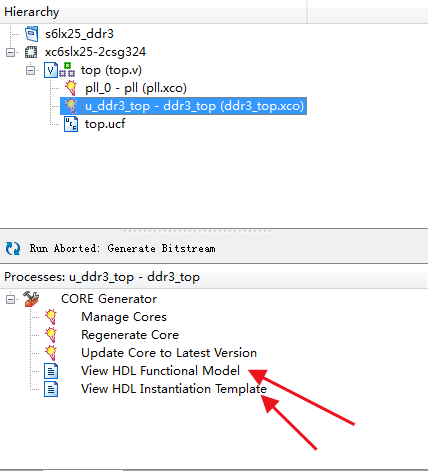

写到这里。还有一个就是xco文件的IP例化 和 直接使用 ISE Design Suite 64 Bit Command Prompt生成的ISE工程的区别,这个我也没明白,且看两个工程目录。

1.利用新建工程,然后,用一个.v文件去例化

下图中的两个小箭头能帮助你例化

ISE中,每个IP核的例化都可以这样,然后再控制

这些信号线皆可以实现你要的读写功能(按照UG388的读写控制时序)

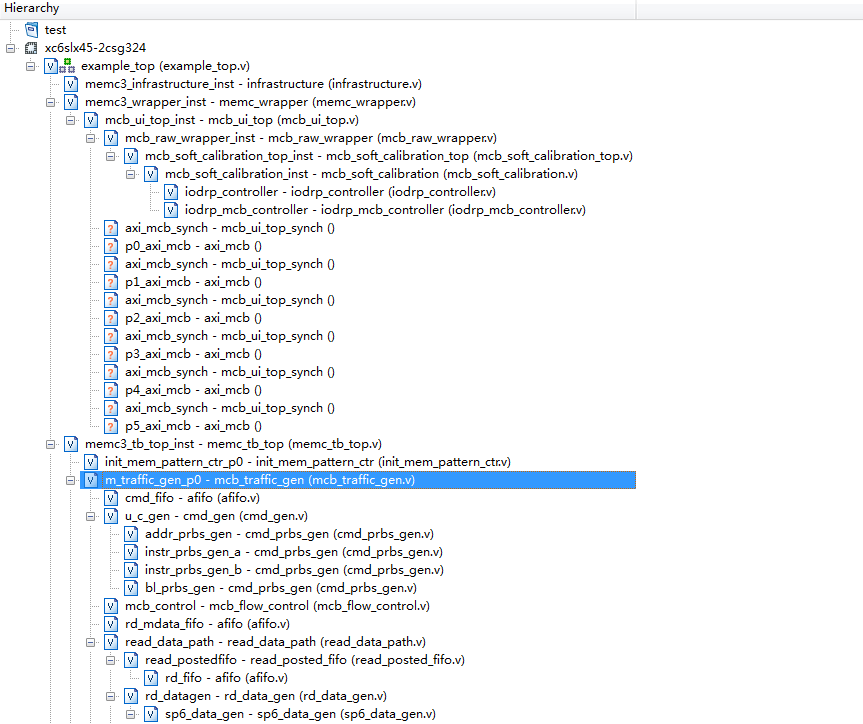

2.这个工程目录是直接按照AX545开发板带的教程生成的

这个本意是想展开全部,然后截个图,然后太多,根本截图不完,在这里就意思意思一下,这个工程应该是涵盖了控制信号线的逻辑(fifo控制),但是我确实是没找到MIG在哪里,脑壳痛。

最后,我并没有使用这个DDR3的MIG,或者说,并没有使用DDR3作为我的RAM,而是采用的IS61WV25616BLL-10TLISRAM存储器这个普通的SRAM,原因有二

1.这个代码以及电路是现成的

2.DDR3的MIG的FIFO控制以及读写,我觉得并不适合我这个产品,我的理解是太麻烦以及时效性。

浙公网安备 33010602011771号

浙公网安备 33010602011771号