零散学FPGA——D触发器

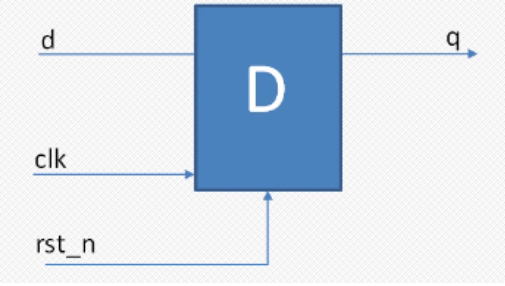

D触发器的结构

D触发器的原理

当rst_n为1时,q为0;

当rst_n为0时,q为d的值,且仅当时钟上升沿时q值才发生变化。

D触发器的VHDL代码

实现源码

1 library IEEE; 2 use IEEE.STD_LOGIC_1164.ALL; 3 4 5 6 entity Dflipflop is 7 port( clk: in bit; 8 p: in bit; 9 rst_n: in bit; 10 q: out bit 11 ); 12 end Dflipflop; 13 14 architecture Behavioral of Dflipflop is 15 16 begin 17 process(rst_n,clk) 18 begin 19 if rst_n='1' then 20 q<='0'; 21 elsif clk' event and clk='1' then 22 q<=p; 23 end if; 24 end process; 25 end Behavioral;

testbench

1 LIBRARY ieee; 2 USE ieee.std_logic_1164.ALL; 3 4 -- Uncomment the following library declaration if using 5 -- arithmetic functions with Signed or Unsigned values 6 --USE ieee.numeric_std.ALL; 7 8 ENTITY Dflipfloptestbench IS 9 END Dflipfloptestbench; 10 11 ARCHITECTURE behavior OF Dflipfloptestbench IS 12 13 -- Component Declaration for the Unit Under Test (UUT) 14 15 COMPONENT Dflipflop 16 PORT( 17 clk : IN bit; 18 p : IN bit; 19 rst_n : IN bit; 20 q : OUT bit 21 ); 22 END COMPONENT; 23 24 25 --Inputs 26 signal clk : bit := '0'; 27 signal p : bit := '0'; 28 signal rst_n : bit := '0'; 29 30 --Outputs 31 signal q : bit; 32 33 -- Clock period definitions 34 constant clk_period : time := 10 ns; 35 36 BEGIN 37 38 -- Instantiate the Unit Under Test (UUT) 39 uut: Dflipflop PORT MAP ( 40 clk => clk, 41 p => p, 42 rst_n => rst_n, 43 q => q 44 ); 45 46 -- Clock process definitions 47 clk_process :process 48 begin 49 clk <= '0'; 50 wait for clk_period/2; 51 clk <= '1'; 52 wait for clk_period/2; 53 end process; 54 55 56 -- Stimulus process 57 stim_proc: process 58 begin 59 -- hold reset state for 100 ns. 60 wait for clk_period/2; 61 p<='0'; 62 wait for clk_period; 63 p<='1'; 64 wait for clk_period; 65 p<='0'; 66 wait for clk_period; 67 p<='1'; 68 wait for clk_period; 69 p<='0'; 70 wait for clk_period; 71 p<='1'; 72 wait for clk_period; 73 p<='0'; 74 wait for clk_period; 75 p<='1'; 76 wait for clk_period; 77 p<='0'; 78 wait for clk_period; 79 p<='1'; 80 wait for clk_period; 81 82 83 -- insert stimulus here 84 85 wait; 86 end process; 87 88 END;

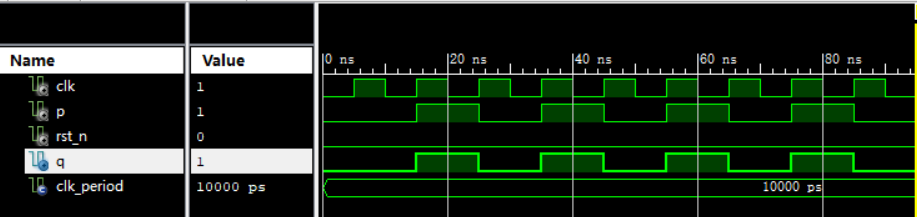

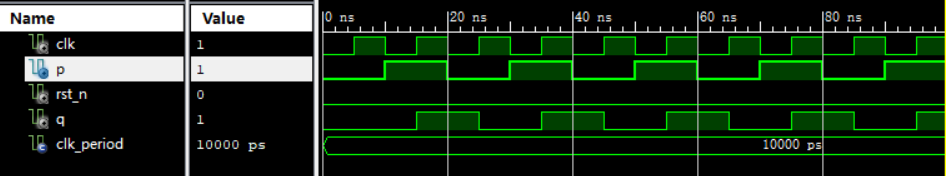

仿真波形

当无延迟时的波形

可以看出第二张图片中的曲线发生了延迟

第一张图片中当发生上升沿时,p已经发生了变化,因此没有曲线延迟的现象。

VHDL语法学习

1.event 表示某个事件发生了,但是必须在后面附加上发生的事件是什么。比如clk'event and clk=1'表示时钟的上升沿,clk'event and clk=0'表示时钟的下降沿。

2.并行与顺序

在结构体(architecture)里的语句并行处理;在process、function和procedure里的语句顺序处理;但是每个process等是并行处理的。

?问题:architecture里的语句真的是一起执行部分先后顺序吗?能不能理解成为同时执行的门电路?

3.process表示进程,process (rst,clk)括号中的数据表示进程的输入数据,可以实现多进程间的信息传输

?问题:进程数据的输入方式不是分很多种吗,这种属于哪一类?

浙公网安备 33010602011771号

浙公网安备 33010602011771号