多路选择器,加法器原理及verilog实现

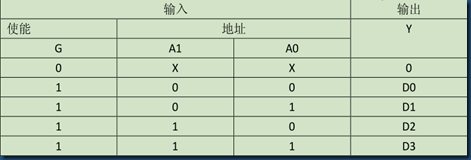

1.数据选择器是指经过选择,把多个通道的数据传到唯一的公共数据通道上。实现数据选择功能的逻辑电路称为数据选择器,它的作用相当于多个输入的单刀多掷开关。本例程以四选一数据选择器(电平触发)为例。 四选一数据选择器书堆 4 个数据源进行选择, 使用量为地址 A1A0 产生 4 个地址信号,由 A1A0 等于“00” 、 “01” 、 “10” 、 “11”来选择输出,真值表如下:

module mux4(d0,d1,d2,d3,y,a,g); input d0,d1,d2,d3; // 输入的四个数据 input g; // 输入使能端 input[1:0] a; // 输入的选择端 output y; // 输出数据 reg y; // 输出数据寄存器 always@(d0 or d1 or d2 or d3 or g or a) // 电平触发,当 d0,d1,d2,d3,a 有变化时 候、// 触发 begin if(g==1'b0) //当 当 g 为 为 0 时候 y=1'b0; //y 置 置 0 else case(a) // 判断 a 的取值,并作出相应的赋值 2'b00:y=d0; 2'b01:y=d1; 2'b10:y=d2; 2'b11:y=d3; default:y=1'b0; //a 为其他值得条件下,y 赋予 0 endcase end endmodule

时序仿真结果:

2.加法器是一种较为常见的算术运算电路,包括半加器(对两个输入数据相加,输出一个结果位和进位,没有进位输入的电路),全加器(有进位输入)。

如题,实现一个四位全加器:

module add4(a,b,ci,s,co); input [3:0] a,b; // 输入四位数据 a ,b input ci; // 输入进位 ci output [3:0] s; // 输出四位数据 s output co; // 输出进位 co assign {co,s}=a+b+ci; //把 把 a 、b 、ci 相加后的结果赋予 co 、s ,其中 co // 放最高位,s 放低三位 endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号