GPIO-FPGA架构

GPIO是一种软件运行期间能够动态配置和控制的通用引脚

有不同的GPIObank,每个GPIO口的bank都会有编号的区分,

每个GPIO口除了通用的输入输出功能以外,还有其他复用功能,例如GPIO5_b4可以复用成:

- spi0_clk

- ts0_data4

- uart4exp_ctsn

一、GPIO的特性

1.可编程控制GPIO中断

2.可边沿触发或者电平触发

3输入输出可承受5V

4读写过程中通过位地址线进行位屏蔽

5弱上拉和若下拉电阻

6.2、4/8mA驱动,以及带驱动转换速率skew rate()的8没A驱动

7开漏使能,数字输入使能

二、GPIO的工作模式

1.高阻输入

实际上就是一个带有施密特触发输入的三态缓冲器(U1)高的输入阻抗,施密特触发输入的作用就是将缓慢变化,或是畸变的输入脉冲信号整形成理想的矩形脉冲信号。读脉冲信号把当前的电平状态读出到内部总线上,不执行读操作的时候,外部管脚和内部总线隔离。

2.推挽输出

这里的推挽主要指的是T1 和T2组成的反相器部分,T1或者T2导通的时候,都具有低的阻抗,但是T1T2不会同时导通,或者同时关闭,这样形成的就是推挽输出。在实际的开发板上,T1T2实际上是多组可编程选通的晶体管,驱动能力可以自行配置为各种电流输出的。GPIO还有回读的功能,实现回读功能的实际上是一个简单的三态门U2,回读到的是管教的输出缓存状态,不是外部管脚的状态。

U17.com是输出缓存器,在执行GPIO管教的写操作的时候,在写脉冲的作用下,数据被锁存到Q和Q1。

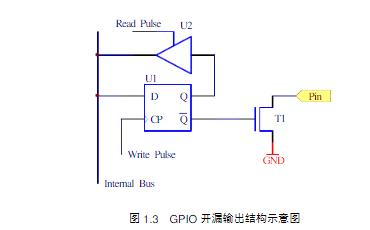

3.开漏输出

开漏输出的结果与推挽输出类似,GPIO管脚在开漏输出下的等效结构模式图,,实际上就是一个开关,输出1时断开,输出0时接到地上,(有一定的内阻)。回读的时候读到的仍然是输出锁存器的状态,而不是外部管脚的pin状态。开漏输出不能用于输入。

实际用用的时候要加上上拉电阻,开漏输出可以方便的实现线与逻辑,另外他可以实现不同逻辑电平之间的转换,只需要接一个上拉电阻,不需要额外的转换电路。典型的应用例子就是基于OD的IIC总线。

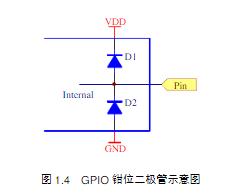

4.钳位二极管

作用在于防止外部管脚Pin的输入电压过高或者过低,VDD的正常供电电压是3.3V,如果从pin输入信号电压超过VDD加上二极管D1的导通压降假定0.6V(),着二极管D1导通,会把多余的电流引入到VDD,而真正输入到内部的信号不会超过3.9V,同理,D2可以限制输入电压的最小值,使之不超过-0.6V 。

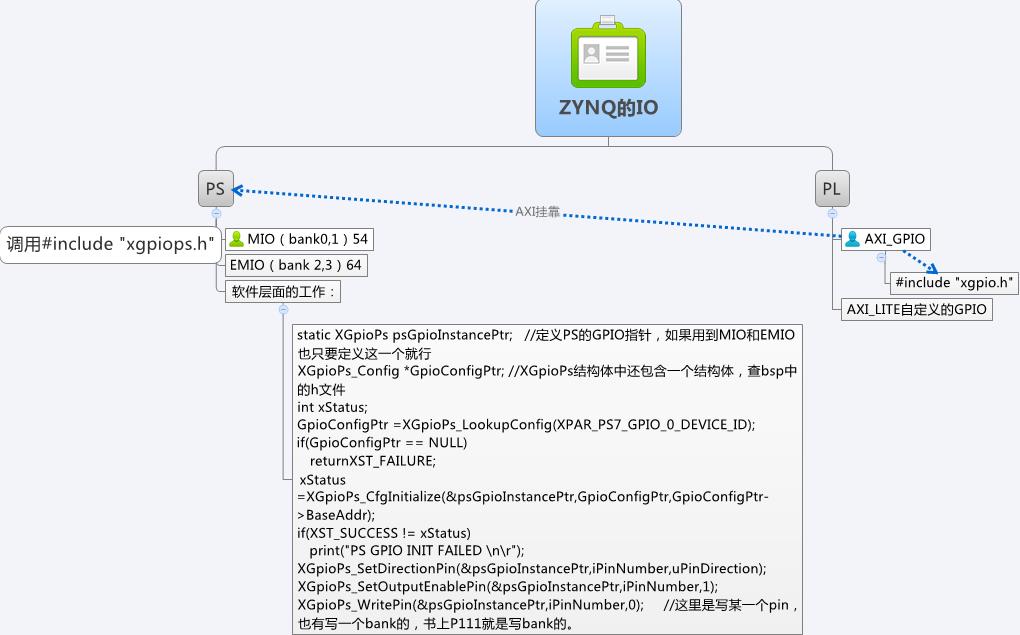

另外,加上一个ZYNQ的IO的用法:

附加一个树莓配的GPIO配置方法:https://blog.csdn.net/xukai871105/article/details/12684617

posted on 2018-08-24 17:18 super_star123 阅读(3251) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号