门控时钟

功耗管理是一个至关重要的设计目标。随着芯片集成度的提高和应用场景的多样化,如何有效地降低功耗成为设计工程师面临的主要挑战之一。功耗主要分为动态功耗和静态功耗,其中动态功耗由时钟信号引起的晶体管开关活动占据了相当大的比例。

门控时钟(Clock Gating)技术作为一种有效的动态功耗优化手段,已经广泛应用于各种数字电路设计中。其基本原理是通过控制时钟信号的传输,减少电路中无用的时钟切换活动,从而降低功耗。这种技术通过在电路中插入门控单元,根据特定条件开启或关闭时钟信号,来实现对时钟资源的精细管理。

在复杂的系统芯片(SoC)设计中,门控时钟不仅可以显著降低功耗,还能改善芯片的热性能和电源管理效率。这种方法尤其适用于需要频繁进入低功耗模式的移动设备、嵌入式系统和电池供电设备。

例子

例如,在ara向量处理器中,门控时钟技术被手动应用于向量寄存器文件(VRF)和定点乘法及浮点单元(vmfpu)。在这些模块中,只有在需要时才会启用时钟。

在 vmfpu 中的应用

在vmfpu模块中,当没有接收到新的指令且没有指令在执行时,时钟会被关闭以节省功耗。以下是相关的Verilog代码示例:

// vmfpu.sv

tc_clk_gating i_simd_mul_manual_clk_gate (

.clk_i (clk_i ),

.en_i (clkgate_en_q),

.test_en_i (1'b0 ),

.clk_o (clk_i_gated )

);

assign clkgate_en_d = vinsn_processing_d_valid & (vinsn_processing_d.op inside {[VMUL:VSMUL]});

在 vector_regfile 中的应用

在vector_regfile模块中,当对当前bank(一个lane包含8个bank)没有请求时,会关闭SRAM的时钟。这段代码实现了在没有请求时对时钟的门控:

// vector_regfile.sv

`FF(sram_active_q, req_i[bank], 1'b0)

tc_clk_gating i_vrf_ckg (

.clk_i (clk_i ),

.test_en_i(1'b0 ),

.en_i (req_i[bank] || sram_active_q),

.clk_o (vrf_clk )

);

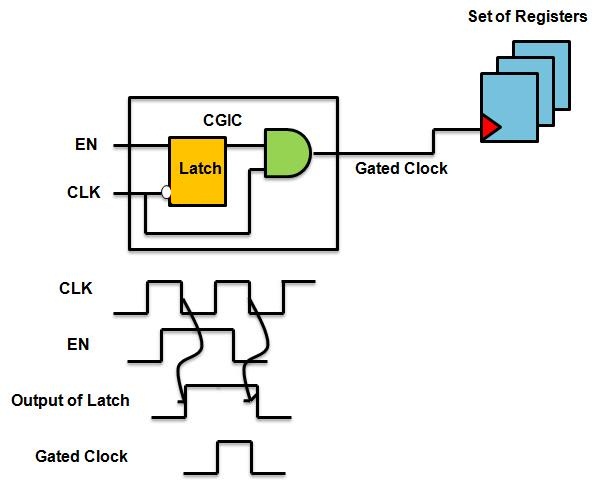

门控时钟单元(ICG)的结构

典型的门控时钟单元(ICG)的内部结构通过一个低电平有效的锁存器对EN信号进行锁存,然后再与CLK信号进行逻辑与操作,以避免毛刺。以下是ICG模块的Verilog实现:

module tc_clk_gating #(

parameter bit IS_FUNCTIONAL = 1'b1

)(

input logic clk_i,

input logic en_i,

input logic test_en_i,

output logic clk_o

);

logic clk_en;

always_latch begin

if (clk_i == 1'b0) clk_en <= en_i | test_en_i;

end

assign clk_o = clk_i & clk_en;

endmodule

图片来源:VLSI-SOC Blog

浙公网安备 33010602011771号

浙公网安备 33010602011771号