使用FPGA开发板驱动VGA显示器

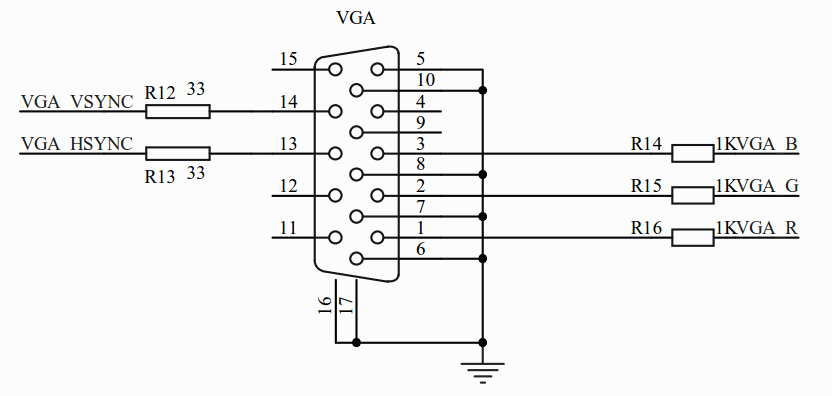

1. 本次使用的是cyclone4开发板,先看下原理图,因为右边的RGB应该是模拟信号量,但是本次例程只接了3根线,那就是说颜色只有8种。

2. 代码,输出信号有R,G,B三色,就是上图右边的,行同步信号(扫描完一行),场同步信号。VGA收发双方没有时钟信号做同步,但是通常会约定发送方有一个基本的时钟,行同步信号HSYNC在每行开始的时候产生一个固定宽度的高脉冲。场同步信号VSYNC在每帧(即一次全屏的图像)开始的时候产生一个固定宽度的高脉冲。我对关键的信号,画了时序图,发现不是很理解程序的机制。

module VGA( clock, switch, disp_RGB, hsync, vsync ); input clock; //系统输入时钟 50MHz input [1:0]switch; output [2:0]disp_RGB; //VGA数据输出 output hsync; //VGA行同步信号 output vsync; //VGA场同步信号 reg [9:0] hcount; //VGA行扫描计数器 reg [9:0] vcount; //VGA场扫描计数器 reg [2:0] data; reg [2:0] h_dat; reg [2:0] v_dat; //reg [9:0] timer; reg flag; wire hcount_ov; wire vcount_ov; wire dat_act; wire hsync; wire vsync; reg vga_clk; //VGA行、场扫描时序参数表 parameter hsync_end = 10'd95, hdat_begin = 10'd143, hdat_end = 10'd783, hpixel_end = 10'd799, vsync_end = 10'd1, vdat_begin = 10'd34, vdat_end = 10'd514, vline_end = 10'd524; always @(posedge clock) begin vga_clk = ~vga_clk; end //************************VGA驱动部分******************************* //行扫描 always @(posedge vga_clk) begin if (hcount_ov) hcount <= 10'd0; else hcount <= hcount + 10'd1; end assign hcount_ov = (hcount == hpixel_end); //场扫描 always @(posedge vga_clk) begin if (hcount_ov) begin if (vcount_ov) vcount <= 10'd0; else vcount <= vcount + 10'd1; end end assign vcount_ov = (vcount == vline_end); //数据、同步信号输 assign dat_act = ((hcount >= hdat_begin) && (hcount < hdat_end)) && ((vcount >= vdat_begin) && (vcount < vdat_end)); assign hsync = (hcount > hsync_end); assign vsync = (vcount > vsync_end); assign disp_RGB = (dat_act) ? data : 3'h00; //************************显示数据处理部分******************************* //图片显示延时计数器 /*always @(posedge vga_clk) begin flag <= vcount_ov; if(vcount_ov && ~flag) timer <= timer + 1'b1; end */ always @(posedge vga_clk) begin case(switch[1:0]) 2'd0: data <= h_dat; //选择横彩条 2'd1: data <= v_dat; //选择竖彩条 2'd2: data <= (v_dat ^ h_dat); //产生棋盘格 2'd3: data <= (v_dat ~^ h_dat); //产生棋盘格 endcase end always @(posedge vga_clk) //产生竖彩条 begin if(hcount < 223) v_dat <= 3'h7; //白 else if(hcount < 303) v_dat <= 3'h6; //黄 else if(hcount < 383) v_dat <= 3'h5; //青 else if(hcount < 463) v_dat <= 3'h4; //绿 else if(hcount < 543) v_dat <= 3'h3; //紫 else if(hcount < 623) v_dat <= 3'h2; //红 else if(hcount < 703) v_dat <= 3'h1; //蓝 else v_dat <= 3'h0; //黑 end always @(posedge vga_clk) //产生横彩条 begin if(vcount < 94) h_dat <= 3'h7; //白 else if(vcount < 154) h_dat <= 3'h6; //黄 else if(vcount < 214) h_dat <= 3'h5; //青 else if(vcount < 274) h_dat <= 3'h4; //绿 else if(vcount < 334) h_dat <= 3'h3; //紫 else if(vcount < 394) h_dat <= 3'h2; //红 else if(vcount < 454) h_dat <= 3'h1; //蓝 else h_dat <= 3'h0; //黑 end endmodule

3. 用quartus软件综合一下工程,烧写,插上显示器的VGA接口,可以看到显示器显示的8种颜色。

浙公网安备 33010602011771号

浙公网安备 33010602011771号