Rockchip RK3399 - ALC5651 & I2S基础

----------------------------------------------------------------------------------------------------------------------------

开发板 :NanoPC-T4开发板

eMMC :16GB

LPDDR3 :4GB

显示屏 :15.6英寸HDMI接口显示屏

u-boot :2023.04

linux :6.3

----------------------------------------------------------------------------------------------------------------------------

一、声音信号的数字化

我们应该都知道,声音是一种模拟信号,如果想用于计算机,就必须要将模拟信号转换为数字信号,这样,我们就能在计算机上存储声音了,等待用户想播放的时候,再将数字信号转换为模拟信号。声音的数字化需要经历三个阶段:采样、量化、编码。

1.1 采样

采样是把时间上连续的模拟信号在时间轴上离散化的过程,这里有采样频率和采样周期的概念,采样周期即相邻两个采样点的时间间隔,采样频率是采样周期的倒数。示意图如下图所示:

蓝色代表模拟音频信号,红色的点代表采样得到的量化数值。采样频率越高,红色的间隔就越密集,记录这一段音频信号所用的数据量就越大,同时音频质量也就越高。

根据奈奎斯特理论,采样频率只要不低于音频信号最高频率的两倍,就可以无损失地还原原始的声音。通常人耳能听到频率范围大约在20Hz~20kHz之间的声音,为了保证声音不失真,采样频率应在40kHz以上。

常用的采样率有:

- 8kHz:电话所用采样率,对于人的说话已经足够;

- 11.025 kHz:AM调幅广播所用采样率;

- 22.05kHz和24kHz:FM调频广播的采样率;

- 32kHz:miniDV数码视频、DAT所用采样率;

- 44.1kHz:音频CD、也常用于MPEG-1音频(VCD、SVCD、MP3)所用采样率;也是现一般的专业设备的采样频率为;

- 47.25kHz :商用 PCM 录音机所用采样率;

- 48kHz:miniDV、数字电视、DVD、DAT、电影专业音频所使用的数字声音所用采样率;

- 50kHZ:商用数字录音机所用采样率;

- 96kHz或者192kHz:DVD-Audio、一些 LPCM DVD 音轨、BD-ROM(蓝光盘)音轨、和 HD-DVD (高清晰度 DVD)音轨所用所用采样率;

1.2 量化

1.2.1 位深度

位深度,也叫位宽,量化精度,上图中,每一个红色的采样点,都需要用一个数值来表示大小,这个数值的数据类型大小可以是:4bit、8bit、16bit、32bit等等,位数越多,表示得就越精细,声音质量自然就越好,当然,数据量也会成倍增大。常见的位宽有:8bit或者16bit。

1.2.2 声道数

由于音频的采集和播放是可以叠加的,因此,可以同时从多个音频源采集声音,并分别输出到不同的扬声器,故声道数一般表示声音录制时的音源数量或回放时相应的扬声器数量。单声道(Mono)和双声道(Stereo)比较常见,顾名思义,前者的声道数为1,后者为2。

1.3 编码

编码是整个声音数字化的最后一步,其实声音模拟信号经过采样,量化之后已经变为了数字形式,但是为了方便计算机的储存和处理,我们需要对它进行编码,以减少数据量。常见的音频编码格式有PCM、PDM。

通过采样频率和精度可以计算声音的数据传输率:数据传输率(bps) = 采样频率 × 量化位数 × 声道数。

有了数据传输率我们就可以计算声音信号的数据量:数据量(byte)= 数据传输率 * 持续时间 / 8。

例如:CD唱片上所存储的立体声高保真音乐的采样频率为44.1kHZ,量化精度为16位,双声道,计算一小时的数据量:根据公式:

$$ 44.1kHZ * 16bit * 2 * 3600s /8 =6350400B ≈ 605.6MB$$

看看这个数字,是非常大的了,所以,在编码的时候常常使用压缩的方式来减少储存空调提高传输效率。

1.3.1 PCM编码

PCM (Pulse Code Modulation) 是通过等时间隔(即采样率时钟周期)采样将模拟信号数字化的方法。

PCM使用等间隔采样方法,将每次采样的模拟分量幅度表示为N位的数字分量(N = 量化位数),因此PCM方式每次采样的结果都是N bit长的数据。

1.3.2 PDM编码

PDM(Pulse Density Modulation)是一种用数字信号表示模拟信号的调制方法,同为将模拟量转换为数字量的方法。

PDM使用远高于PCM采样率的时钟采样调制模拟分量,只有1位输出,要么为0,要么为1。因此通过PDM方式表示的数字音频也被称为Oversampled 1-bit Audio。

相比PDM一连串的0和1,PCM的量化结果更为直观简单。

注意:如果你学过SPWM、SVPWM的话,这种脉冲宽度调试方式就很容易理解。

1.4 数字音频接口(DAI)

数字音频接口全部是硬件接口,是实实在在的物理连线方式,即同一个PCB板上IC芯片和IC芯片之间的通讯协议。和音频编码格式完全是两回事。

数字音频接口有PCM、I2S、AC97、PDM;

- I2S和PCM(TDM)接口传输的数据是PCM编码格式的音频数据;

- PDM接口传输的数据是PDM编码格式的音频数据;

为直观的展示,下图简单列举了数字音频接口硬件接线的一般场景,图中AP指的应用处理器。

1.4.1 I2S总线

I2S总线是一种数字音频数据传输的串行连接,在系统中用于设备之间的音频数据传输,由飞利浦半导体发明,现在被许多半导体厂商广泛使用。

用I2S总线的设备有ADC、DAC、DSP、CPU等。使用I2S接口,我们可以将音频设备和嵌入式SoC平台连接在一起,为系统提供音频接口解决方案。

和 I2C、 SPI 这些常见的通信协议一样, I2S 总线用于主控制器和音频 CODEC 芯片之间传输音频数据。I2S 接口需要3根信号线(如果需要实现收和发,那么就要 4 根信号线,收和发分别使用一根信号线):

- SCLK:串行时钟信号,也叫位时钟(BCLK),音频数据的每一位数据都对应一个SCLK,立体声都是双声道的,因此SLCK=2×采样率×采样位数;比如采样频率为44.1KHz、 16位的立体声音频,那么SCK=2×44100×16=1411200Hz=1.4112MHz;

- WS:声道选择信号,也叫做帧时钟(LRCK),用于切换左右声道数据,为1表示正在传输左声道的数据,为0表示正在传输右声道的数据;WS的频率等于采样频率,比如采样率为44.1KHz的音频,WS=44.1KHz;

- SD:串行数据信号,也就是实际的音频数据,若要同时实现放音和录音,就需要2根数据线;比如WM8960的ADCDAT和DACDAT,就是分别用于录音和放音;

BCLK和LRCK外,可能还需要控制器为编解码芯片提供系统系统时钟MCLK(Master/System clock input),这是由CODEC内部基于Delta-Sigma (ΔΣ)的架构设计要求使然,其主要原因是因为这类的CODEC没有所谓提供芯片的工作时钟晶振电路。如果使用MCLK时钟的话,MCLK时钟频率一般为采样频率的256倍或384倍,具体参考特定器件手册。

当然MCLK也不是必须的,以ALC5651为例它可以使用BLCK1/2作为内部PLL的时钟源,从而为ALC5651提供时钟。

在I2S总线上,只能同时存在一个主设备和发送设备。主设备可以是发送设备,也可以是接收设备,或是协调发送设备和接收设备的其它控制设备。在I2S系统中,提供时钟(SCLK和WS)的设备为主设备。

特点:效率高;主要传输音乐;传输PCM编码后的音频数据。

根据SDATA相对于SCLK和LRCK位置的不同,I2S分为三种不同的工作模式,分别为标准I2S模式、左对齐模式和右对齐模式。

1.4.2 PCM/TDM总线

PCM总线包括4根信号:

- PCM_CLK:数据时钟信号;

- PCM_SYNC:帧同步时钟信号;

- PCM_IN:接收数据信号;

- PCM_OUT:发送数据信号;

和I2S接口差不多,PCM接口是4根信号线,通常用于AP处理器和通信MODEM之间传输语音数据(就是双向打电话的数据)。

AP处理器和蓝牙之间也是通过PCM来传输语音数据,打电话的蓝牙数据走的是PCM,放音乐的蓝牙数据走的是串口(不是PCM)。

特点:效率高,多达16路数据;主要传输音乐;传输PCM编码后的音频数据。

I2S只能传2个声道的数据,PCM可以传多达16路数据,采用时分复用的方式,就是TDM(Time Division Multiplexing)。

1.4.3 PDM总线

PDM总线只有两根信号线:

- PDM_CLK:时钟信号;

- PDM_DATA :数据信号;

特点:信号线数量少,只需两根;多用于传输麦克风录音;传输的是PDM编码后的音频数据(不同于I2S接口和PCM接口)。

在数字麦克风领域,应用最广的就是PDM接口,其次为I2S接口。

PDM在诸如手机和平板等对于空间限制严格的场合有着广泛的应用前景。

二、RK3399 I2S

我们翻看RK3399 datasheep第22章,可以看到I2S/PCM控制器相关的介绍,这里我们只是粗略的介绍一下RK3399有关的特性。

2.1 概括

I2S/PCM控制器不仅支持I2S模式,还支持PCM模式环绕音频输出和立体声输入。设计中嵌入了三个I2S/PCM控制器,分别是I2S0、I2S1和I2S2。它们之间的不同特点如下:

- I2S0支持八个内部32位宽、32个位深的FIFO(先进先出队列),其中四个用于传输音频数据,四个用于接收音频数据;

- I2S1支持两个内部32位宽、32个位深的FIFO,一个用于传输音频数据,一个用于接收音频数据;

- I2S2支持四个内部32位宽、32个位深的FIFO,用于传输音频数据;

- 在I2S模式下,I2S0支持10通道音频数据传输和接收,I2S1支持2通道音频数据传输和2通道音频数据接收,I2S2支持8通道音频数据传输;

- I2S0和I2S1支持高达192kHz的采样率,I2S2支持高达768kHz的采样率;

- I2S2被内部连接到HDMI和显示端口,I2S0/I2S1被暴露到外设;

这三个控制器的共同特点如下:

- 支持AHB总线接口;

- 支持16~32位音频数据传输;

- 支持主从模式;

- PCM模式下支持2通道音频接收;

- Support DMA handshake interface and configurable DMA water level;

- Support transmit FIFO empty, underflow, receive FIFO full, overflow interrupt and all interrupts can be masked;

- Support configurable water level of transmit FIFO empty and receive FIFO full interrupt;

- 支持合并中断输出;

- PCM模式下支持2通道音频接收;

- 支持I2S正常、左对齐和右对齐模式的串行音频数据传输;

- 支持PCM提前、后延1、后延2、后延3模式的串行音频数据传输;

- 支持将16到31位的音频数据左对齐或右对齐存储在32位宽FIFO中;

- 支持两个16位音频数据存储在一个32位宽位置中;

- 支持2个独立的LRCK信号,一个用于接收,一个用于传输音频数据。如果采样率相同,则可以使用单个LRCK来传输和接收数据;

- 支持可配置的SCLK和LRCK极性;

2.2 功能框图

I2S/PCM控制器主要由以下6个模块组成;

- 系统接口:实现AHB从属操作,包括发送器和接收器内的控制寄存器、中断和DMA握手接口等;

- 时钟发生器:用于生成发送器和接收器所需的时钟信号。输入源时钟为MCLK_I2S,通过模块的分频器,时钟发生器生成SCLK和LRCK信号;

- 发送器:实现传输操作。发送器可以作为主设备或从设备运行,在I2S或PCM模式下,提供环绕立体声音频接口;

- 接收器:实现接收操作。接收器可以作为主设备或从设备运行,在I2S或PCM模式下,提供立体声音频串行接口;

- 传输FIFO:用于存储传输的音频数据。FIFO的大小为32位x32个位置;

- 接收FIFO:用于存储接收的音频数据。FIFO的大小为32位x32个位置;

这些组成部分一同构成了一个I2S/PCM控制器的完整功能。当主机需要进行音频数据传输或接收时,通过系统接口向I2S/PCM控制器发送数据,并通过传输或接收器的I2S/PCM接口完成音频数据传输或接收。

缓冲区FIFO用于缓存传输或接收的音频数据,以确保高效的数据处理和正确的数据传输。时钟发生器提供必要的时钟信号以保证数据传输操作的正确执行。

2.3 功能介绍

在I2S/PCM控制器中,有四种工作条件:

- 发送器-主设备 & 接收器-主设备;

- 发送器-主设备 & 接收器-从设备;

- 发送器-从设备 & 接收器-主设备;

- 发送器-从设备 & 接收器-从设备。

当发送器作为主设备时,它向接收器(从设备)发送所有信号,并由CPU控制何时向接收器发送时钟和数据。

当发送器作为从设备时,SD信号仍然从发送器发送到接收器,但SCLK和LRCK信号是由接收器(主设备)发送到发送器的。

根据三个接口规范,传输数据在发送器接收SCLK和LRCK信号之前应该准备好。CPU应该知道接收器何时初始化事务以及何时发送数据。

当接收器作为主设备时,它向发送器(从设备)发送SCLK和LRCK信号,并接收串行数据。因此,CPU必须告诉发送器何时开始事务以便它准备好传输数据,然后接收器开始传输并发送时钟和通道选择信号。

当接收器作为从设备时,CPU只需进行初始设置并等待所有信号,然后开始读取数据。

在传输或接收数据之前,CPU需要对I2S寄存器进行初始设置。这包括CPU设置、I2S接口寄存器设置以及可能的嵌入式SoC平台设置。这些寄存器必须在开始数据传输之前设置好。

2.4 I2S三种模式

I2S支持多种模式:标准模式、左对齐模式、右对齐模式。

2.4.1 标准模式

下图是I2S工作于标准模式的时序图:

(1) 对于LRCK(I2S_LRCK_RX/I2S_LRCK_TX)信号,当为低电平时是采样的左声道信号,为高电平时采样的是右声道信号;

(2) 对于SD(I2S_SDO、I2S_SDI)信号,,可以选择先传输最高有效位(MSB)或最低有效位(LSB),数据的传输是在LRCK信号发生变化之后的第一个SCLK时钟周期内开始的,每个SCLK时钟周期可以传输一位数据,SD信号的位宽可以在16到32位之间进行设置;

2.4.2 左对齐模式

下图是I2S工作于左对齐模式的时序图:

(1) 对于LRCK(I2S_LRCK_RX/I2S_LRCK_TX)信号,当为高电平时是采样的左声道信号,为低电平时采样的是右声道信号;

(2) 对于SD(I2S_SDO、I2S_SDI)信号,,可以选择先传输最高有效位(MSB)或最低有效位(LSB),数据的传输是在LRCK信号发生变化之后的第一个SCLK时钟周期内开始的,每个SCLK时钟周期可以传输一位数据,SD信号的位宽可以在16到32位之间进行设置;

2.4.3 右对齐模式

下图是I2S工作于右对齐模式的时序图:

(1) 对于LRCK(I2S_LRCK_RX/I2S_LRCK_TX)信号,当为高电平时是采样的左声道信号,为低电平时采样的是右声道信号;

(2) 对于SD(I2S_SDO、I2S_SDI)信号,在这种模式下,数据的传输顺序仍然可以选择先传输最高有效位(MSB)或最低有效位(LSB),而且SD信号的位宽也可以在16到32位之间进行设置。但是,这种模式下数据的对齐方式与普通或左对齐模式不同,它会将数据的最后一个位对齐到LRCK信号的边缘上。换句话说,在这种模式下,每个数据帧的起始边沿处,数据的位数与SD信号的位宽相等;而在普通或左对齐模式下,数据的起始边沿处则分别是第一个和最后一个数据位;

2.5 寄存器

下表描述了RK3399有关I2S/PCM控制器的寄存器信息:

| 名称 | 偏移 | 大小 | 复位值 | 描述 |

| I2S_TXCR | 0x0000 | W | 0x0000000f | 传输操作控制器寄存器 |

| I2S_RXCR | 0x0004 | W | 0x0000000f | 接收操作控制器寄存器 |

| I2S_CKR | 0x0008 | W | 0x00071f1f | 时钟发生寄存器 |

| I2S_TXFIFOLR | 0x000C | W | 0x00000000 | TX FIFO level寄存器 |

| I2S_DMACR | 0x0010 | W | 0x001f0000 | DMA控制寄存器 |

| I2S_INTCR | 0x0014 | W | 0x00000000 | 中断控制寄存器 |

| I2S_INTSR | 0x0018 | W | 0x00000000 | 中断状态寄存器 |

| I2S_XFER | 0x001C | W | 0x00000000 | I2S数据传输开始寄存器 |

| I2S_CLR | 0x0020 | W | 0x00000000 | SCLK域逻辑清除寄存器 |

| I2S_TXDR | 0x0024 | W | 0x00000000 | 传输FIFO数据寄存器 |

| I2S_RXDR | 0x0028 | W | 0x00000000 | 接收FIFO数据寄存器 |

| I2S_RXFIFOLR | 0x002C | W | 0x00000000 | RX FIFO level寄存器 |

其中:大小B表示字节,8位;HW表示半字,16位;W表示字,32位;

I2S0寄存器基地址为0xFF88 0000;I2S1寄存器基地址为0xFF89 0000;I2S2寄存器基地址为0xFF8A 0000;

2.5.1 I2S_TXCR

I2S_TXCR为发送操作控制寄存器,地址偏移0x0000;

| 位 | 属性 | 复位值 | 描述 |

| 31:23 | RO | 0x0 | reserved |

| 22:17 | RW | 0x00 |

RCNT |

| 16:15 | RW | 0x0 |

TCSR |

| 14 | RW | 0x0 |

HWT |

| 13 | RO | 0x0 | reserved |

| 12 | RW | 0x0 |

SJM |

| 11 | RW | 0x0 |

FBM |

| 10:9 | RW | 0x0 |

IBM |

| 8:7 | RW | 0x0 |

PBM |

| 6 | RO | 0x0 | reserved |

| 5 | RW | 0x0 |

TFS |

| 4:0 | RW | 0x0f |

VDW |

2.5.1 I2S_RXCR

I2S_RXCR为接收操作控制寄存器,地址偏移0x0004;

| 位 | 属性 | 复位值 | 描述 |

| 31:17 | RO | 0x0 | reserved |

| 16:15 | RW | 0x0 |

RCSR |

| 14 | RW | 0x0 |

HWT |

| 13 | RO | 0x0 | reserved |

| 12 | RW | 0x0 |

SJM |

| 11 | RW | 0x0 |

FBM |

| 10:9 | RW | 0x0 |

IBM |

| 8:7 | RW | 0x0 |

PBM |

| 6 | RO | 0x0 | reserved |

| 5 | RW | 0x0 |

TFS |

| 4:0 | RW | 0x0f |

VDW |

2.5.3 I2S_CKR

I2S_CKR为时钟发生寄存器,地址偏移0x0008;

| 位 | 属性 | 复位值 | 描述 |

| 31:30 | RO | 0x0 | reserved |

| 29:28 | RW | 0x0 |

TRCM |

| 27 | RW | 0x0 |

MSS |

| 26 | RW | 0x0 |

CKP |

| 25 | RW | 0x0 |

RLP |

| 24 | RW | 0x0 |

TLP |

| 23:16 | RW | 0x7 |

MDIV |

| 15:8 | RW | 0x1f |

RSD |

| 7:0 | RO | 0x1f |

TSD |

2.5.4 I2S_DMACR

I2S_DMACR为DMA控制寄存器,地址偏移0x0010;

| 位 | 属性 | 复位值 | 描述 |

| 31:25 | RO | 0x0 | reserved |

| 24 | RW | 0x0 |

RDE |

| 23:21 | RO | 0x0 | reserved |

| 20:16 | RW | 0x1f |

RDL |

| 15:9 | RO | 0x0 | reserved |

| 8 | RW | 0x0 |

TDE |

| 7:5 | RO | 0x0 | reserved |

| 4:0 | RW | 0x0 |

TDL |

2.5.5 I2S_INTCR

I2S_INTCR为中断控制寄存器,地址偏移0x0014;

| 位 | 属性 | 复位值 | 描述 |

| 31:25 | RO | 0x0 | reserved |

| 24:20 | RW | 0x0 |

RFT |

| 19 | RO | 0x0 | reserved |

| 18 | WO | 0x0 |

RXOIC |

| 17 | RW | 0x0 |

RXOIE |

| 16 | RW | 0x0 |

RXFIE |

| 15:9 | RO | 0x0 | reserved |

| 8:4 | RW | 0x0 |

TFT |

| 3 | RO | 0x0 | reserved |

| 2 | WO | 0x0 |

TXUIC |

| 1 | RW | 0x0 |

TXUIE |

| 0 | RW | 0x0 |

TXEIE |

2.5.6 I2S_INTSR

I2S_INTSR为中断状态寄存器,地址偏移0x0018;

| 位 | 属性 | 复位值 | 描述 |

| 31:18 | RO | 0x0 | reserved |

| 17 | RO | 0x0 |

RXOI |

| 16 | RO | 0x0 |

RXFI |

| 15:2 | RO | 0x0 | reserved |

| 1 | RO | 0x0 |

TXUI |

| 0 | RO | 0x0 |

TXEI |

2.5.7 I2S_XFER

I2S_XFER为数据传输开始寄存器,地址偏移0x001C;

| 位 | 属性 | 复位值 | 描述 |

| 31:2 | RO | 0x0 | 保留 |

| 1 | RW | 0x0 |

RXS RX(接收)传输开始; 0:停止RX传输; 1:开始RX传输; |

| 0 | RW | 0x0 |

TXS TX(发送)传输开始; 0:停止TX传输; 1:开始TX传输; |

2.5.8 I2S_CLR

I2S_CLR为SCLK域裸机清除寄存器,地址偏移0x0020;

| 位 | 属性 | 复位值 | 描述 |

| 31:2 | RO | 0x0 | 保留 |

| 1 | RW | 0x0 |

RXC RX逻辑清除; 这是一个自动清除位,写入1可以清除所有接收逻辑; |

| 0 | RW | 0x0 |

TXC TX逻辑清除; 这是一个自动清除位,写入1可以清除所有发送逻辑; |

2.5.9 I2S_TXDR

I2S_TXDR为传输FIFO数据寄存器,地址偏移0x0024;

| 位 | 属性 | 复位值 | 描述 |

| 31:0 | WO | 0x00000000 |

TXDR |

2.5.10 I2S_RXDR

I2S_RXDR为接收FIFO数据寄存器,地址偏移0x0028;

| 位 | 属性 | 复位值 | 描述 |

| 31:0 | RO | 0x00000000 |

RXDR |

2.6 引脚

2.6.1 I2S0

I2S0接口有1路SDI,4路SDO,可以支持2个输入通道和8路输出声道。

| 功能引脚 | 方向 | 功能复用设置 |

| I2S0_MCLK | I/O | GRF_GPIO4A_IOMUX[1:0]=2’b01 |

| I2S0_SCLK | I/O | GRF_GPIO3D_IOMUX[1:0]=2’b01 |

| I2S0_LRCK_RX | I/O | GRF_GPIO3D_IOMUX[3:2]=2’b01 |

| I2S0_LRCK_TX | I/O | GRF_GPIO3D_IOMUX[5:4]=2’b01 |

| I2S0_SDO0 | O | GRF_GPIO3D_IOMUX[15:14]=2’b01 |

| I2S0_SDO1 | O | GRF_GPIO3D_IOMUX[13:12]=2’b01 |

| I2S0_SDO2 | O | GRF_GPIO3D_IOMUX[11:10]=2’b01 |

| I2S0_SDO3 | O | GRF_GPIO3D_IOMUX[9:8]=2’b01 |

| I2S0_SDI0 | I | GRF_GPIO3D_IOMUX[7:6]=2’b01 |

由于一个引脚具有多个功能,因此我们需要将引脚功能复用为I2S,至于每个引脚还有其它什么功能,可以查阅datsheet。

2.6.2 I2S1

I2S1接口有1路SDI,1路SDO,可以支持2个输入通道和2路输出声道。

| 功能引脚 | 方向 | 功能复用设置 |

| I2S1_MCLK | I/O | GRF_GPIO4A_IOMUX[1:0]=2’b01 |

| I2S1_SCLK | I/O | GRF_GPIO4A_IOMUX[7:6]=2’b01 |

| I2S1_LRCK_RX | I/O | GRF_GPIO4A_IOMUX[9:8]=2’b01 |

| I2S1_LRCK_TX | I/O | GRF_GPIO4A_IOMUX[11:10]=2’b01 |

| I2S1_SDI | I | GRF_GPIO4A_IOMUX[13:12]=2’b01 |

| I2S1_SDO | O | GRF_GPIO4A_IOMUX[15:14]=2’b01 |

2.6.3 I2S2

I2S2模块连接到HDMI和DP的音频接口,支持8通道音频数据传输。

I2S2与HDMI连接(这些引脚没有对外暴露,所以是看不到的):

| 引脚引脚(I2S2) | 方向 | 功能引脚(HDMI) | 方向 |

| I2S2_SCLK_OUT | O | ii2sclk | I |

| I2S2_TX_LRCK_OUT | O | ii2slrclk | I |

| I2S2_8CH_SDO[3:0] | O | ii2sdata[3:0] | I |

I2S2与DP连接(这些引脚没有对外暴露,所以是看不到的):

| 引脚引脚(I2S2) | 方向 | 功能引脚(DP) | 方向 |

| I2S2_SCLK_OUT | O | source_i2s_clk | I |

| I2S2_TX_LRCK_OUT | O | source_i2s_ws | I |

| I2S2_8CH_SDO[3:0] | O | source_i2s_data[3:0] | I |

2.7 应用说明

官方给出了I2S/PCM控制传输操作的流程图;

具体流程如下:

(1) 通过向I2C_XFER寄存器第0位写入0x0,禁止I2S发送器;

(2) 通过向I2S_CLR寄存器第0位写入0x1来清除I2S控制逻辑;

(3) 读取I2S_CLR寄存器第0位,直至该位为0x0;

(4) 通过设置I2S_TXCR和I2S_CKR寄存器配置I2S的操作模式;

(5) 为I2S发送器配置DMA通道,并通过I2S_TXDR寄存器传输目标地址;

(6) 向I2S_DMACR寄存器写入,以确定何时发出DMA请求;

(7) 向I2S_XFER寄存器第0位写入0x01,使能I2S发送器;

(8) I2S_XFER寄存器第0位不能被禁止直至数据传输完成;

三、 ALC5651

声卡是负责录音、播音、调节音量和声音合成等的一种多媒体板卡。我所使用的Nanopc-T4开发板搭载的是一款型号为ALC5651的声卡芯片。

3.1 特征

ALC5651具有以下特点:

- 支持一个24位/8kHz ~ 192kHz的I2S/PCM/TDM接口,可用于连接立体声DAC和ADC;

- 支持一个24位/8kHz ~ 192kHz的I2S/PCM接口,可用于连接立体声DAC和ADC;

- 支持I2C控制接口;

- 支持1路数字麦克风接口(DMIC)以及3路麦克风接口;

- 每个接口都具有异步采样率转换器(ASRC);

- 支持7段可调的均衡器(EQ),可以用于DAC和ADC路径上;

- 对于DAC和ADC路径,它还具有增强型动态范围控制器(DRC)/自动增益控制器(AGC)功能以及防风噪降噪滤波器;

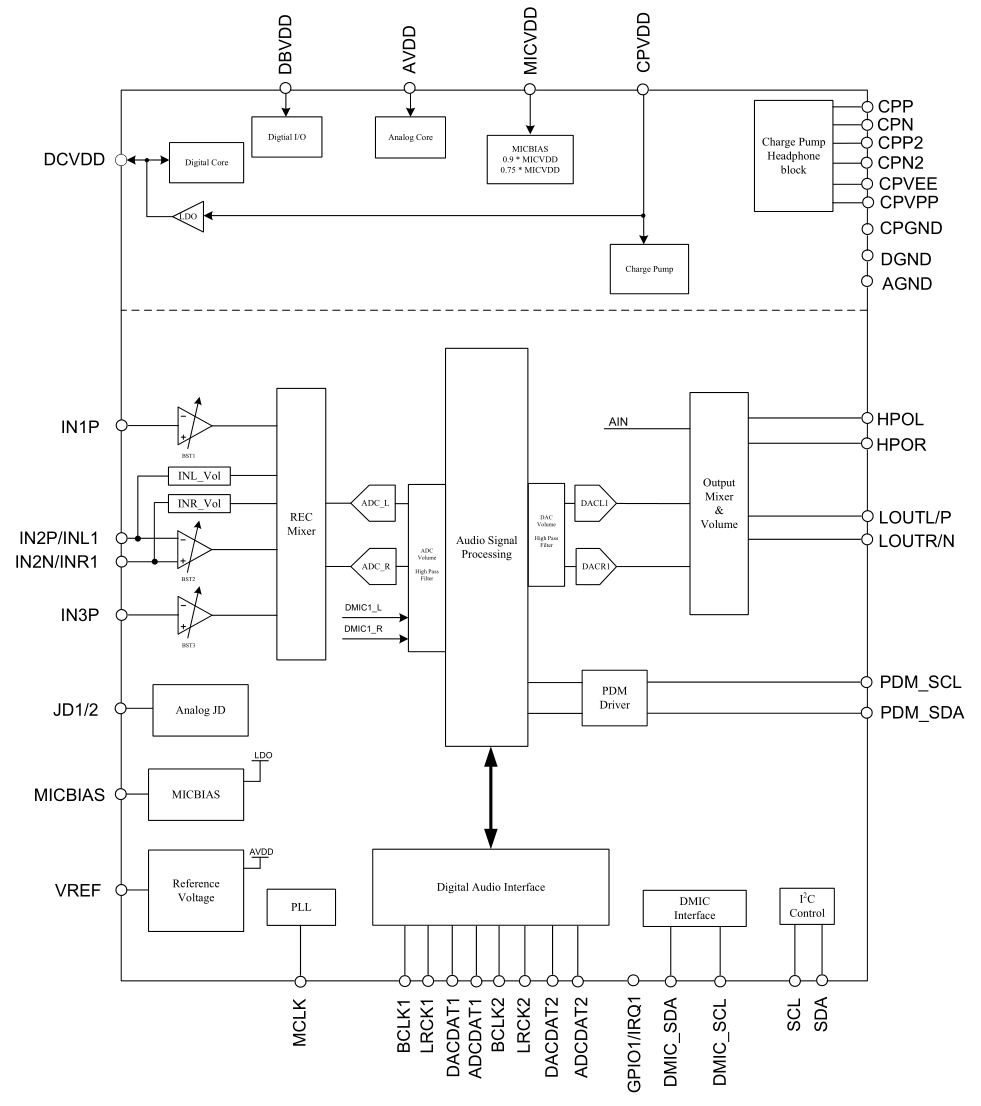

3.2 功能框图

ALC5651功能框图如下所示,该图来自ALC5651 datasheet:

ALC5651一共包含了40个引脚,其中包含了I2S1、I2S2、麦克风输入、耳机输出、Line output、Line input、电源、地等引脚。

3.2.1 数字引脚

其中数字I/O引脚主要是I2S接口、I2C接口等引脚,如下:

| 名称 | 类型 | 引脚 | 描述 |

| DACDAT1 | I | 31 | First I2S interface serial data input |

| ADCDAT1 | O | 30 | First I2S interface serial data output |

| BCLK1 | I/O | 33 | First I2S interface serial bit clock |

| LRCK1 | I/O | 32 | First I2S interface synchronous signal |

| DACDAT2 | I | 27 | Second I2S interface serial data input |

| ADCDAT2 | O | 26 | Second I2S interface serial data output |

| BCLK2 | I/O | 29 | Second I2S interface serial bit clock |

| LRCK2 | I/O | 28 | Second I2S interface synchronous signal |

| SDA | I/O | 36 | I2C interface serial data |

| SCL | I | 35 | I2C interface clock input |

| MCLK | I | 34 | I2S interface master clock input |

| GPIO1/IRQ | I/O | 37 |

General purpose input and output Interrupt output |

| GPIO2/DMIC_SCL | I/O | 38 |

General purpose input and output Digital microphone clock output |

| PDM_SCL | O | 25 | PDM clock output |

| PDM_SDA | O | 24 | PDM data output |

3.2.2 模拟引脚

其中模拟I/O引脚主要是麦克风、Line input、Line output、耳机输出等引脚,如下:

| 名称 | 类型 | 引脚 | 描述 |

| LOUTR/N | O | 13 |

Line output type Right channel single-end output Negative channel differential output |

| LOUTL/P | O | 12 |

Line output type Left channel single-end output Positive channel differential output |

| IN2P | I | 5 |

Positive differential input for microphone 2 Left channel line input |

| IN2N/JD2 | I | 6 |

Negative differential input for microphone 2 Right channel line input Second jack detection pin |

|

IN1P/DMIC_DAT |

I | 4 |

Single-end input for microphone 1 Digital microphone data input |

| JD1 | I | 3 | First jack detection pin |

| HPO_R | O | 21 |

Headphone amplifier output Right channel |

| HPO_L | O | 23 |

Headphone amplifier output Left channel |

| IN3P | I | 7 | Single-end input for microphone 3 |

3.2.3 Filter/Reference

| 名称 | 类型 | 引脚 | 描述 |

| MICBIAS1 | O | 2 | Bias voltage output for microphone |

| VREF | O | 11 | Internal reference voltage |

| CPVREF | - | 20 | Headphone reference ground |

| CPN1 | - | 16 | First charge pump bucket capacitor |

| CPP1 | - | 17 | First charge pump bucket capacity |

| CPN2 | - | 14 | Second charge pump bucket capacitor |

| CPP2 | - | 15 | Second charge pump bucket capacitor |

3.2.4 电源/地

| 名称 | 类型 | 引脚 | 描述 |

| MICVDD | P | 1 | Analog power for MICBIAS |

| AVDD | P | 9 | Analog power |

| DACREF | P | 8 | Analog power |

| AGND | P | 10 | Analog ground |

| CPVDD | P | 18 |

Analog power for headphone charge pump |

| CPVEE | P | 22 | Charge pump negative voltage output |

| CPVPP | P | 19 | Charge pump positive voltage output |

| DCVDD | P | 40 |

Digital power for digital core Kept open if LDO1_EN is pulled high, or connected to external 1.2V power. |

| DBVDD | P | 39 | Digital power for digital I/O buffer |

|

CPGND/DGND |

P | 41 |

Charge pump ground Digital ground |

3.3 电路原理图

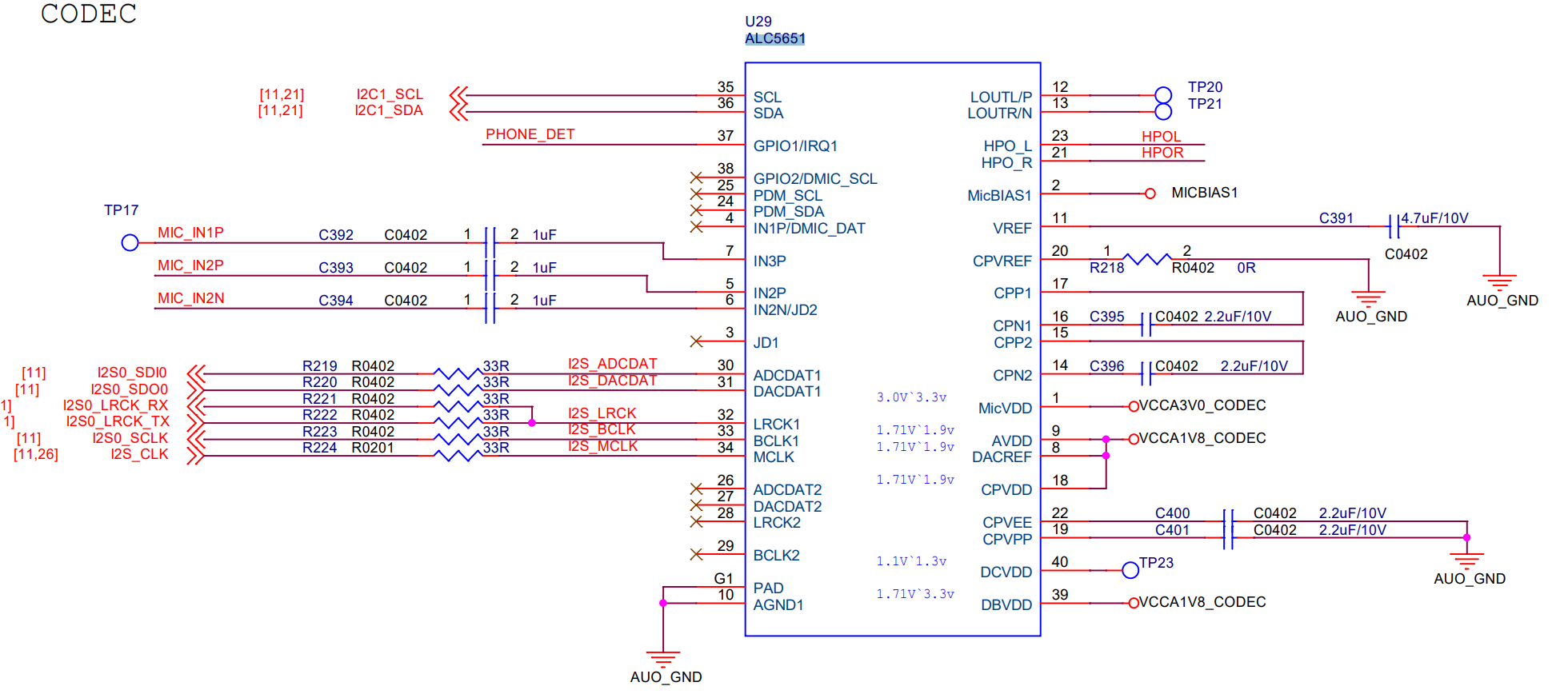

下图是ALC5651整体电路接线图:

下图是麦克风输入电路(连接的麦克风2,用于实现录音功能)、以及耳机输出电电路:

3.3.1 I2S接口引脚

ALC5651有两组I2S引脚,分别为I2S1、I2S2;

- I2S1:ADCDAT1、DACDAT1、LRCK1、BCLK1、MCLK;

- I2S2:ADCDAT2、DACDAT2、LRCK2、BCLK2、MCLK;

这里我们以I2S1为例进行介绍,当我们播放声音时,将数字信号传入DACDAT1引脚,ALC5651通过解码,产生模拟信号到喇叭/耳机;

录音时,ALC5651便获取麦克风的模拟信号,编码出数字信号到ADCDAT1引脚;

I2S接口相关的引脚如下:

- MCLK:SoC为编解码芯片提供的系统同步时钟(Master/System clock input),是采样频率的256倍;

- BCLK1:编解码芯片提供的串行时钟信号(Audio bit clock output),也就是量化位深,比如LRCKL1=44.1kHz,量化位深为32位,则BCLK=44.1kHz*32*2;

- LRCK1:采样频率信号,当为低电平时是采样的左声道信号,为高电平时采样的是右声道信号;

- ADCDAT1:ADC数据输入;

- DACDAT1:DAC数据输出;

由于I2S2引脚未被使用,我们只用看一下I2S1引脚与RK3399的接线关系:

| ALC5651 | RK3399 |

| MCLK | I2S_CLK(GPIO4_A0/I2S_CLK) |

| BCLK1 | I2S0_SCLK(GPIO3_D0/I2S0_SCLK) |

| LRCK1 |

I2S0_LRCK_TX(GPIO3_D2/I2S0_LRCK_TX) I2S0_LRCK_RX(GPIO3_D1/I2S0_LRCK_RX) |

| ADCDAT1 | I2S0_SDI0(GPIO3_D3/I2S0_SDI0) |

| DACDAT1 | I2S0_SDO0(GPIO3_D7/I2S0_SDO0) |

3.3.2 I2C接口引脚

ALC5651还有一组I2C控制引脚,与RK3399的接线关系如下:

| ALC5651 | RK3399 |

| SCL | I2C1_SCL(GPIO4_A2/I2C1_SCL) |

| SDA | I2C1_SDA(GPIO4_A1/I2C1_SDA) |

3.3.3 麦克风引脚

ALC5651支持1路数字麦克风、引脚如下,我们的开发板并没有使用数字麦克风;

- DMIC_DAT:数字麦克风数据输入;

- DMIC_SCL:数字麦克风时钟输出;

ALC5651支持3路麦克风,引脚如下:我们的开发板使用了麦克风2;

- IN1P:麦克风1的单端输入;

- IN2N:麦克风2的负向差分输入;

- IN2P:麦克风2的正向差分输入;

- IN3P:麦克风3的单端输入;

接线关系如下:

| ALC5651 | 其他 |

| IN3P | MIC_IN1P(麦克风0单端输入,未使用) |

| IN2P | MIC_IN2P(麦克风2输入正极) |

| IN2N | MIC_IN2N(麦克风2输入父极) |

3.3.4 PDM引脚

ALC5651支持PDM、引脚为如下,我们的开发板并没有使用PDM;

- PDM_SCL:PDM时钟输出;

- PDM_SDA:PDM数据输出;

3.3.5 电源引脚

电路接线图中使用到的电源引脚有VCCA3V0_CODEC、VCCA1V8_CODEC;

VCCA3V0_CODEC:rk808电源管理芯片14号输出引脚VLDO5,电压输出范围1.8~3.4V;

VCCA1V8_CODEC:rk808电源管理芯片5号输出引脚VLDO7,电压输出范围0.8~2.5V;

3.3.6 其他引脚

其它比较重要的引脚如下:

- GPIO2:基本输入输出引脚2;

- JD2:第二个耳机插入检测引脚,用于检测耳机插入状态的引脚;

- JD1:第一个耳机插入检测引脚,用于检测耳机插入状态的引脚;

- LOUTL/P:音频左输出通道1,线路输出类型,不可以直接驱动耳机,需要连接到功放或其他驱动器件才能使用;

- LOUTR/N:音频右输出通道1,线路输出类型,不可以直接驱动耳机,需要连接到功放或其他驱动器件才能使用;

- HPO_L:耳机放大器输出左声道,外接耳机插孔;

- HPO_R:耳机放大器输出右声道,外接耳机插孔;

- GPIO1/IRQ1:基本输入输出引脚1/中断输出;

这里我们只介绍使用的引脚:

| ALC5651 | RK3399 | 其他 |

| LOUTL | TP20(未使用) | |

| LOUTR | TP21(未使用) | |

| HPO_L | HPOL(左耳机输出) | |

| HPO_R | HPOR(右耳机输出) | |

| IRQ | HP_DET_H(GPIO4_D4) | PHONE_DET(检测耳机插入) |

参考文章

[1] 31.Linux-wm9876声卡驱动(移植+测试)

[2] Nanopc-T4原理图

[3] RK3399平台适配TI-tlv320aic3111音频芯片

[5] I2S音频协议详解

浙公网安备 33010602011771号

浙公网安备 33010602011771号