FPGA的uart串行通信(一)

UART串口是一种类似于USB、VGA的接口,有固定的引脚和通信协议。使用FPGA实现串口通信,可分为“计算机发送数据给FPGA”和“FPGA发送数据给计算机”两部分。

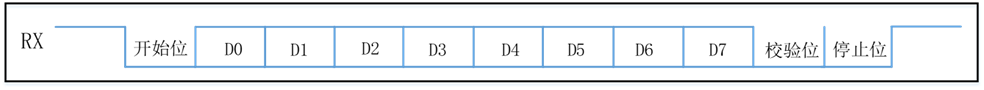

串口接收时序

上图为串口接收时序图(一帧),串口接收只需要一条数据线RX,具体流程如下:

- 起始位:当RX产生了一个下降沿后开始接收一帧数据,接收到的第一位为开始位,也就是发出一个“逻辑0”的信号,表示传输字符的开始

- 数据位:一帧周期内有11个时钟,第一个时钟是开始位,2-9个时钟是数据位,数据是从低位到高位接收的。

- 奇偶校验位:数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验),以此来校验数据传送的正确性。

- 停止位:通常为1位,1.5位,2位,停止位必须是“逻辑1”

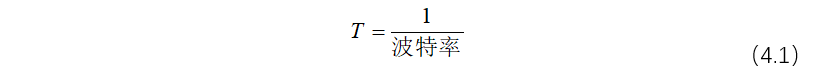

- 串口的接收时钟频率取决于它的波特率,常用的波特率为固定值。例如,9600bps,表示一秒内传送9600位数据,则一位数据的周期为

如何准确读取RX上的数据,需要以下两点:

- 判断RX什么时候开始接收一帧数据,即判断开始位

- 判断什么时候读取D0-D7上的数据,即判断数据位

接收数据过程

- 空闲状态,线路处于高电平

- 当检测到线路的下降沿,线路电位由高电平变为低电平,说明有数据传输,此时按照约定的波特率从低位到高位接收数据,数据接收完成后依次发送奇偶校验位和停止位,然后校验位判断数据传输是否正确,如果正确,则后续通知设备接收数据或存入缓存。

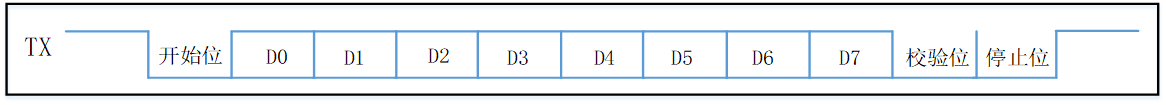

串口发送时序

上图为发送一帧数据的简单时序图,可以看出,串口的发送和接收时序是一样的,而接收和发送的不同点在于,接收是把数据从时序中提取出来,发送是把数据放入时序中去。

发送数据过程

- 空闲状态,线路处于高电位

- 当收到发送指令后,拉低线路的一个数据位,然后开始发送数据,按低位到高位依次发送,数据发送完成后,接着发送奇偶校验位和停止位(停止位为高电平),一帧数据发送完成。

浙公网安备 33010602011771号

浙公网安备 33010602011771号