时钟双边沿触发问题

问题

题目链接:Dualedge

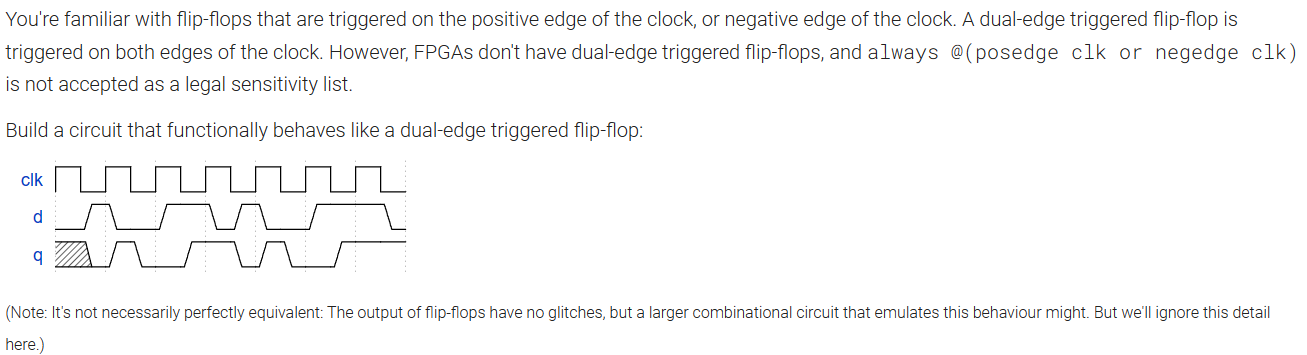

题目让实现同时在时钟clk上升沿和下降沿都进行触发(triggered),但是提示说:我们无法通过(posedge clk or negedge clk)这种方式来实现,在FPGA中实际上是不存在这种双边沿触发的触发器的。

FPGA(以及其他任何地方)上的触发器是一个具有一个时钟且仅对该时钟的一个边缘敏感的器件。没有真正的硬件设备能够实现@(posedge clk or negedge clk)

有一个例外:IDDR和ODDR,至于具体怎么实现不是很清楚。

解决方法

有一种做法看似能够实现,但是综合的时候是不能通过的

assign clk_gen = ~clk;

always@(posedge clk) begin

q <= d;

end

always@(posedge clk_gen) begin

q <= d;

end

两种能够通过的解法:

- 方法一:可能会产生毛刺

module top_module (

input clk,

input d,

output q

);

reg p,n;

always@(posedge clk)

p <= d;

always@(negedge clk)

n <= d;

assign q = clk ? p : n;

endmodule

为什么会有毛刺产生?可以看下面电路

由于触发器输出会产生一个延迟,因此q和p的输出相对clk会有一个延迟,如果采用这种方法,则图中部分会产生毛刺

- 方法二:官方给的解法

module top_module(

input clk,

input d,

output q);

reg p, n;

// A positive-edge triggered flip-flop

always @(posedge clk)

p <= d ^ n;

// A negative-edge triggered flip-flop

always @(negedge clk)

n <= d ^ p;

// Why does this work?

// After posedge clk, p changes to d^n. Thus q = (p^n) = (d^n^n) = d.

// After negedge clk, n changes to d^p. Thus q = (p^n) = (p^d^p) = d.

// At each (positive or negative) clock edge, p and n FFs alternately

// load a value that will cancel out the other and cause the new value of d to remain.

assign q = p ^ n;

// Can't synthesize this.

/*always @(posedge clk, negedge clk) begin

q <= d;

end*/

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号