《摄像头 —— MCLK、VSYNC、HSYNC、PCLK》

MCLK: MCLK是指芯片的主时钟,由BB提供,是CCM sensor的时钟源,MCLK由sensor处理后变成传输数据所需要的PCLK,PCLK指pixel采样的时钟。

PCLK:有些方案给他起名字叫:DotCLK。是像素点同步时钟信号。也就是每个PCLK对应一个像素点。

VSYNC(垂直同步信号):

- 用于标记一帧图像的开始或结束。

- 一个 VSYNC 脉冲表示一帧图像传输完成,下一帧即将开始。

- VSYNC 的频率决定了帧率(FPS)

HSYNC(水平同步信号):

- 用于标记一行图像的开始或结束。

- 一个 HSYNC 脉冲表示一行像素数据传输完成,下一行即将开始。

- HSYNC 的频率决定了行频(每秒传输的行数)。

VSYNC、HSYNC 与曝光的关系

VSYNC(垂直同步信号):

- VSYNC 用于标记一帧图像的开始或结束。在摄像头中,一帧图像的曝光时间通常是在 VSYNC 信号之间的时间段内确定的。

- 曝光时间是指摄像头传感器接收光线并转化为电信号的时间长度。VSYNC 信号的频率(即帧率)会影响每帧图像的曝光时间上限,因为一帧图像的采集必须在下一帧 VSYNC 信号到来之前完成。

- 如果 VSYNC 频率较高(帧率较高),则每帧图像的曝光时间可能较短,反之则较长。但曝光时间还受到其他因素(如光圈大小、传感器增益等)的影响。

HSYNC(水平同步信号):

- HSYNC 用于标记一行图像的开始或结束。在曝光过程中,HSYNC 信号确保每一行像素在正确的时间点开始和结束曝光。

- 虽然 HSYNC 本身不直接决定曝光时间,但它与 VSYNC 一起,通过定义帧和行的结构,间接影响了曝光时间的分配。例如,在一帧图像中,每一行的曝光时间可能受到 HSYNC 信号周期的限制。

VSYNC、HSYNC 与 PCLK 的关系

PCLK(像素时钟):

- PCLK 是像素点同步时钟信号,每个 PCLK 对应一个像素点的采集和传输。

- PCLK 的频率决定了像素数据的传输速率,也间接影响了曝光过程中像素数据的读取速度。

- 在摄像头中,PCLK 通常与 VSYNC 和 HSYNC 信号协同工作,以确保像素数据在正确的时间点被采集和传输。

VSYNC、HSYNC 与 PCLK 的协同作用:

- VSYNC 信号触发一帧图像的采集开始,HSYNC 信号则在一帧图像内触发每一行像素的采集开始。

- PCLK 信号在每一行像素采集过程中,按照固定的频率驱动像素数据的读取和传输。

- 这三个信号共同确保了摄像头能够按照预定的帧率、行率和像素率采集和传输图像数据。

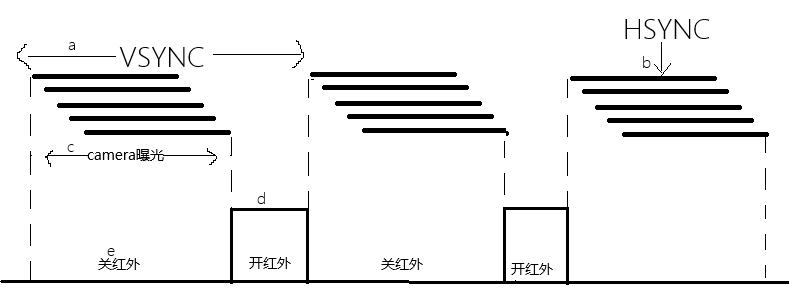

下图为摄像头行扫描成像:

其中为了解决在camera曝光周期外,打开红外灯。避免在camera夜视模式,红外灯影响camera成像。目标则是在保证夜视成像效果的前提下,尽可能拉长开红外的时常。

1.首先调整VSYNC,VSYNC(帧率)越小,曝光时间则长,会拉大a的长度。

2.行周期也就是b(HSYNC)缩小,hsync=每行像素数 / 像素时钟。行像素为camera固定,则在图像传输的前提下,尽可能提高像素时钟。

3.在c(camera一帧曝光时常)的时候,关闭红外e。然后在d的时长打开红外灯。

1.PCLK是由MCLK进行分频而来......

2.PCLK是个时钟,通过寄存器只能调节它的频率什么的,它是控制像素输出的一个时钟;

3.在曝光时间的算法中需要知道PCLK的值,是因为在sensor内没有时间观念,只有频率,所以在算曝光计算时需要将所要的曝光的秒数转换为曝光的clock数,同样的

Clock数,在不同的频率下代表的时间是不同的,例如同样的1000个clock在12HZ和24HZ下代表的时间就差了二倍。

而PClk的值一般是以提供给sensor的MCLK除以sensor内部除频后的值,而每个sensor的除频设计方式不太相同,所以需要对照datasheet才行。

4.我解释一下pll,PC-camera芯片晶振产生时钟,pll进行倍频输出MCLK给sensor,sensor再通过pll产生合适的PCLK,一般PC-camera芯片输出的MCLK是固定的几个值,

而sensor这边输出的PCLK根据调节相应的寄存器在可以输出的值在一定范围内可随意调,sensor输出PCLK和曝光是两个独立的过程,对于曝光可以设置target值进行亮度调整,

如果是非SOC sensor可以改变dummy line和dummy pixel来调节帧率,对于水波纹的消除可以根据PCLK可抑制消除,这样的PCLK有约束,如果真可输出频率范围内的频率输出则可以

调节dummy pixel来消除。

5.MCLK = 倍率系数*Pclk

个人理解:

1.主控提供mclk

2.sensor将mclk分频成pclk

3.sensor通过pclk做像素采样

4.sensor采集完像素,通过mipi接口传输图像数据给主控,其中VSYNC和HSYNC用来告诉主控哪些数据是同一帧,哪些数据是同一行

浙公网安备 33010602011771号

浙公网安备 33010602011771号