《计算机体系结构基础》杂记(4)

记录下读胡伟武的《计算机体系结构基础》的一些知识点和扩展,第五部分,并行处理结构。

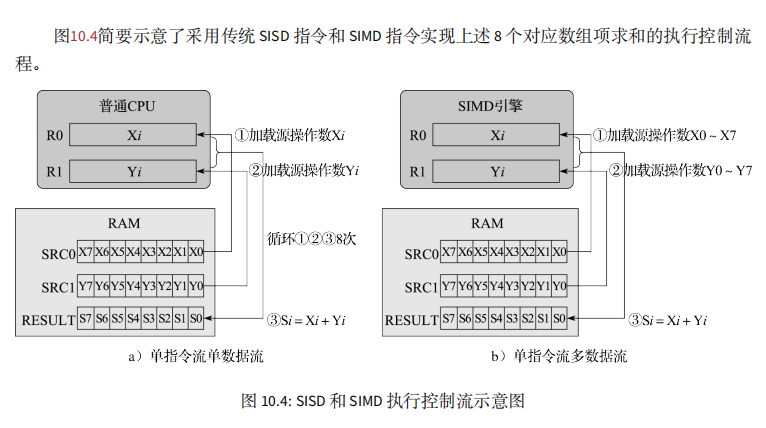

1、指令级并行性、数据级并行性、任务级并行性

2、数据相关包括写后读(Read After Write,简称 RAW)相关、读后写、(Write AfterRead,简称 WAR)相关和写后写(WriteAfter Write,简称 WAW)相关。

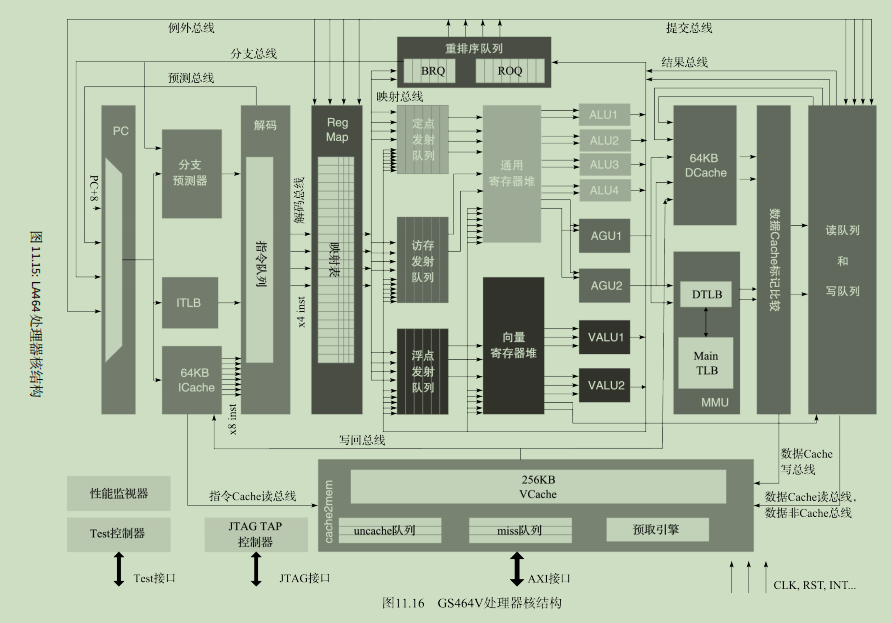

3、现代处理器采用多种微结构设计技术挖掘指令级并行性,包括指令流水线、多发射、动态调度、寄存器重命名、转移猜测等技术。指令流水线重叠执行多条不相关的指令;多发射技术允许一个时钟周期执行多条指令,类似于 “多车道”;动态调度允许后续指令越过前面被阻塞的指令继续被调度执行,相当于允许 “超车”;寄存器重命名主要解决 RAW 和 WAW 的假相关问题;转移猜测技术可以猜测分支指令的方向和目标,在分支指令还未执行完之前获取更多可执行指令,以减少控制相关造成的指令流水线阻塞。

4、并行编程模型(Parallel Programming Model)是一种程序抽象的集合,它给程序员提供了一幅计算机硬件/软件系统的抽象简图,程序员利用这些模型就可以为多核处理器、多处理器、机群等并行计算系统设计并行程序。

5、

6、POSIX 编程标准

7、OpenMP 标准

8、MPI(Message Passing Interface)定义了一组消息传递函数库的编程接口标准。

9、多核处理器

(1)半导体工艺发展

(2)功耗墙问题

(3)并行结构的发展

1)SIMD结构。2)对称多处理器(Symmetric MultiProcessor,简称SMP)结构。3)高速缓存一致非均匀存储器访问(Cache Coherent Non‑Uniform Memory Access,简称CC‑NUMA)结构。4)MPP(Massive Parallel Processing)系统。5)机群系统。

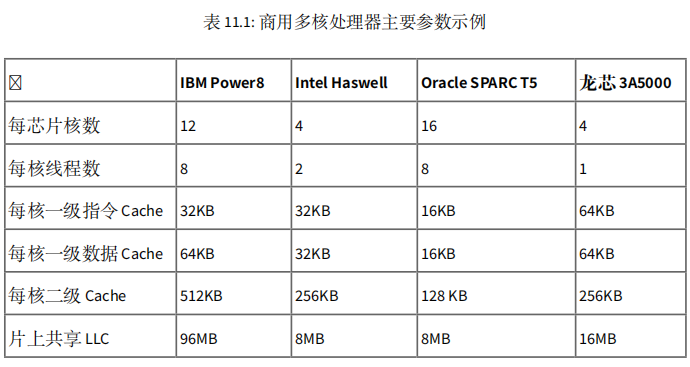

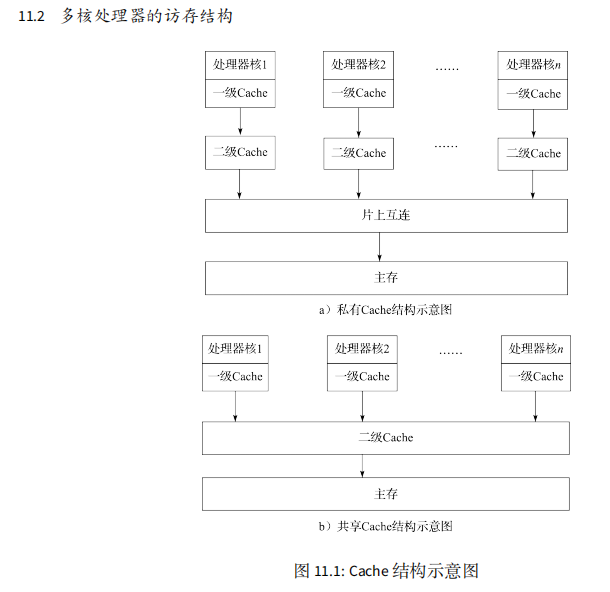

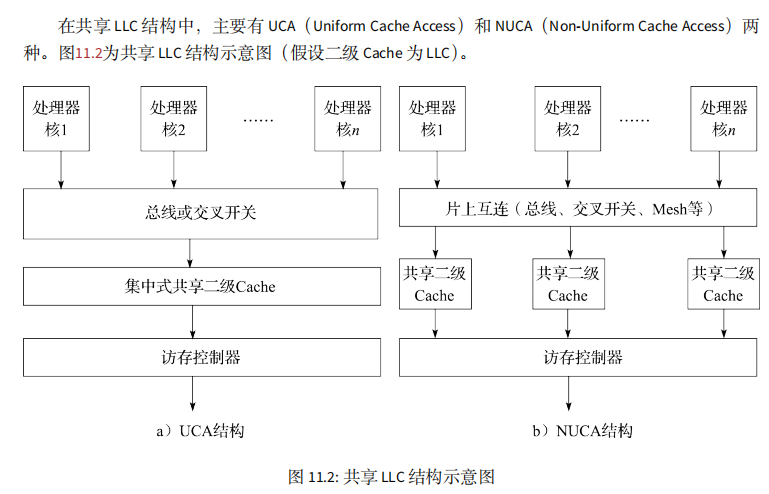

10、目前,主流多核处理器的典型 Cache 结构是:片内共享最后一级 Cache(Last Level Cache,简称LLC),片间共享内存。表11.1列出了典型商用多核处理器的Cache结构参数。处理器核的一级Cache和二级Cache私有,三级Cache(LLC)共享。有些处理器甚至有片外的四级Cache,例如Intel i7处理器。

11、存储一致性模型最初是针对共享存储的多处理器设计提出来的,同样也可以适用于多核处理器设计。

文献中常见的存储一致性模型包括:顺序一致性模型、处理器一致性模型、弱一致性模型、释放一致性模型等。

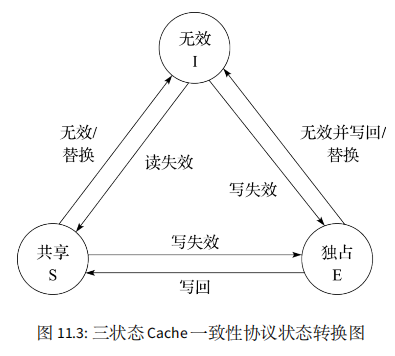

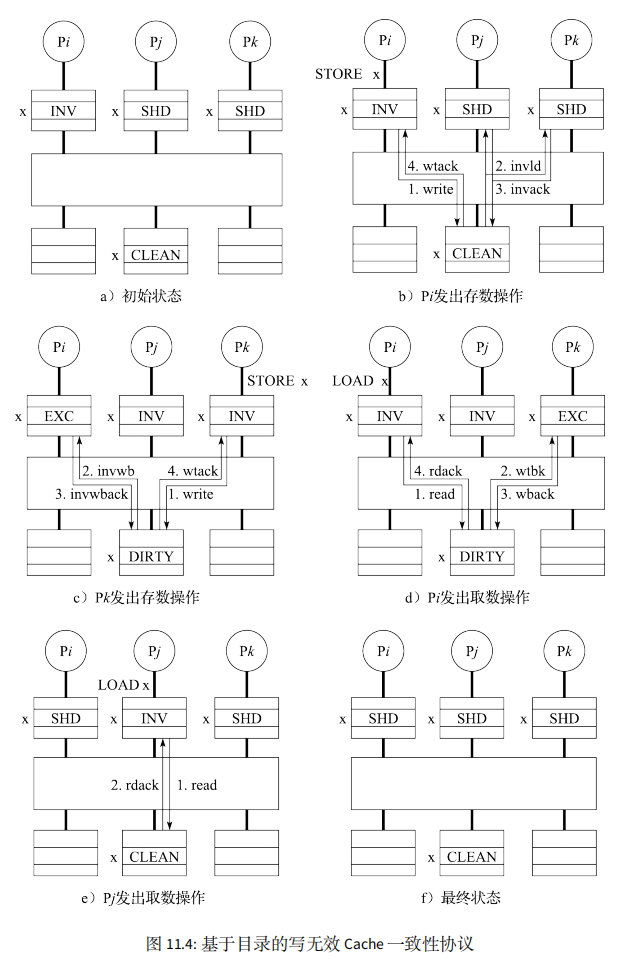

12.Cache 一致性协议

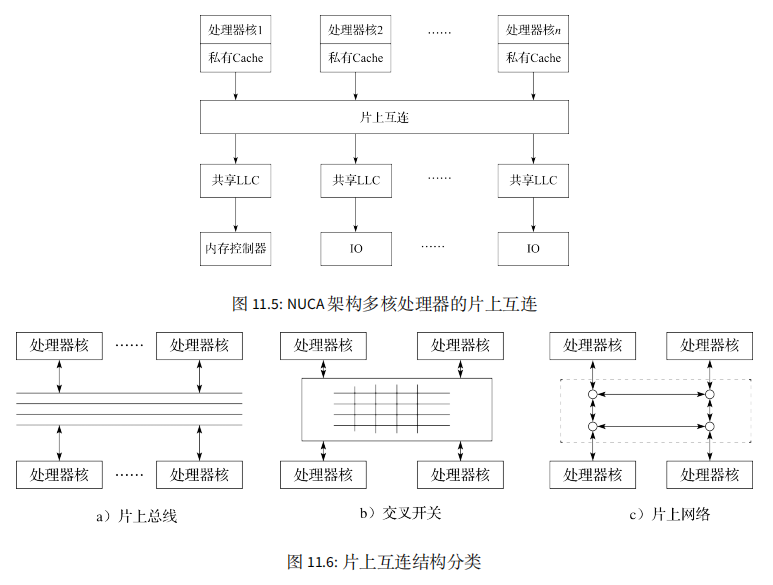

13、多核处理器的互连结构————片上总线,交叉开关,片上网络

14、多核处理器的同步机制

1) 原子操作 原子指令的实现方式可以分为两种,其中一种是直接使用一条“读‑改‑写”(Read‑Modify‑Write,

RMW)原子指令来完成,另一种是使用一组原子指令对LL/SC(Load‑Linked/Store‑Conditional)来完成

指定的原子操作。

2) 锁的软件实现方法

3)栅障软件实现方法

4)事务内存

15、可以从以下几个维度对多核处理器结构进行分析:一是从处理器核及访存带宽的维度,包括核的数量、大核还是小核、同构核还是异构核、通用核还是专用核等,访存带宽与峰值计算能力之间的比例决定该多核处理器的通用性。二是从存储一致性模型的维度,存储一致性模型对多个处理器核发出的访存指令次序进行约定,包括顺序一致性模型、处理器一致性模型、弱一致性模型等。三是从 Cache 组织及一致性协议的维度,包括有几级 Cache、Cache 容量、私有还是共享 Cache,Cache 一致性协议是把一个处理器核新写的值传播到其他处理器核的一种机制。四是从片上互连结构的维度,即多个核处理器核间如何实现通信。五是多核之间的同步机制的维度,如互斥锁操作(lock)、路障操作(barrier)等。

浙公网安备 33010602011771号

浙公网安备 33010602011771号