【转】建立时间和保持时间

如图所示,当时钟为高电平是,Q随D变化而变化;而当时钟为高电平时,Q值保持不变。

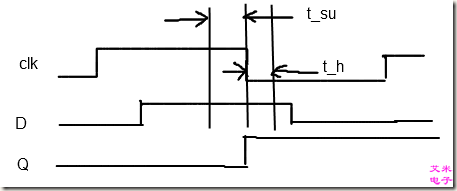

图3.4所示为门控D触发器基本时序参数模型。在clk下降沿到来之前,D必须保持稳定的最短时间叫做锁存器的建立时间t_su,在clk的下降沿之后,D必须保持稳定的最短时间叫做锁存器的保持时间t_h。

图3.4 门控D触发器基本时序参数

4 亚稳态

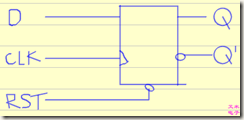

图4.1 异步复位的D-ff

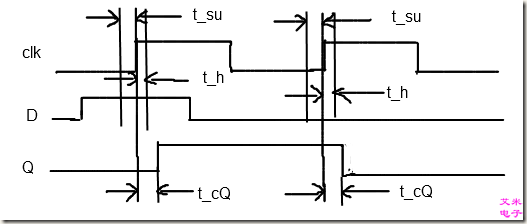

图4.2 触发器的时序参数

如图4.2所示,在clk的上升沿到来之前,D必须保持稳定的最短时间为触发器的建立时间t_su;在clk的上升沿到来之后,D必须保持稳定的最短时间为触发器的保持时间t_h。如果t_su或t_h不能严格达到电路的要求,那么触发器就会进入不稳定状态,即亚稳态。从clk的上升沿起,Q随D变化而变化所需要的时间为clk到Q的传播延迟t_cQ。

原文:http://www.cnblogs.com/yuphone/archive/2010/10/25/1860871.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号