微机原理

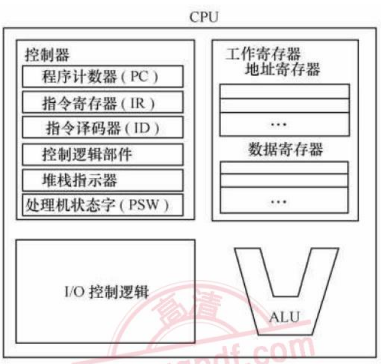

1 CPU组成

cpu由运算器和控制器和寄存器组成。

运算器用于完成数据的算术和逻辑运算。

控制器

寄存器用于暂存参加运算的操作数和运算结果。

80x86微处理器指的是一系列处理器型号。包括8086,80286,80386,Pentium系列。

1.1结构图

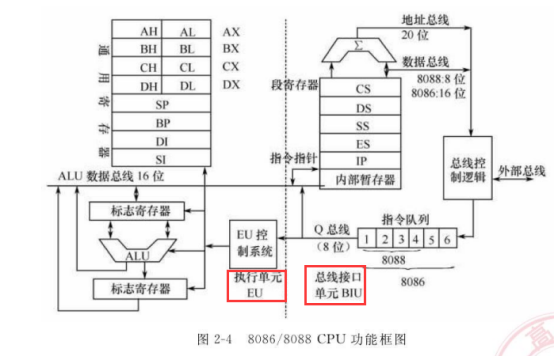

1.2 8086/8088功能结构

由两部分组成,总线接口单元(BIU),执行单元(EU)

1.2.1 BIU总线接口单元

组成:

段寄存器CS,DS,SS,ES

指令指针IP

指令队列寄存器

加法器:作用是累加段寄存器和IP或者EU部件提供的偏移地址形成20位物理地址

总线控制逻辑

问题:段寄存器16位,而地址总线20位,如何做到16位地址能够访问20位地址空间?从8086开始采用地址分段机制,也就是说比如说数据段寄存器DS中存储的数据段地址为10110001 00111100,以这个作为段基址,再用另一个寄存器存储偏移地址00000000 00001001

然后段基址左移4位+偏移地址就得到20位物理地址。

1.2.2 EU执行单元

组成:

ALU算术逻辑运算单元

通用寄存器:AX,BX,CX,DX,SP,BP,DI,SI

PSW程序状态字

EU控制器

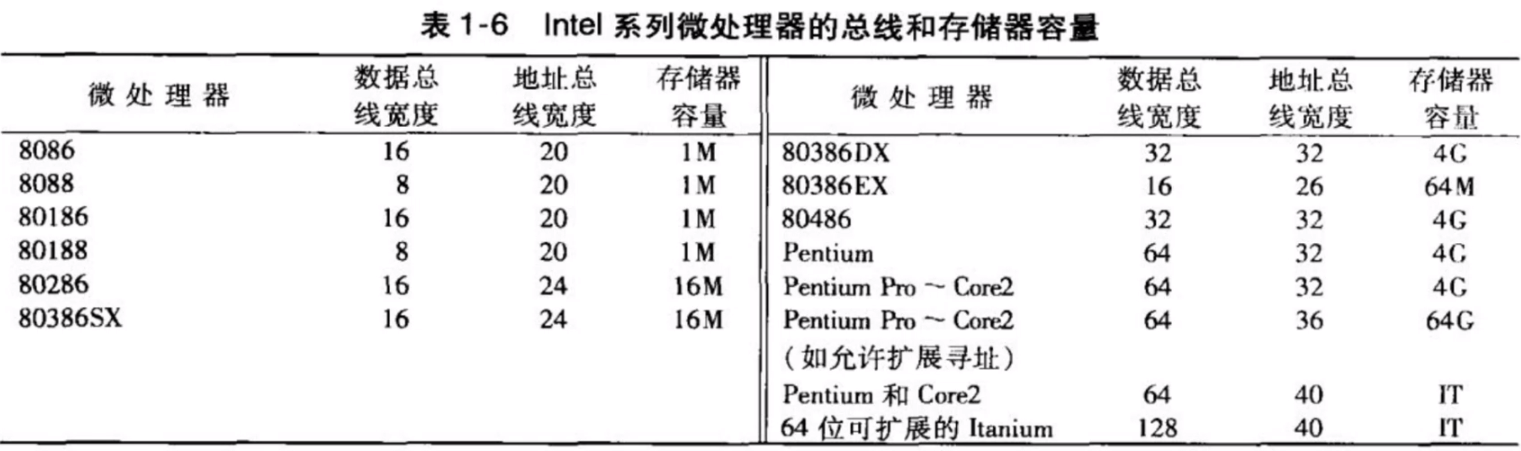

1.3 CPU容量发展

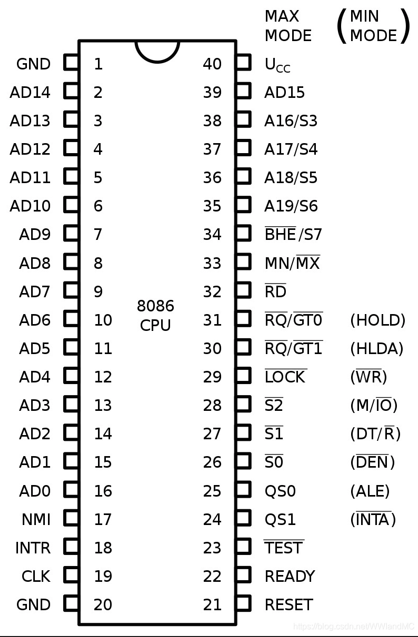

以8086为例,说明一下cpu位数和地址总线和数据总线的关系

下图有20个地址线(AD0~AD15,A16~A19),16个数据线(AD0~AD15),它有16条数据线,一次能够传输16位2进制数据,因此该CPU是16位处理器

它有20个地址线,在其寻址范围为2^20=1M寻址空间,也就是说它的寻址能力是1M。

上述说的是该CPU的寻址能力,需要和实模式下和保护模式下的分段机制区分开,他们是两个不同的概念。寻址能力指的是其最大和寻址的范围。分段机制是内存的表示方法(即虚拟地址和真实物理地址)

而且实模式下和保护模式下的分段机制不一样,实模式下一个段大小是16kb,因此虚拟地址到物理地址的转换:段基址*16+偏移地址,也就是段基址左移4位+偏移地址;而保护模式下地址仍然采用“段地址:偏移地址”的方式来表示,但段的概念发生了根本性的变化。段不再仅仅是内存的一个连续区域,而是由描述符表(如全局描述符表GDT或局部描述符表LDT)中的描述符定义的

1.4 寄存器

1.4 存储器地址空间分类

8086/8088有20条地址总线,寻址范围为2^20次方。

存储器中每个字节对应一个地址,地址范围:000000H-FFFFFFH

存储器是分段对数据进行存储的。每个段的地址存储在段寄存器中,由于段寄存器是16位的,所以每个段的最大容量是2^16=64kb的存储单元。

一个段的起始地址的高16位称为该段的段地址。所以可以有2^16个段地址。任意相邻的两个段地址相距16个存储单元。段内存储单元的偏移量称为段内偏移地址。偏移地址也是16位的,所以一个段最大可以包含2^16=64kb的存储空间。

用户编写的程序,加载到内存后,存储在代码段、数据段、堆栈段、附加段中。

1.5 I/O端口

一个I/O端口就是I/O接口电路内部的一个寄存器或一组寄存器。一个I/O端口有唯一的I/O地址与之对应。

1.6 一些CPU芯片介绍-80386

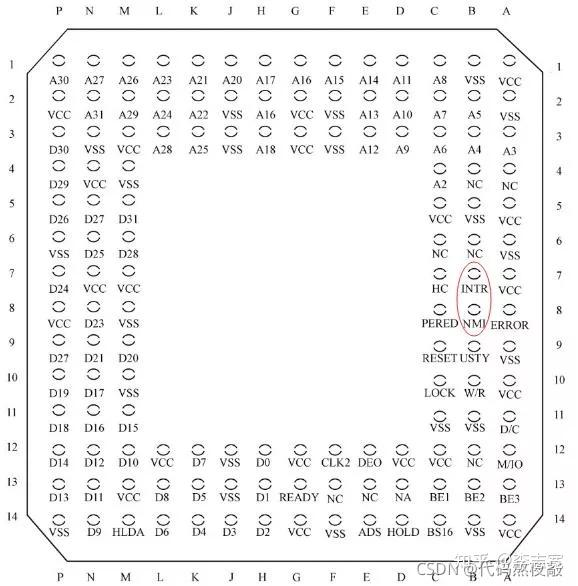

引脚图

2 总线

总线其实就是连接CPU各个部分的公共线路。在这方面讲,连接多个电脑的网络通信线路页可称之为总线。

按功能分,CPU内部总线可分为:地址总线,数据总线,控制总线。

浙公网安备 33010602011771号

浙公网安备 33010602011771号