常用的组合逻辑电路

1 编码器

1.1 编码

编码我们可以理解为,根据一定的规则,我们把一个输入A,编码成输出B。比如说ASCII码就是一种编码方式,输入是英文字符,输出是二进制数字。比如字母A的ASCII码为01000001.

1.2 集成电路中的编码器

编码器的特点:

1 输入2^n个,输出n个

1.3 普通编码器

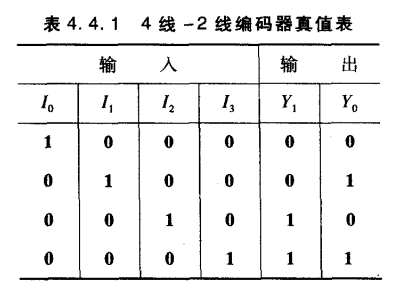

以4线-2线编码器为例

特点:

1 四个输入I3、I2、I1、I0

2 两个输出Y1、Y0

3 任何时刻I3-I0只能有一个为1

其真值表

1.4 优先编码器

特点:

1 四个输入I3、I2、I1、I0

2 两个输出Y1、Y0

3 任何时刻I3-I0并不是只能有一个为1

其真值表

从真值表我们可以看出,I3优先级最高,当I3为1时,不论其他输入端为何值,都输出11;I0优先级最低。

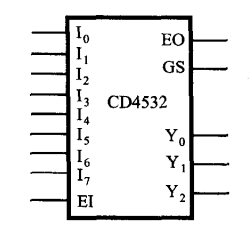

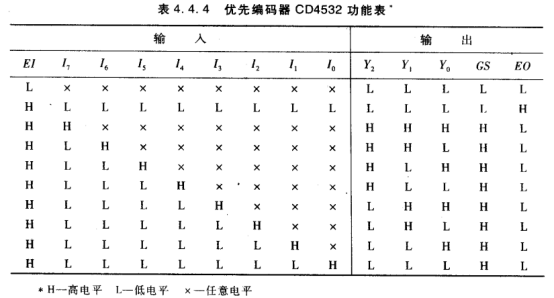

1.5 CD4532优先编码器介绍

CD4532是一个比较成熟的编码器。其封装成芯片供其他电路使用。

其是一个8线-3线编码器。输入有8路,输出有3路。另外EI为输入使能端,EO为输出使能端,GS为工作状态标志。

EI作用:当EI为高电平时,代表输入使能,编码器能够正常工作,否则输出都是低电平。

EO作用:当EI为高电平且I7-I0都为低电平时,EO输出高电平

GS作用:当EI为高电平且I7-I0任意一个为高电平,GS输出高电平

其真值表如下所示。

2 译码器

译码是编码的逆过程。它的功能是将具有特定含义的二进制码转换为对应的输出信号。比如CPU寻址的时候,将内存地址转化为2^n路高低电平,从而对应存储阵列中的2^n路线路,从而选中对应的存储单元。

2.1 74x139译码器介绍

74x139译码器是一种2线-4线译码器。

3 算术运算电路

3.1 半加器

半加器是指不考虑低位进位的加法器。其真值表如下所示。

3.2 全加器

全加器是考虑了低位进位的加法器,其真值表如下所示。

3.3 多位加法器

我们把全加器串联起来,就组成了多位加法器,如下图所示。

4 锁存器

大多数数字系统中,除了需要具有逻辑运算和算术运算功能的组合逻辑电路外,还需要具有存储功能的电路,组合电路和存储电路相结合可构成时序逻辑电路。

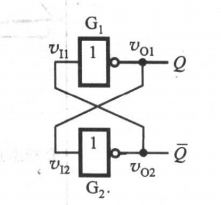

4.1 双稳态存储电路

当Q为1时,经过反相器使得Q为0,经过反相器使得Q为1.这样经过正反馈,使得该状态能够长期保持不变。

当我们在Vi2施加一个低电平,导致Q为1,从而导致Q为0,此时锁存器状态发生了改变。

这样,这种电路就能够保存一位高低电平信号。

4.2 锁存器

锁存器是一种能够长期保存一种电平状态的电路。它对脉冲电平敏感。

4.2.1 SR锁存器

它有两个输入端,S为置位端,R为复位端。

当S=0,R=0时,输出保持不变

当S=1,R=0时,Q置位

当S=0,R=1时,Q复位

基本的SR锁存器的保持和置1和置0功能是一个存储单元应具备的最基本功能。

4.2.2 D锁存器

D锁存器解决了SR锁存器S=1,R=1的不确定性。

E=0,D=X 保持

E=1,D=1 置1

E=1,D=0 置0

4.2.3 典型集成电路74HC/HCT373

该芯片是中规模集成的8D锁存器。该电路可以方便的应用于微机的总线传输电路。

其核心是8个传输门控D锁存器。

当锁存使能信号LE=1时,允许所有D锁存器动作,由D0-D7更新他们的状态。

当锁存使能信号LE=0时,则保持8位数据不变。

当输出三态使能信号OE=0时,三态门有效,输出锁存的信号到Q0-Q7.

当OE=1时,输出高阻态,起到隔离电路作用。

5 触发器

触发器是很重要的一个电路。基本上很多的存储电路都是由触发器组成的,同步时序电路中的存储电路一般都是由触发器组成的。

锁存器是对电平敏感的器件,触发器是时钟对脉冲边沿敏感的器件,分为上升沿触发和下降沿触发。

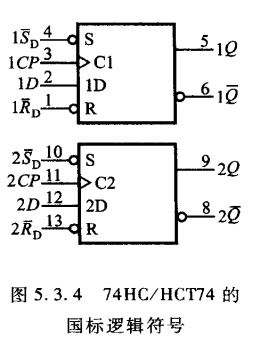

5.1 D触发器74HC/HCT74

这个芯片封装了2个D触发器。

CP为时钟信号,上升沿触发

SD为置位端,低电平置位,输出Q=1

RD为复位端,低电平复位,输出Q=0

当SD和RD都无效时,触发器工作。当上升沿之前Q是0,则上升沿之后Q=0;当上升沿之前Q是1,则上升沿之后Q=1。

特性方程:Qn+1=D

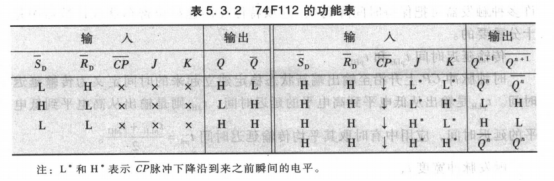

5.2 JK触发器74F112

该芯片含有两个JK触发器。

CP为时钟信号,下降沿触发

SD为置位端,低电平置位,输出Q=1

RD为复位端,低电平复位,输出Q=0

当SD和RD都无效时,触发器工作。

特性方程:Qn+1=JQn+KQn

5.3 其他触发器芯片及其特性方程

5.3.1 D触发器

特性表

特性方程

Qn+1=D

5.3.2 JK触发器

特性表

特性方程

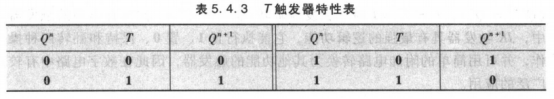

5.3.3 T触发器

特性表

特性方程

5.3.4 SR触发器

特性表

特性方程

6 时序电路

时序电路的特点:

1 由组合电路和存储电路组成,存储电路一般是锁存器或者触发器。

2 时序电路的状态由输入信号和当前电路的状态共同决定。

3 时序电路分为同步时序电路和异步时序电路。其中同步时序电路在外接时钟的控制下状态步进的进行改变,是设计超大型集成电路的基础。

6.1 若干典型的时序电路

6.1.1 寄存器

寄存器是数字系统中用来存储二进制数据的逻辑部件。cpu中就用到很多寄存器,比如ax、bx、cx、dx这些通用寄存器,那其是如何工作的呢?

1个触发器可以存储1位二进制数据,存储n位二进制数据的寄存器需要由n个触发器组成。

例如,下面是由8个触发器组成的8位寄存器的电路图,D0-D7是8位数据输入端,在CP脉冲上升沿作用下,D0-D7端的数据同时存入相应的触发器。输出是Q0-Q7。

写数据:当我们想寄存一个字节数据时,这个字节从D0-D7端传入,然后给个时钟脉冲,字节数据将会存储到这8个触发器中。此后时钟脉冲信号消失,触发器保持锁存状态。

读数据:我们可以在Q0-Q7读取这1字节数据。

改数据:当我们想修改寄存器的数据时,重复上面过程

这里面需要注意的一点是:时钟脉冲不能随便给,只有需要存储数据的时候,才给一个时钟脉冲。

7 存储器

7.1 ROM结构图

ROM是只读存储器,也就是说只需要读,不需要写。

下图所示为一个ROM芯片的内部结构示意图,有一个2-4译码器、存储阵列和输出控制电路组成。

每个位置如果有一个二极管,说明该处有值1,否则说明该处存储的值是0.由此可见ROM电路是组合电路,并不是时序电路。

现在对其进行分析。当A1A0=01时,经过译码器,Y3Y2Y1Y0=0010,只有Y1为高电平,对应的这一排的所有二极管导通(图上画的二极管可能不大规范,我们可以理解为只要Y1输出高电平,二极管处的十字交叉处相当于导通就可以了)输出端经过反相器,输出高电平,所有D3D2D1D0=1101.

在CPU中,当我们想读取ROM中某个地址(比如A1A0=01)处的值时,我们通过地址总线传输地址信号01,然后经过地址总线到达ROM存储器,ROM存储器中有一译码器,将地址信号译码为0010,也就是读取存储阵列中第2排存储的值(存1的地方有二极管,因此此处存储的值就是1101),然后输出引脚连接着数据总线,供cpu使用

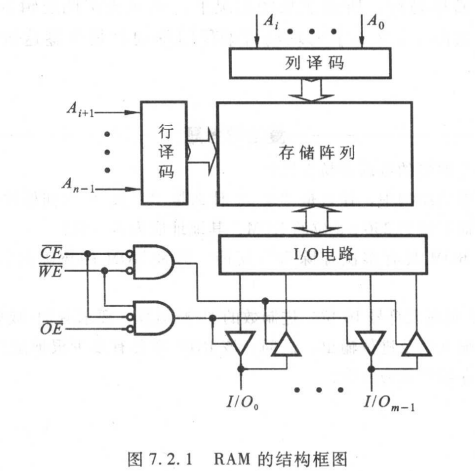

7.2 RAM

7.2.1 SRAM

静态随机存储器,基本结构分为如下几个部分:地址译码器、存储阵列、I/O控制电路。

其基本的存储单元为触发器。

A为n根地址线,I/O为m根数据线。其容量为2n * m

CE为片选信号,为0时RAM才能进行读写操作。

OE为输出使能信号

WE为写使能信号

由于触发器至少由6个MOS组成,因此存储密度较低。高速缓存一般使用SRAM。

7.2.2 DRAM

动态随机存储器,其基本存储单元为MOS管+小电容,由于结构简单,所有可以做成超大规模集成电路。我们平常说的内存一般是由DRAM组成的

其工作原理是,电容的电荷存储效应,当电容C充有电荷时,呈现高电压,存储1,反之存储0.MOS管相当于一个开关,当行选择线高电平时,T导通,C与位线连通,反之则断开。由于电容电荷会消散,所以要有定时刷新电路来补充电荷。

浙公网安备 33010602011771号

浙公网安备 33010602011771号