基于Verilog的格雷码编码器的设计

格雷码(Gray Code)是一种二进制编码方式,其特点是相邻的两个代码只有一位二进制数不同。格雷码常用于减少数字信号传输中的错误。

采用Verilog语言实现格雷码编码设计,按键输入4位二进制,编码器将二进制转换为格雷码,再将格雷码显示在四个LED等上。

采用Verilog语言实现格雷码编码设计,按键输入4位二进制,编码器将二进制转换为格雷码,再将格雷码显示在四个LED等上。

下面是一个基于Verilog的格雷码编码器的设计及其仿真测试程序。

1、一个4位二进制数到4位格雷码的编码器的Verilog描述

1 module gray_encoder( 2 input [3:0] binary, // 4位二进制输入 3 output [3:0] gray // 4位格雷码输出 4 ); 5 6 assign gray[3] = binary[3]; // 最高位保持不变 7 assign gray[2] = binary[3] ^ binary[2]; 8 assign gray[1] = binary[2] ^ binary[1]; 9 assign gray[0] = binary[1] ^ binary[0]; 10 11 endmodule

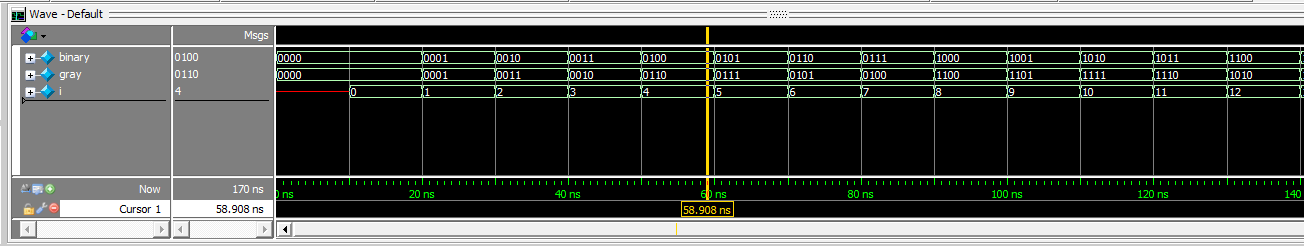

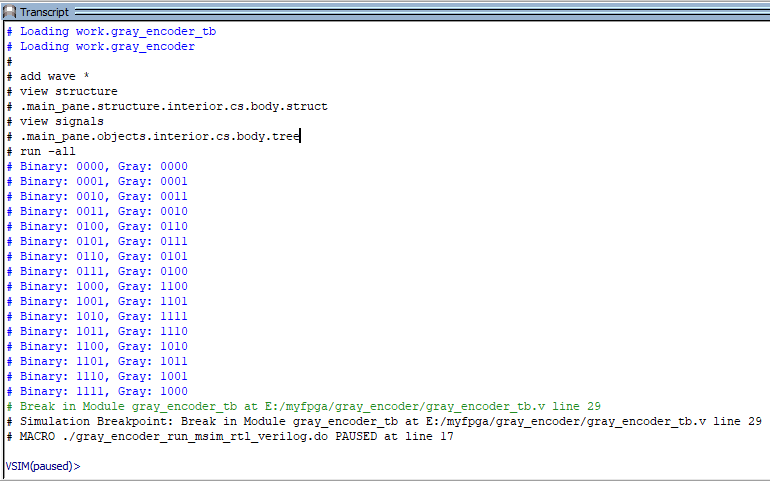

2、二进制转格雷码的仿真测试程序

1 `timescale 1ns/1ns 2 3 module gray_encoder_tb(); 4 5 reg [3:0] binary; // 4位二进制输入 6 wire [3:0] gray; // 4位格雷码输出 7 8 integer i; 9 10 // 实例化格雷码编码器 11 gray_encoder uut ( 12 .binary(binary), 13 .gray(gray) 14 ); 15 16 initial begin 17 // 初始化输入 18 binary = 4'b0000; 19 #10; 20 21 // 遍历所有可能的4位二进制数 22 for ( i = 0; i < 16; i = i + 1) begin 23 binary = i; 24 #10; 25 $display("Binary: %b, Gray: %b", binary, gray); 26 end 27 28 // 结束仿真 29 $stop; 30 end 31 32 endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号