普通8线-3线编码器的Verilog描述及仿真

一个8线-3线编码器将8个输入线编码为3位二进制输出。当输入中的某一位为1时,输出对应的二进制编码。通常,输入中只有一个位为1,其余为0。

1、普通编码器的Verilog描述(8线-3线编码器)

1 module encode83(

2 input [7:0] in, // 8位输入

3 output reg [2:0] out // 3位输出

4 );

5

6 always @(*) begin

7 case (in)

8 8'b00000001: out = 3'b000; // 输入第0位为1

9 8'b00000010: out = 3'b001; // 输入第1位为1

10 8'b00000100: out = 3'b010; // 输入第2位为1

11 8'b00001000: out = 3'b011; // 输入第3位为1

12 8'b00010000: out = 3'b100; // 输入第4位为1

13 8'b00100000: out = 3'b101; // 输入第5位为1

14 8'b01000000: out = 3'b110; // 输入第6位为1

15 8'b10000000: out = 3'b111; // 输入第7位为1

16 default: out = 3'bxxx; // 默认情况,输出未定义

17 endcase

18 end

19

20 endmodule

2、普通8线-3线编码器的Testbench仿真测试

1 `timescale 1ns/1ns

2

3 module encode83_tb();

4

5 reg [7:0] in; // 8位输入

6 wire [2:0] out; // 3位输出

7

8 // 实例化编码器模块

9 encode83 uut (

10 .in(in),

11 .out(out)

12 );

13

14 initial begin

15 // 测试所有可能的输入

16 in = 8'b00000001; #10; // 输出应为 3'b000

17 in = 8'b00000010; #10; // 输出应为 3'b001

18 in = 8'b00000100; #10; // 输出应为 3'b010

19 in = 8'b00001000; #10; // 输出应为 3'b011

20 in = 8'b00010000; #10; // 输出应为 3'b100

21 in = 8'b00100000; #10; // 输出应为 3'b101

22 in = 8'b01000000; #10; // 输出应为 3'b110

23 in = 8'b10000000; #10; // 输出应为 3'b111

24

25 // 测试无效输入(多个位为1)

26 in = 8'b00000011; #10; // 输出应为 3'bxxx

27 in = 8'b00001100; #10; // 输出应为 3'bxxx

28 in = 8'b00011000; #10; // 输出应为 3'bxxx

29

30 $stop; // 停止仿真

31 end

32

33 endmodule

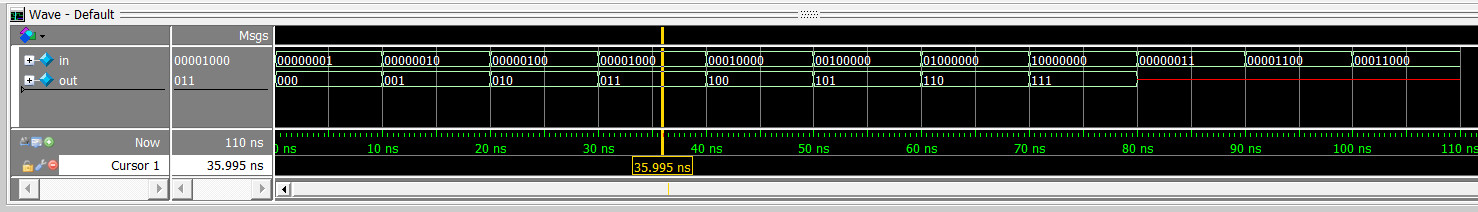

仿真结果如上图所示,初始化激励信号x为0000_0001,每延迟10ns,激励信号左移一位,重复7次,每次输入仅有1位有效输入,输出有效编码依次是000,001,010,011,100,101,110,111。第80ns时,x 输入中有多个位为1,输出将是未定义的状态。

浙公网安备 33010602011771号

浙公网安备 33010602011771号