命题运算符

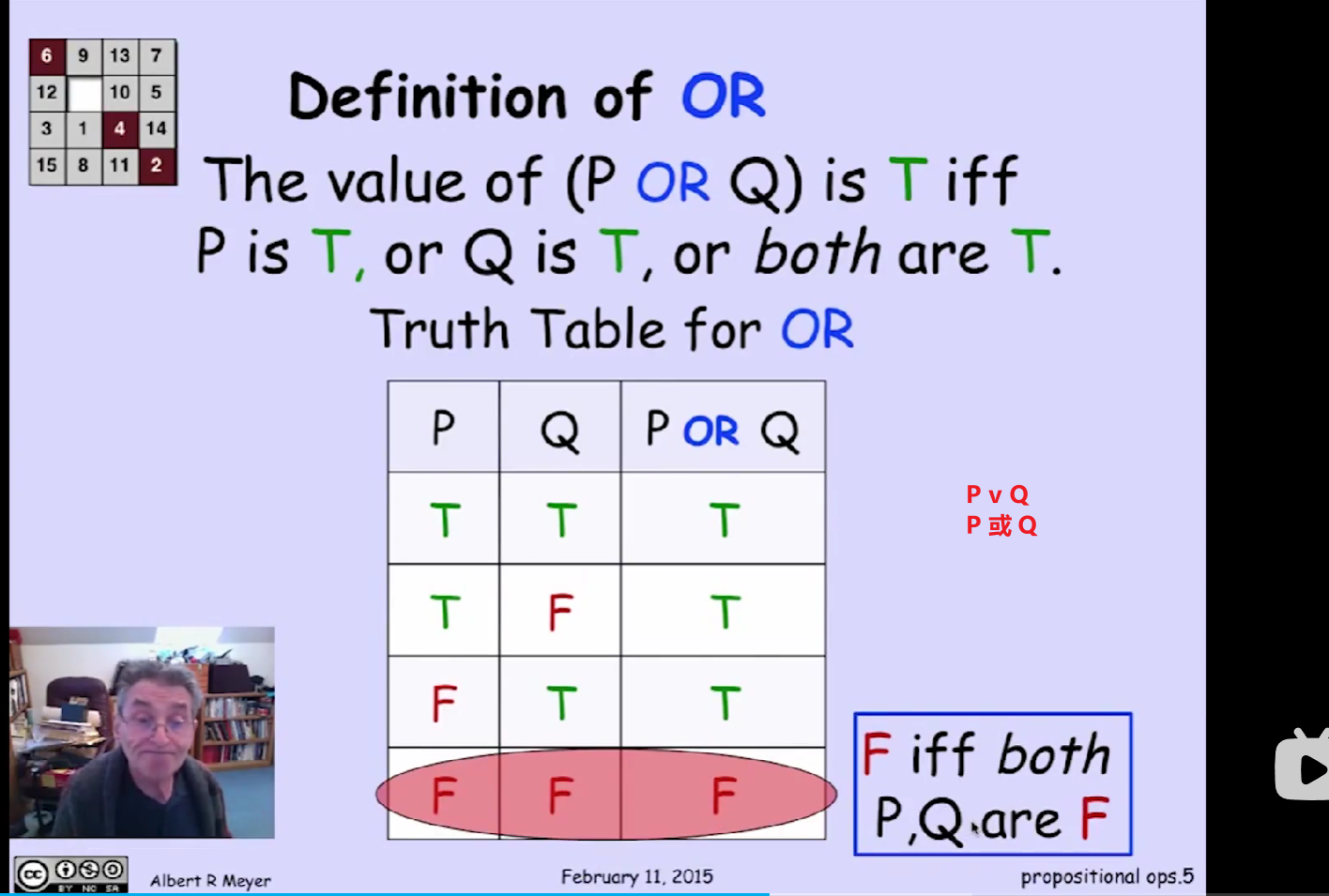

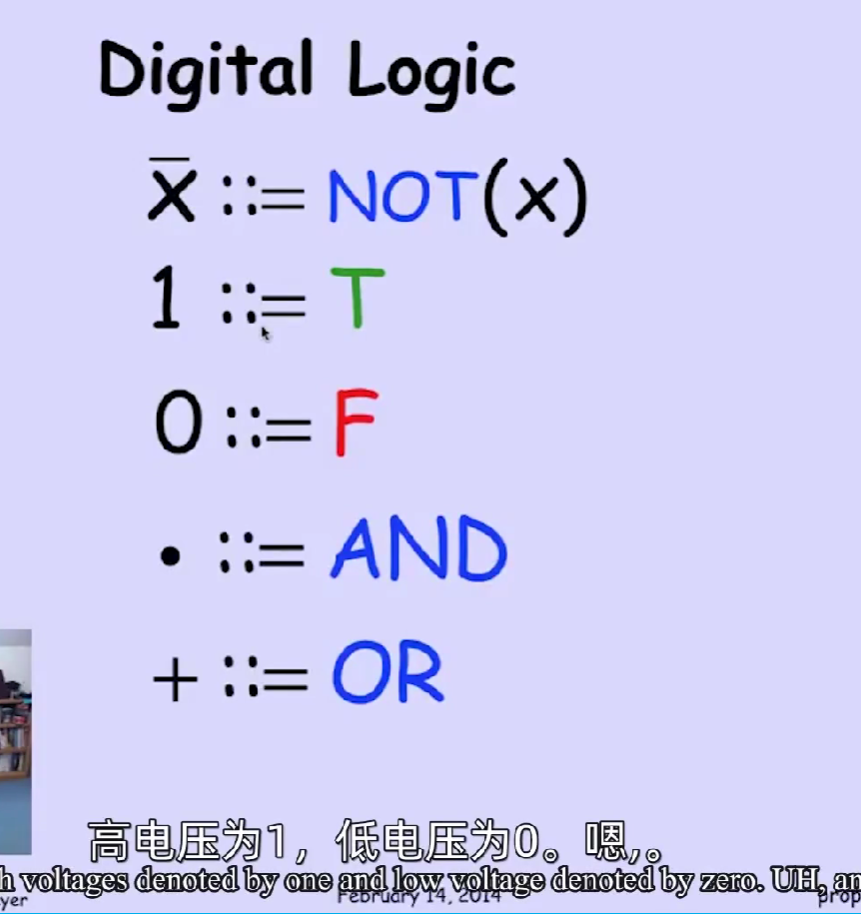

"v"运算符读作或,英文是“or",只有当其连接命题(其一定连接着2个及以上的命题)中的每一个命题均为假时,才能说或链接的这个大命题为假(全假为假)

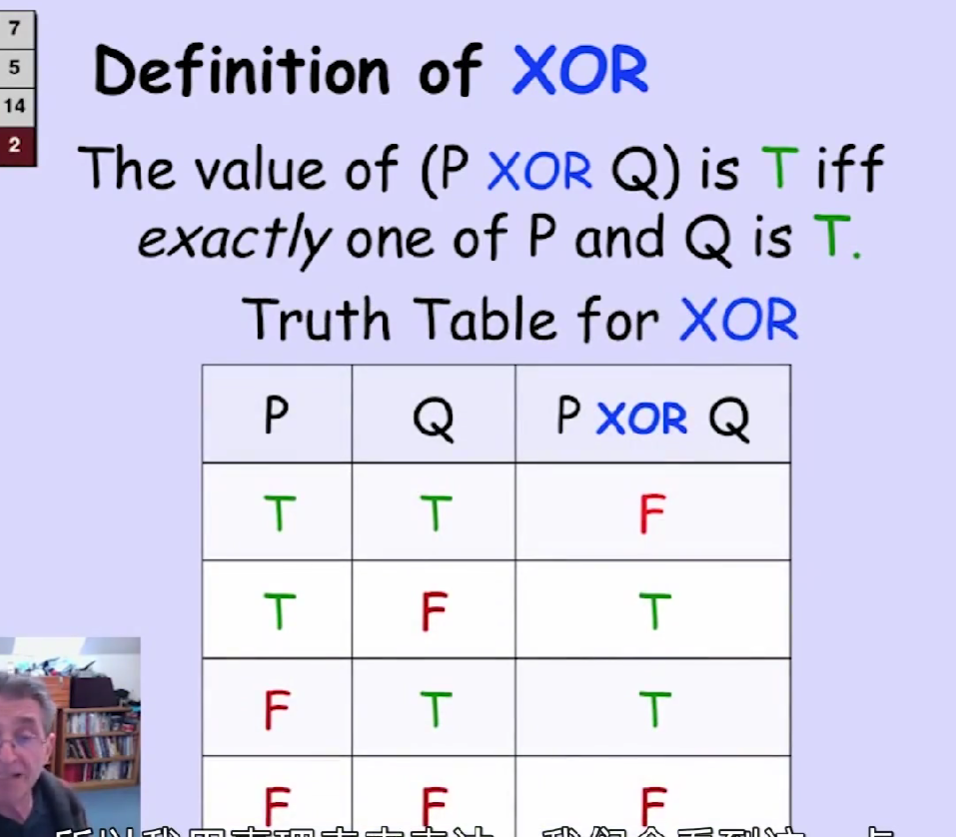

"⊕"读作异或,英文读作”xor",只有当其连接命题(其一定连接着2个及以上的命题)中的每一个命题真假值相同时,大命题才为假(同假异真)

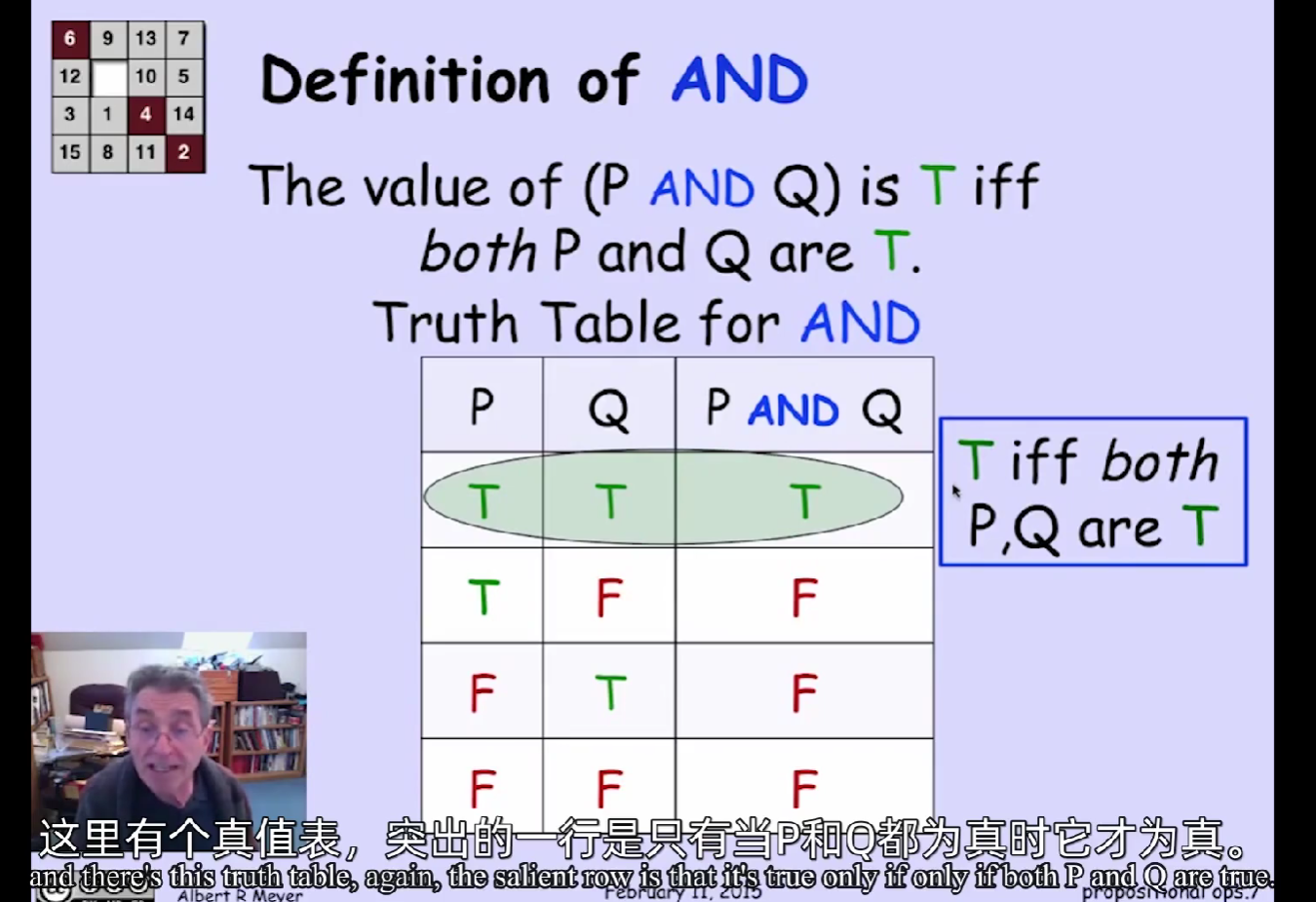

“∧”读作且,英文名“and",当其连接命题(其一定连接着2个及以上的命题)中的每一个命题中任意一个为假,大命题就为假(全真为真,有假为假)

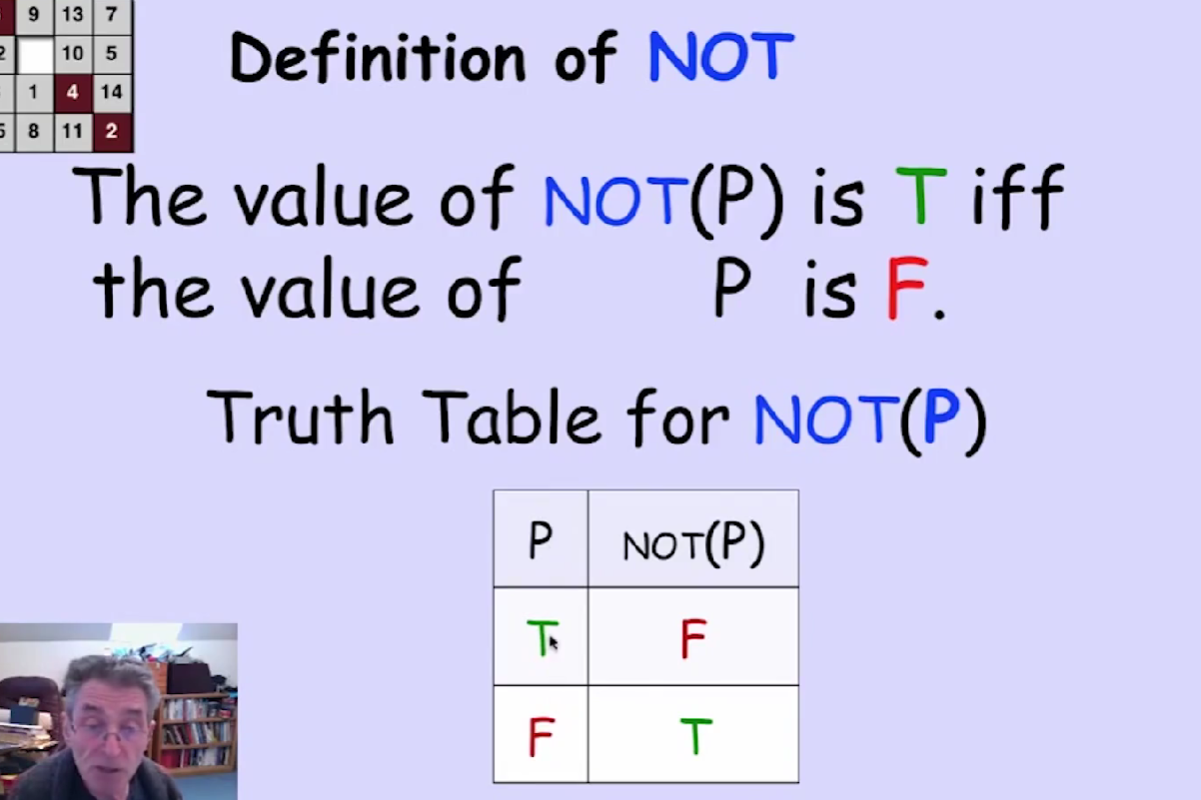

”¬“读作非,否定运算符,英文名”NOT",使原命题真假值颠倒。

命题逻辑的电路逻辑表达

数字逻辑

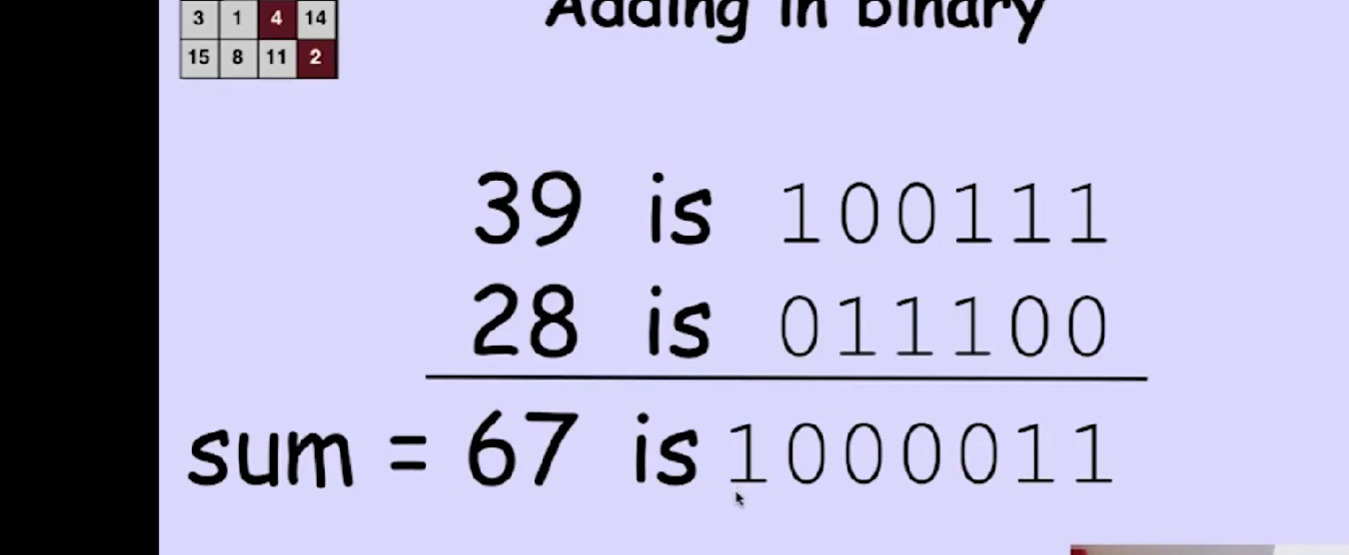

二进制加法

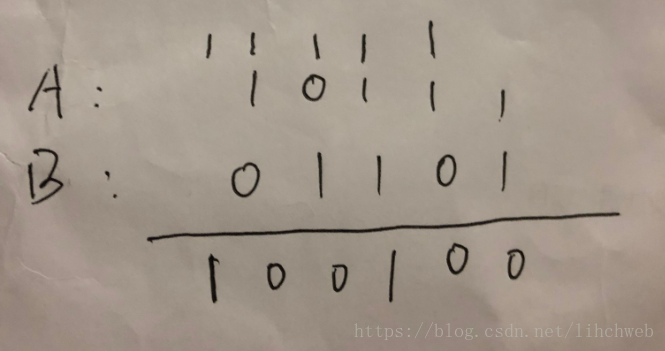

- 计算时,先把两个二进制数对齐(如同十进制一样, 从右向左)

- 1+1为10,此时向上一位进1,0写在本位(如同十进制,因为2进制最高只有1)

- 不全为1的两个数,直接相加得到结果即可。

(此图来自https://blog.csdn.net/lihchweb/article/details/81145154,侵删)

(此图来自https://blog.csdn.net/lihchweb/article/details/81145154,侵删)

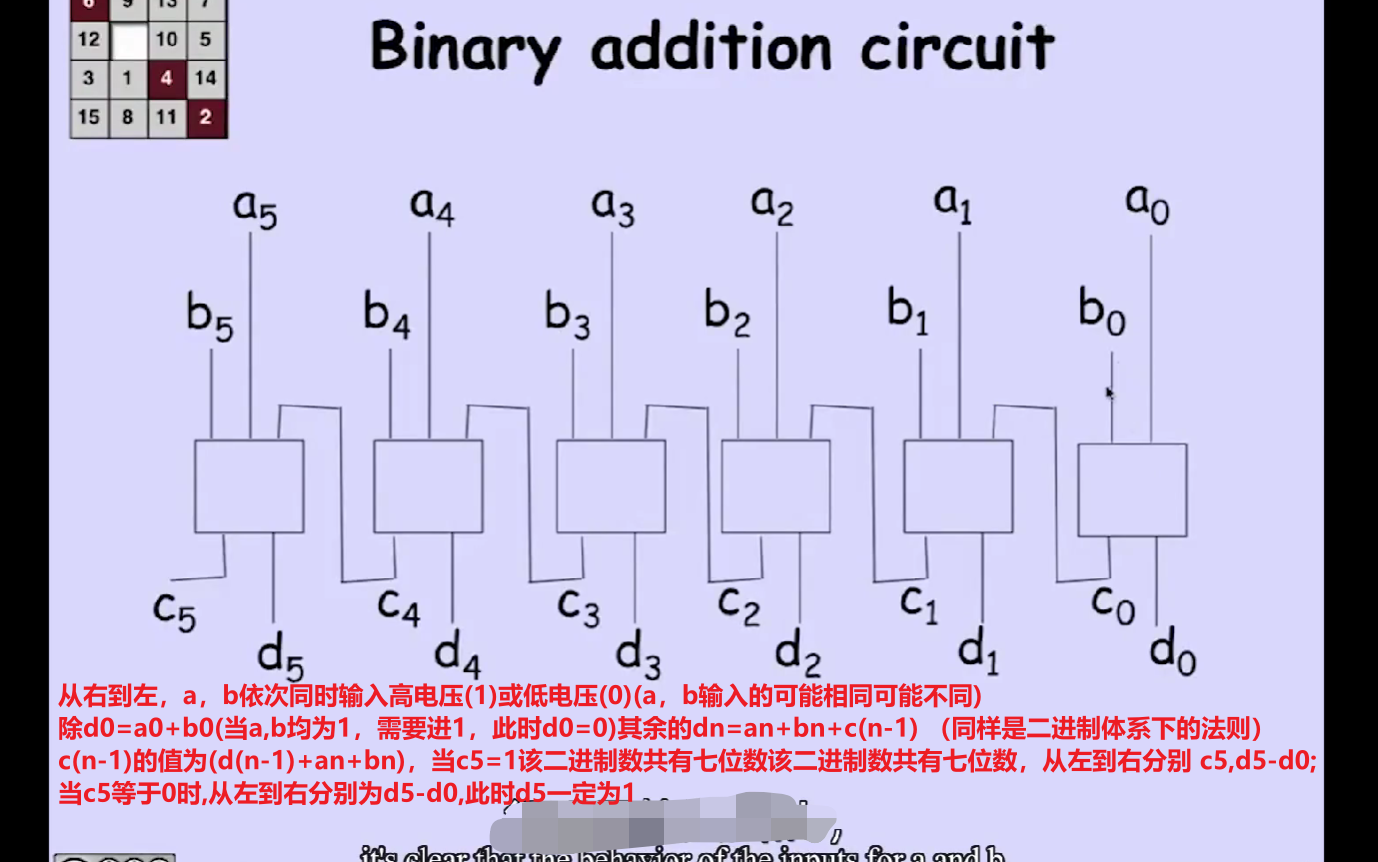

二进制加法电路

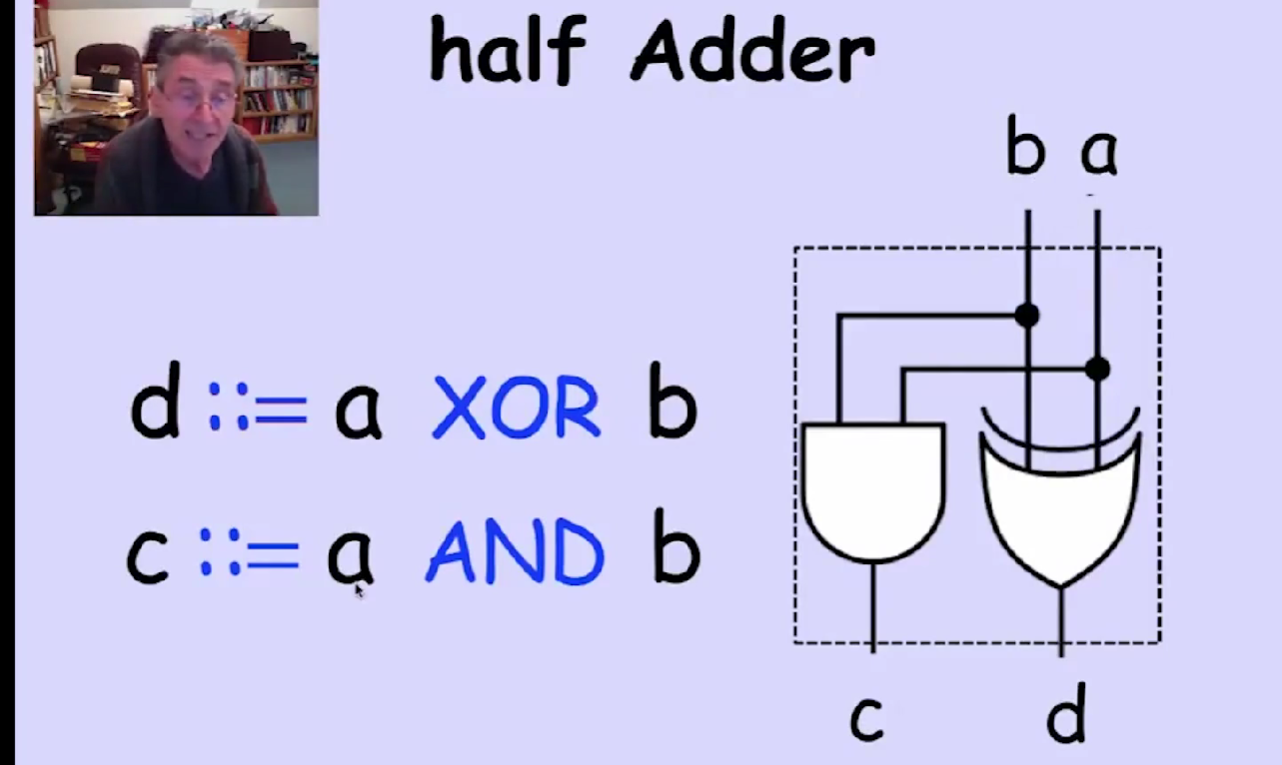

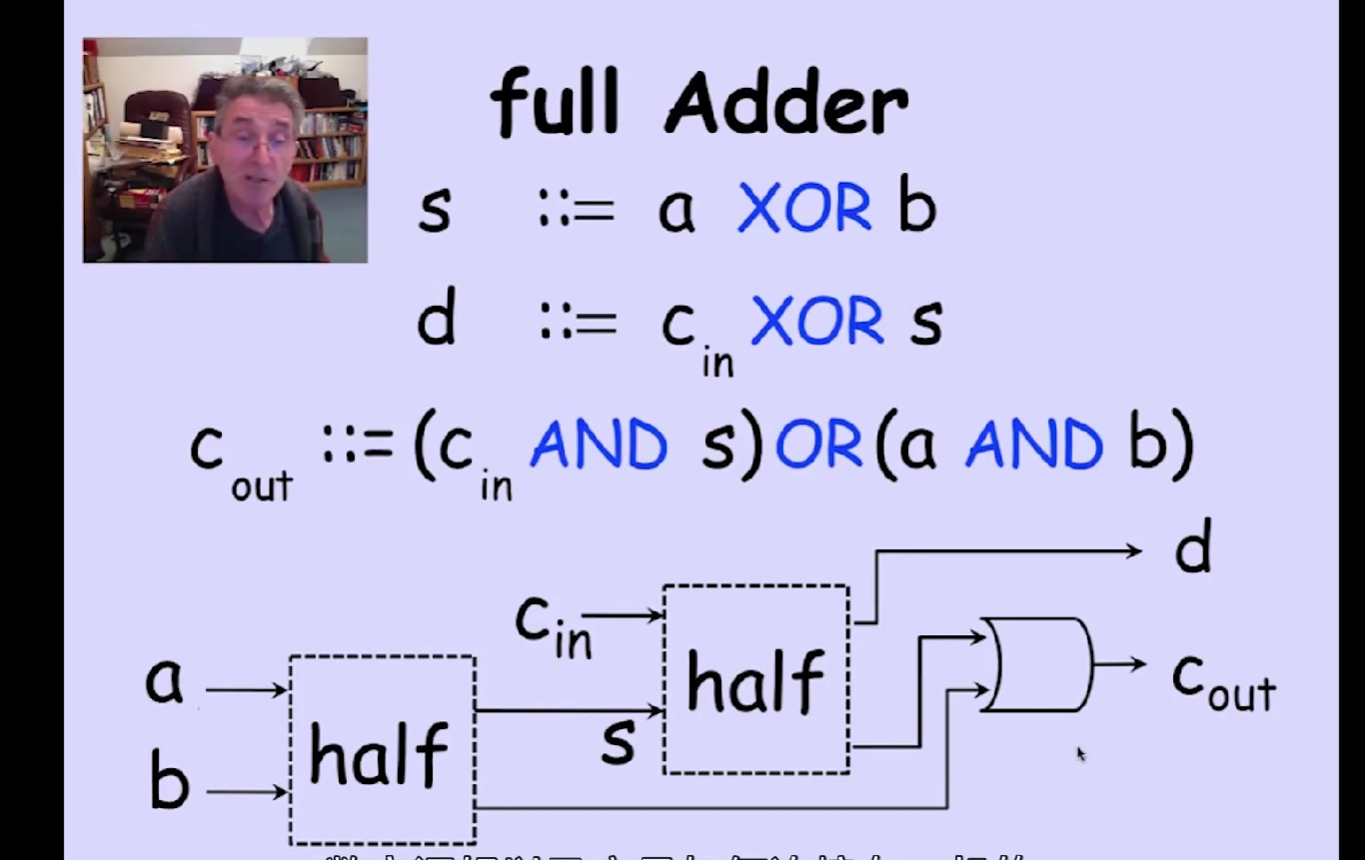

用数学符号表述二进制加法电路

最开始的输入器称之为半加器,因为只有a,b的值加入,"::="的意思是定义为,如d::=a xor b,意思是d被定义为a 异或 b

后面的称之为全加器,由an,bn,c(n-1)相加,

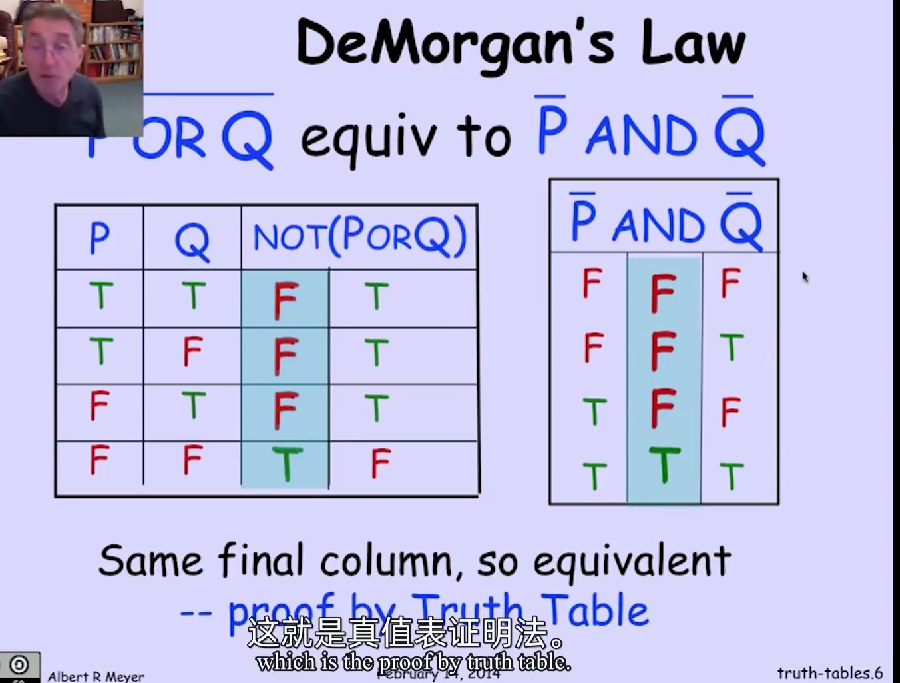

真值表技术

列出所有的真值可能,但正是因为如此,每加一个变量使得需要列出的真值翻倍,最后呈指数级增长,所以需要一个替代方案

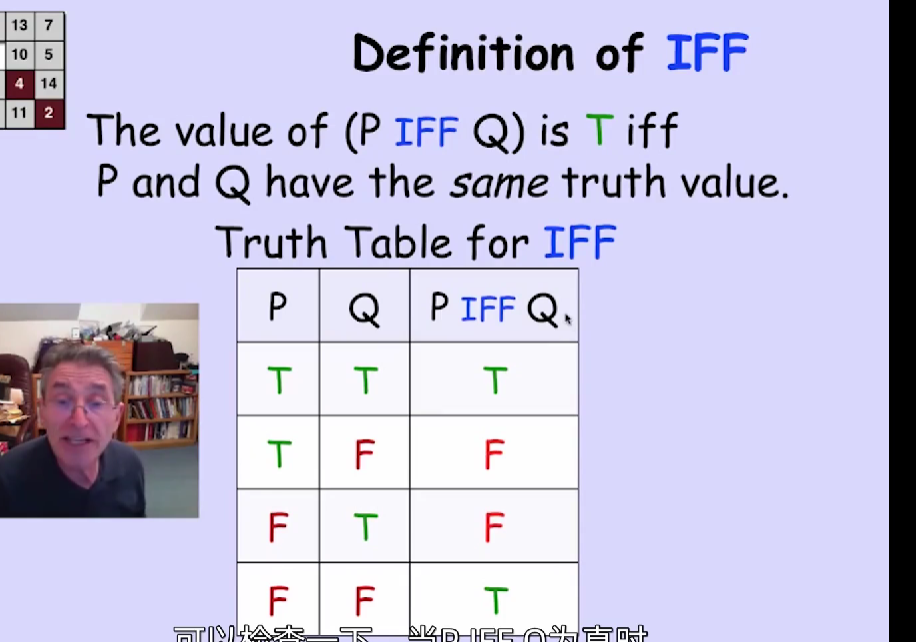

iff词的定义

当且仅当连接词真值相等时,整体为真

浙公网安备 33010602011771号

浙公网安备 33010602011771号