RGB与HSV的转换(FPGA实现)

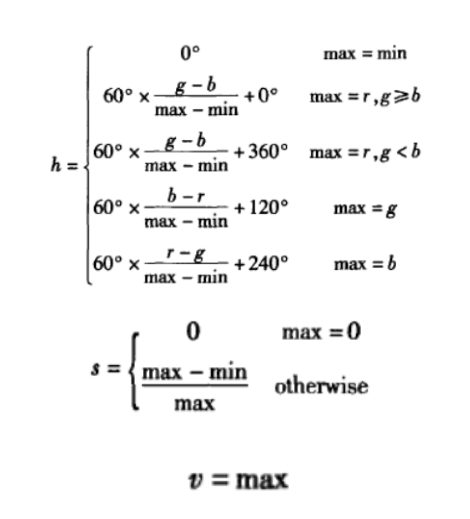

RGB到HSV的转换公式为

由于s的范围是0到1,所以用verilog实现时,将s扩大256倍,容易表示,当然会丢失精度,其次,这里用到许多除法,笔者用的工具可以直接综合除法,所以这里没有例化除法器,当然,例化除法器ip核也是一样的效果。

实现代码如下:

1 module rgb2hsv( 2 input clk, 3 input reset_n, 4 input [7:0]rgb_r, 5 input [7:0]rgb_g, 6 input [7:0]rgb_b, 7 input vs, 8 input hs, 9 input de, 10 output [8:0]hsv_h, 11 output [8:0]hsv_s, 12 output [7:0]hsv_v, 13 output hsv_vs, 14 output hsv_hs, 15 output hsv_de); 16 17 18 reg [7:0]max; 19 reg [7:0]min; 20 reg [13:0]rgb_r_r; 21 reg [13:0]rgb_g_r; 22 reg [13:0]rgb_b_r; 23 24 reg [13:0]rgb_r_r2; 25 reg [13:0]rgb_g_r2; 26 reg [13:0]rgb_b_r2; 27 reg [7:0]max_r; 28 29 wire [7:0]max_min; 30 assign max_min=max-min; 31 reg [7:0]max_min_r; 32 wire [13:0]max60; 33 assign max60=max*60; 34 35 wire [13:0] g_b; 36 wire [13:0] b_r; 37 wire [13:0] r_g; 38 assign g_b=(rgb_g_r>=rgb_b_r)?(rgb_g_r-rgb_b_r):(rgb_b_r-rgb_g_r); 39 assign b_r=(rgb_b_r>=rgb_r_r)?(rgb_b_r-rgb_r_r):(rgb_r_r-rgb_b_r); 40 assign r_g=(rgb_r_r>=rgb_g_r)?(rgb_r_r-rgb_g_r):(rgb_g_r-rgb_r_r); 41 42 43 reg [13:0]temp; 44 reg [13:0]hsv_h_r; 45 reg [15:0]hsv_s_r; 46 reg [7:0]hsv_v_r; 47 48 49 always@(posedge clk or negedge reset_n)begin 50 if(!reset_n)begin 51 rgb_r_r<=0; 52 rgb_g_r<=0; 53 rgb_b_r<=0; 54 end 55 else begin 56 rgb_r_r<=60*rgb_r; 57 rgb_g_r<=60*rgb_g; 58 rgb_b_r<=60*rgb_b; 59 end 60 end 61 62 always@(posedge clk or negedge reset_n)begin 63 if(!reset_n)begin 64 rgb_r_r2<=0; 65 rgb_g_r2<=0; 66 rgb_b_r2<=0; 67 end 68 else begin 69 rgb_r_r2<=rgb_r_r; 70 rgb_g_r2<=rgb_g_r; 71 rgb_b_r2<=rgb_b_r; 72 end 73 end 74 75 always@(posedge clk or negedge reset_n)begin 76 if(!reset_n) 77 max<=0; 78 else if((rgb_r>=rgb_b)&&(rgb_r>=rgb_g)) 79 max<=rgb_r; 80 else if((rgb_g>=rgb_b)&&(rgb_g>=rgb_r)) 81 max<=rgb_g; 82 else if((rgb_b>=rgb_r)&&(rgb_b>=rgb_g)) 83 max<=rgb_b; 84 end 85 86 always@(posedge clk or negedge reset_n)begin 87 if(!reset_n) 88 min<=0; 89 else if((rgb_r<=rgb_b)&&(rgb_r<=rgb_g)) 90 min<=rgb_r; 91 else if((rgb_g<=rgb_b)&&(rgb_g<=rgb_r)) 92 min<=rgb_g; 93 else if((rgb_b<=rgb_r)&&(rgb_b<=rgb_g)) 94 min<=rgb_b; 95 end 96 97 always@(posedge clk or negedge reset_n)begin 98 if(!reset_n) 99 max_min_r<=0; 100 else 101 max_min_r<=max_min; 102 end 103 104 always@(posedge clk or negedge reset_n)begin 105 if(!reset_n) 106 temp<=0; 107 else if(max_min!=0)begin 108 if(rgb_r_r==max60) 109 temp<=g_b/{6'b0,max_min}; 110 else if(rgb_g_r==max60) 111 temp<=b_r/{6'b0,max_min}; 112 else if(rgb_b_r==max60) 113 temp<=r_g/{6'b0,max_min}; 114 end 115 else if(max_min==0) 116 temp<=0; 117 end 118 119 always@(posedge clk or negedge reset_n)begin 120 if(!reset_n) 121 max_r<=0; 122 else 123 max_r<=max; 124 end 125 126 always@(posedge clk or negedge reset_n)begin 127 if(!reset_n) 128 hsv_h_r<=0; 129 else if(max_r==0) 130 hsv_h_r<=0; 131 else if(rgb_r_r2==60*max_r) 132 hsv_h_r<=(rgb_g_r2>=rgb_b_r2)?temp:(14'd360-temp); 133 else if(rgb_g_r2==60*max_r) 134 hsv_h_r<=(rgb_b_r2>=rgb_r_r2)?(temp+120):(14'd120-temp); 135 else if(rgb_b_r2==60*max_r) 136 hsv_h_r<=(rgb_r_r2>=rgb_g_r2)?(temp+240):(14'd240-temp); 137 end 138 139 always@(posedge clk or negedge reset_n)begin 140 if(!reset_n) 141 hsv_s_r<=0; 142 else if(max_r==0) 143 hsv_s_r<=0; 144 else 145 hsv_s_r<={max_min_r,8'b0}/{8'b0,max_r}; 146 end 147 148 149 always@(posedge clk or negedge reset_n)begin 150 if(!reset_n) 151 hsv_v_r<=0; 152 else 153 hsv_v_r<=max_r; 154 end 155 156 reg [2:0]vs_delay; 157 reg [2:0]hs_delay; 158 reg [2:0]de_delay; 159 160 161 always@(posedge clk or negedge reset_n)begin 162 if(!reset_n)begin 163 vs_delay<=0; 164 hs_delay<=0; 165 de_delay<=0; 166 end 167 else begin 168 vs_delay <= { vs_delay[1:0],vs}; 169 hs_delay <= { hs_delay[1:0],hs}; 170 de_delay <= { de_delay[1:0],de}; 171 end 172 end 173 174 assign hsv_vs=vs_delay[2]; 175 assign hsv_hs=hs_delay[2]; 176 assign hsv_de=de_delay[2]; 177 178 assign hsv_h=hsv_h_r[8:0]; 179 assign hsv_s=hsv_s_r[8:0]; 180 assign hsv_v=hsv_v_r; 181 182 endmodule

HSV到RGB的转换公式:

实现代码:

1 module hsv2rgb( 2 input clk, 3 input reset_n, 4 input [8:0]i_hsv_h, 5 input [8:0]i_hsv_s, 6 input [7:0]i_hsv_v, 7 input vs, 8 input hs, 9 input de, 10 output [7:0]rgb_r, 11 output [7:0]rgb_g, 12 output [7:0]rgb_b, 13 output rgb_vs, 14 output rgb_hs, 15 output rgb_de 16 17 ); 18 19 20 reg [7:0]i_hsv_v_r1; 21 reg [7:0]i_hsv_v_r2; 22 reg [7:0]i_hsv_v_r3; 23 reg [7:0]i_hsv_v_r4; 24 reg [8:0]i_hsv_h_r; 25 reg [8:0]i_hsv_s_r1; 26 reg [8:0]i_hsv_s_r2; 27 reg [8:0]i_hsv_s_r3; 28 reg [8:0]i_hsv_s_r4; 29 30 wire [8:0]temp; 31 assign temp=9'd256-i_hsv_s; 32 33 reg [16:0] p;//p=V-V*S,,扩大256 34 reg [7:0] p2; 35 reg [7:0]p3; 36 reg [2:0]I;//H/60的商 37 reg [2:0]I2; 38 reg [2:0]I3; 39 wire [5:0]f;//H/60的余数 40 assign f=i_hsv_h_r-I*60; 41 reg [15:0]f_60; 42 43 reg [15:0]adjust; 44 45 46 47 always@(posedge clk or negedge reset_n)begin 48 if(!reset_n)begin 49 i_hsv_v_r1 <= 0; 50 i_hsv_v_r2 <= 0; 51 i_hsv_v_r3<=0; 52 i_hsv_v_r4<=0; 53 end 54 else begin 55 i_hsv_v_r1<=i_hsv_v; 56 i_hsv_v_r2<=i_hsv_v_r1; 57 i_hsv_v_r3<=i_hsv_v_r2; 58 i_hsv_v_r4<=i_hsv_v_r3; 59 end 60 end 61 62 always@(posedge clk or negedge reset_n)begin 63 if(!reset_n) 64 i_hsv_h_r<=0; 65 else 66 i_hsv_h_r<=i_hsv_h; 67 end 68 69 always@(posedge clk or negedge reset_n)begin 70 if(!reset_n)begin 71 i_hsv_s_r1<=0; 72 i_hsv_s_r2<=0; 73 i_hsv_s_r3<=0; 74 i_hsv_s_r4<=0; 75 end 76 else begin 77 i_hsv_s_r1<=i_hsv_s; 78 i_hsv_s_r2<=i_hsv_s_r1; 79 i_hsv_s_r3<=i_hsv_s_r2; 80 i_hsv_s_r4<=i_hsv_s_r3; 81 end 82 end 83 84 always@(posedge clk or negedge reset_n)begin 85 if(!reset_n)begin 86 p<=0; 87 p2<=0; 88 p3<=0; 89 end 90 else begin 91 p<=temp*i_hsv_v; 92 p2<=p[15:8]; 93 p3<=p2; 94 end 95 end 96 97 always@(posedge clk or negedge reset_n)begin 98 if(!reset_n) 99 I<=0; 100 else if(i_hsv_h<60) 101 I<=0; 102 else if((i_hsv_h<120)&&(i_hsv_h>=60)) 103 I<=1; 104 else if((i_hsv_h<180)&&(i_hsv_h>=120)) 105 I<=2; 106 else if((i_hsv_h<240)&&(i_hsv_h>=180)) 107 I<=3; 108 else if((i_hsv_h<300)&&(i_hsv_h>=240)) 109 I<=4; 110 else 111 I<=5; 112 end 113 114 always@(posedge clk or negedge reset_n)begin 115 if(!reset_n)begin 116 I2<=0; 117 I3<=0; 118 end 119 else begin 120 I2<=I; 121 I3<=I2; 122 end 123 end 124 125 126 always@(posedge clk or negedge reset_n)begin 127 if(!reset_n) 128 f_60<=0; 129 else 130 f_60<={f,8'b0}/60; 131 end 132 133 always@(posedge clk or negedge reset_n)begin 134 if(!reset_n) 135 adjust<=0; 136 else 137 adjust<=(i_hsv_v_r2-p2)*f_60[7:0]; 138 end 139 140 141 /**************************************/ 142 reg [7:0]rgb_r_r; 143 reg [7:0]rgb_g_r; 144 reg [7:0]rgb_b_r; 145 146 reg [3:0]vs_delay; 147 reg [3:0]hs_delay; 148 reg [3:0]de_delay; 149 150 always@(posedge clk or negedge reset_n)begin 151 if(!reset_n)begin 152 rgb_r_r<=0; 153 rgb_g_r<=0; 154 rgb_b_r<=0; 155 end 156 else case(I3) 157 0: begin 158 rgb_r_r<=i_hsv_v_r3; 159 rgb_g_r<=p3+adjust[15:8]; 160 rgb_b_r<=p3; 161 end 162 163 1: begin 164 rgb_r_r<=i_hsv_v_r3-adjust[15:8]; 165 rgb_g_r<=i_hsv_v_r3; 166 rgb_b_r<=p3; 167 end 168 169 2: begin 170 rgb_r_r<=p3; 171 rgb_g_r<=i_hsv_v_r3; 172 rgb_b_r<=p3+adjust[15:8]; 173 end 174 175 3: begin 176 rgb_r_r<=p3; 177 rgb_g_r<=i_hsv_v_r3-adjust[15:8]; 178 rgb_b_r<=i_hsv_v_r3; 179 end 180 181 4: begin 182 rgb_r_r<=p3+adjust[15:8]; 183 rgb_g_r<=p3; 184 rgb_b_r<=i_hsv_v_r3; 185 end 186 187 5: begin 188 rgb_r_r<=i_hsv_v_r3; 189 rgb_g_r<=p3; 190 rgb_b_r<=i_hsv_v_r3-adjust[15:8]; 191 end 192 193 default: begin 194 rgb_r_r<=0; 195 rgb_g_r<=0; 196 rgb_b_r<=0; 197 end 198 endcase 199 end 200 201 always@(posedge clk or negedge reset_n)begin 202 if(!reset_n)begin 203 vs_delay<=0; 204 hs_delay<=0; 205 de_delay<=0; 206 end 207 else begin 208 vs_delay<={vs_delay[2:0],vs}; 209 hs_delay<={hs_delay[2:0],hs}; 210 de_delay<={de_delay[2:0],de}; 211 end 212 end 213 214 assign rgb_r = (i_hsv_s_r4==0)?i_hsv_v_r4:rgb_r_r; 215 assign rgb_g = (i_hsv_s_r4==0)?i_hsv_v_r4:rgb_g_r; 216 assign rgb_b = (i_hsv_s_r4==0)?i_hsv_v_r4:rgb_b_r; 217 218 assign rgb_vs = vs_delay[3]; 219 assign rgb_hs = hs_delay[3]; 220 assign rgb_de = de_delay[3]; 221 222 endmodule

参考文献:

[1]袁奋杰, 周晓, 丁军,等. 基于FPGA的RGB和HSV色空间转换算法实现[J]. 电子器件, 2010, 33(4):5.

浙公网安备 33010602011771号

浙公网安备 33010602011771号