OrCAD Capture CIS 原理图设计(自学)

初次配置文件:

先创建元件库:

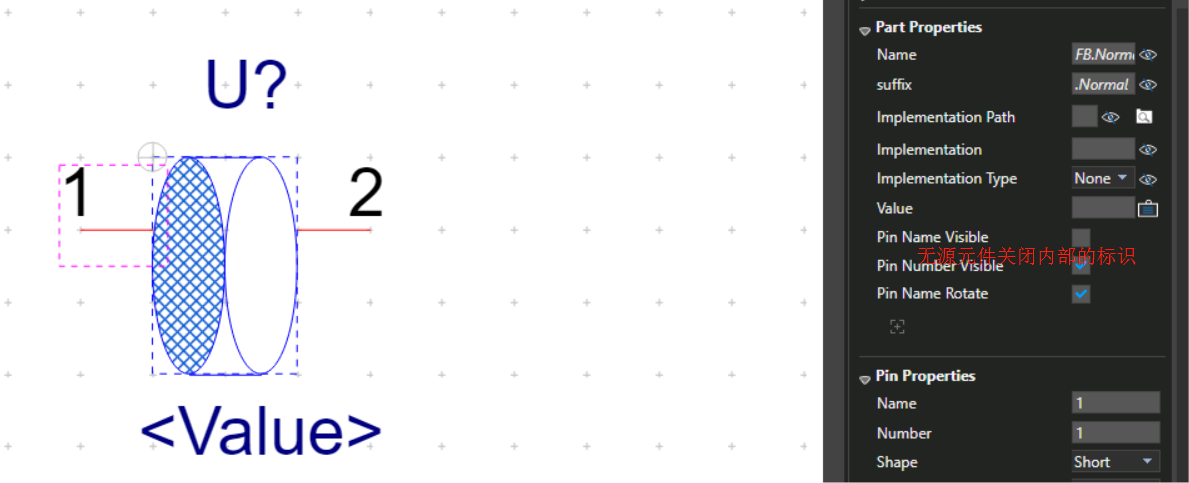

放置管脚:

cy2303芯片手册:

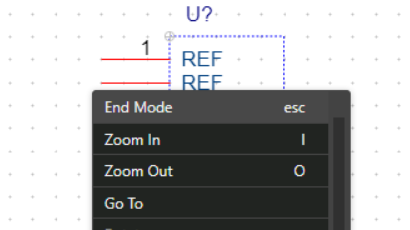

取消放置:

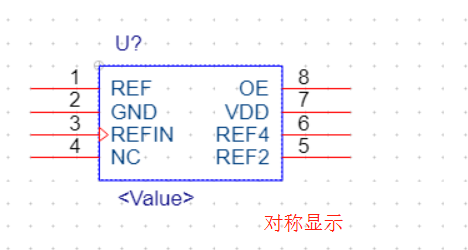

不规则绘制:

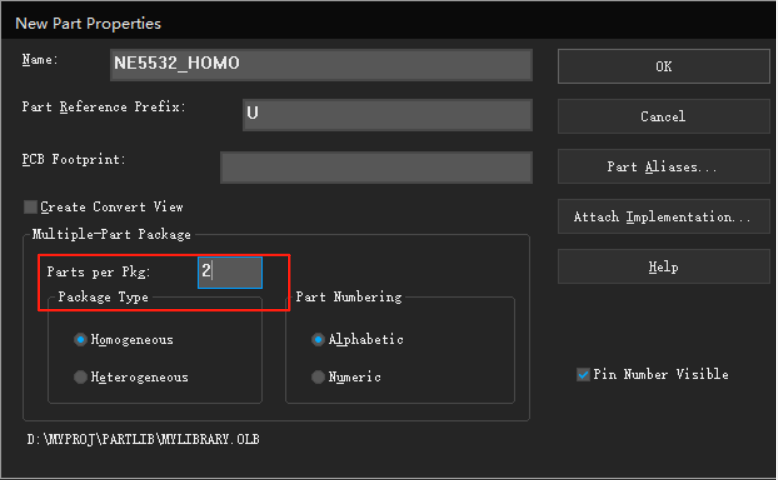

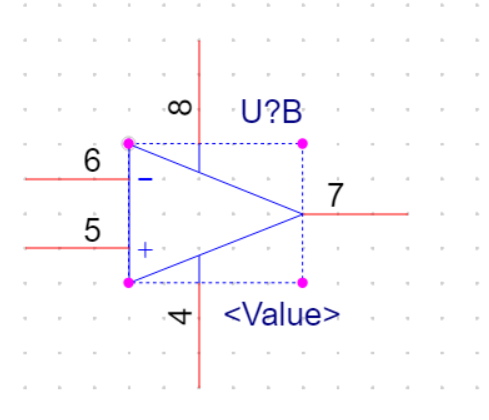

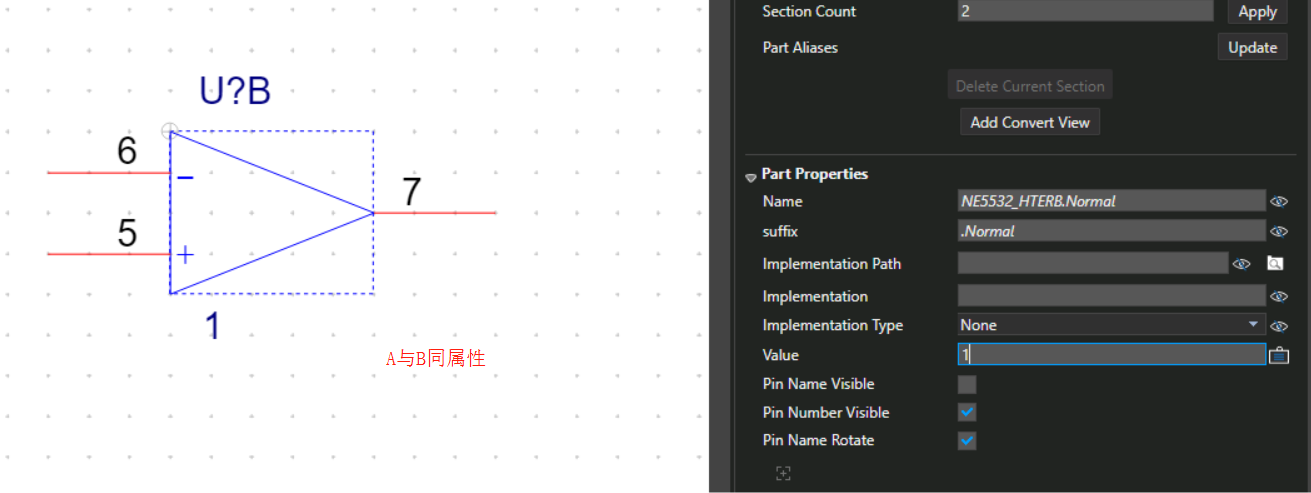

NE5532双运放:

避免找不到相同的器件:

方式结束后修改,同一组。

R旋转,W画线

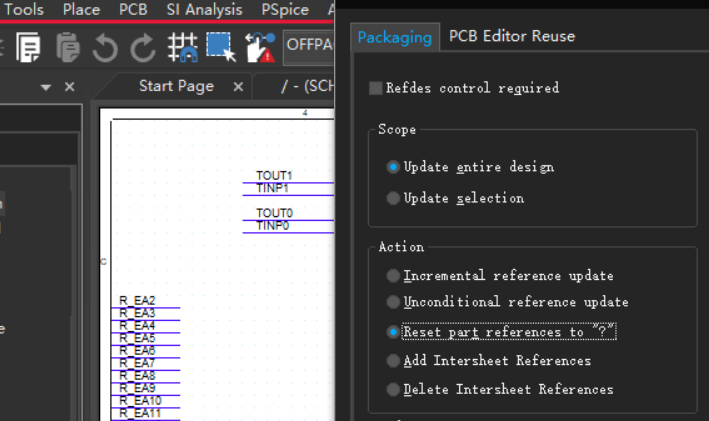

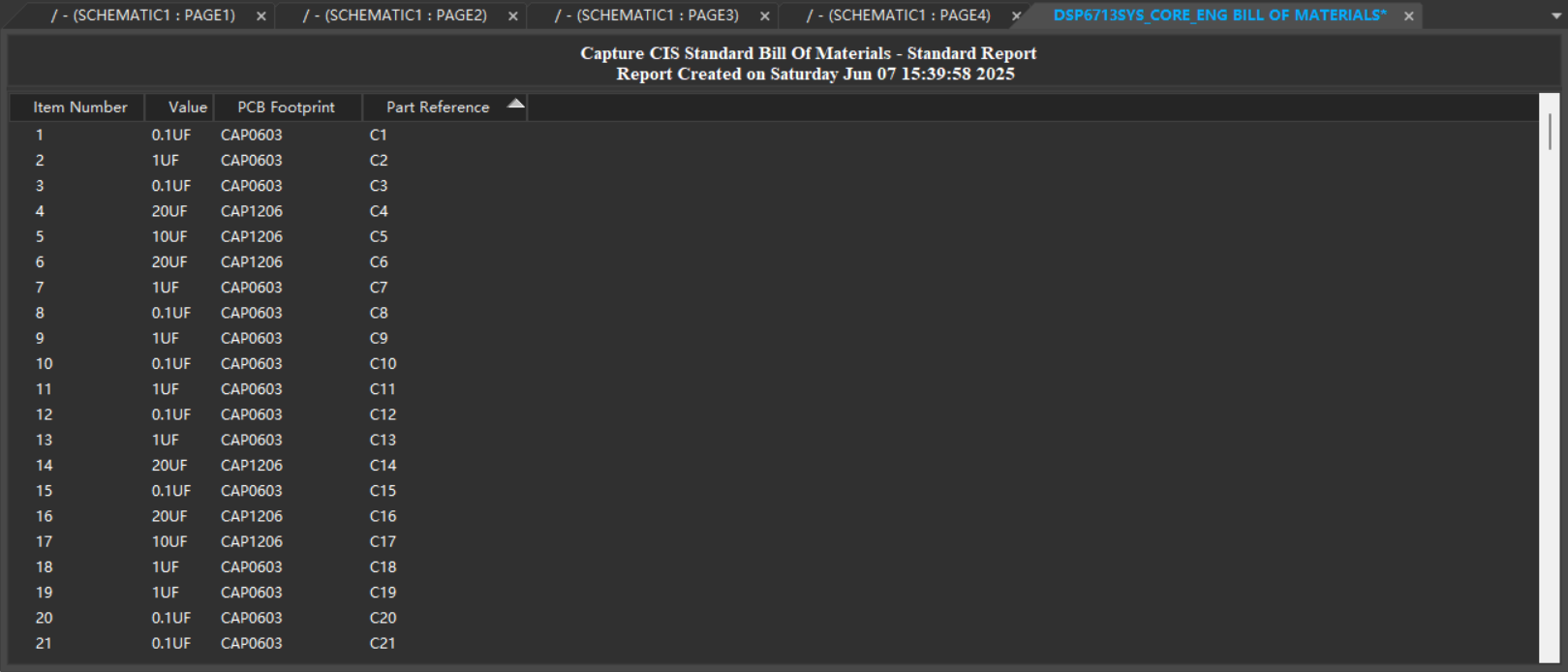

元器件重新编号

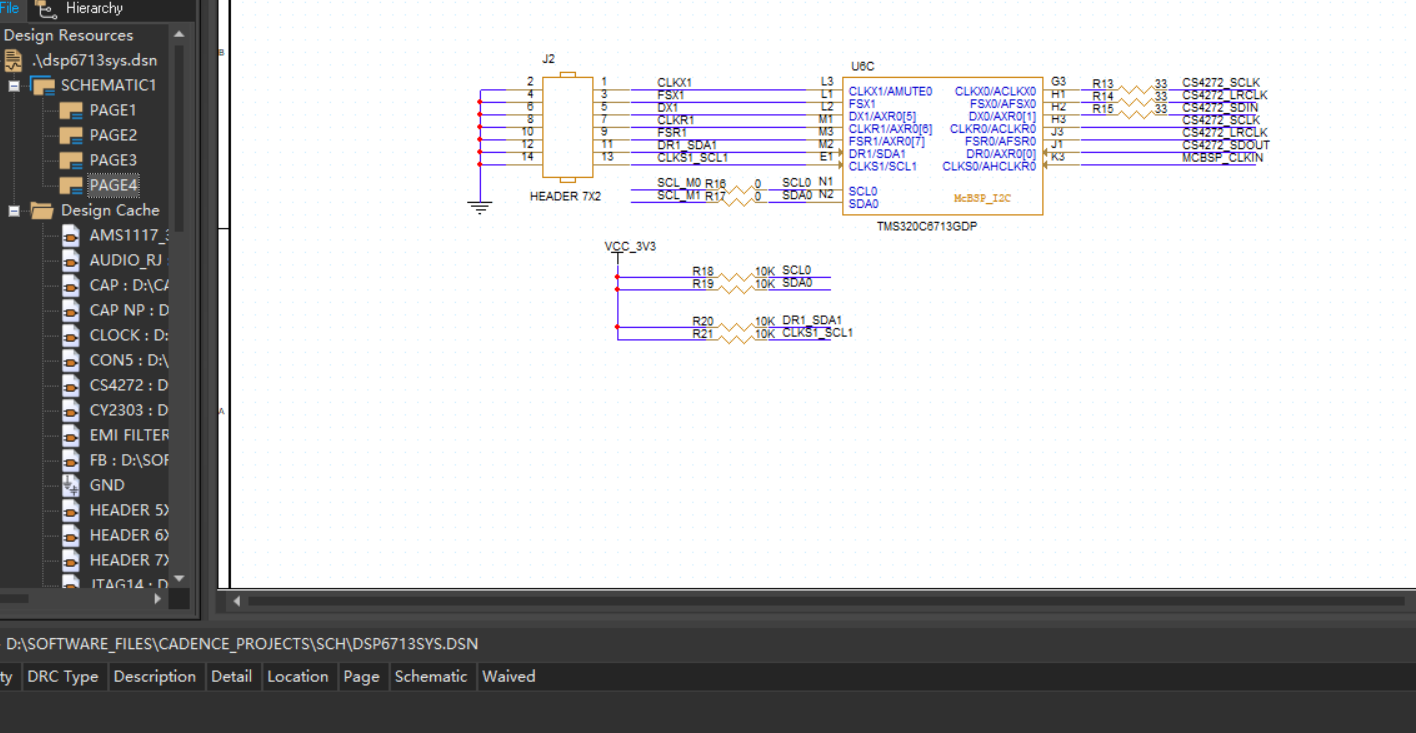

总线:命名样式ED[0:31],F4/ctrl拖动

Edit-->Browse-->Parts(检查元件标号和值)/Nets(检查网络电气特性)

需要修改某一个原件直接双击

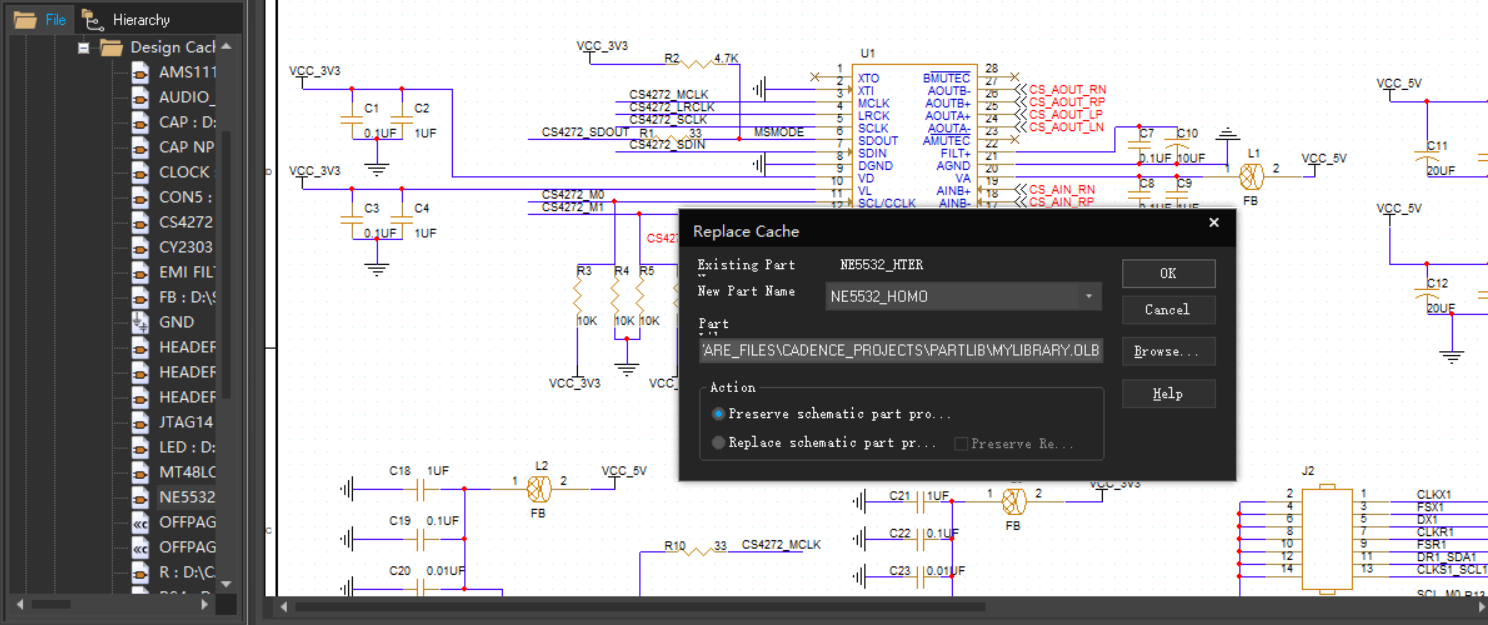

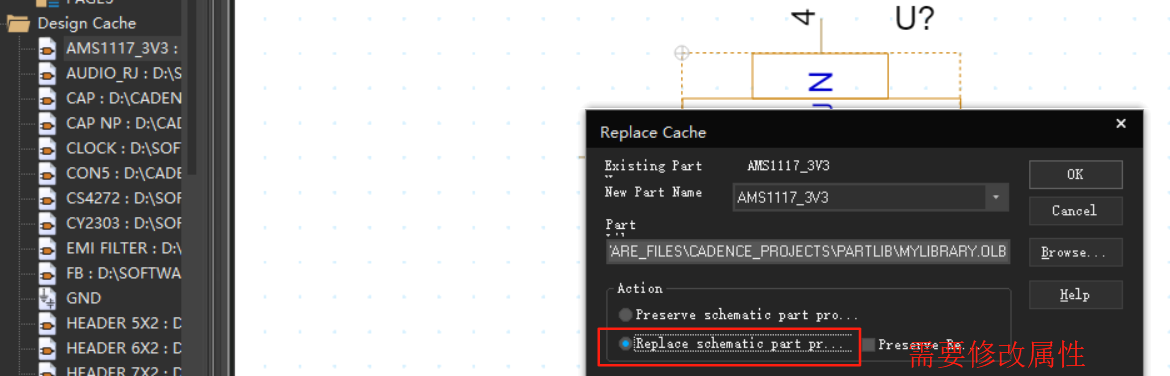

元件更新与替换:

alt拖动元器件会断开连接

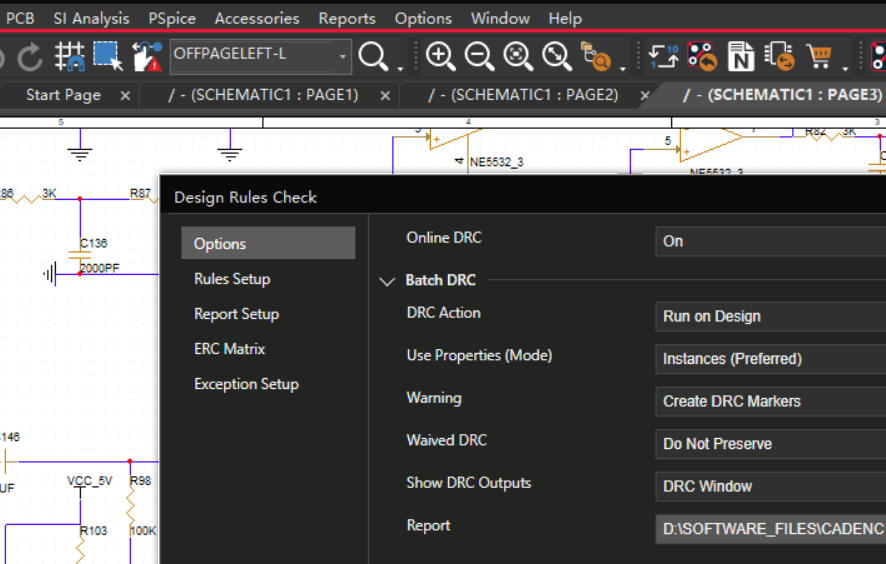

生成网表之前需要检测上述的一些检查,然后重置网络编号,整体DRC检查。

ERROR: Possible pin type conflict VCC_3V3 ,将管教电源的属性改成passive ,问题解决。

(如果一个引脚既可以输出也可以输入或者不清楚实际的功能,可以把引脚设置为passive,仿真会忽略对管脚的检查)

直到检查无错误,无警告:

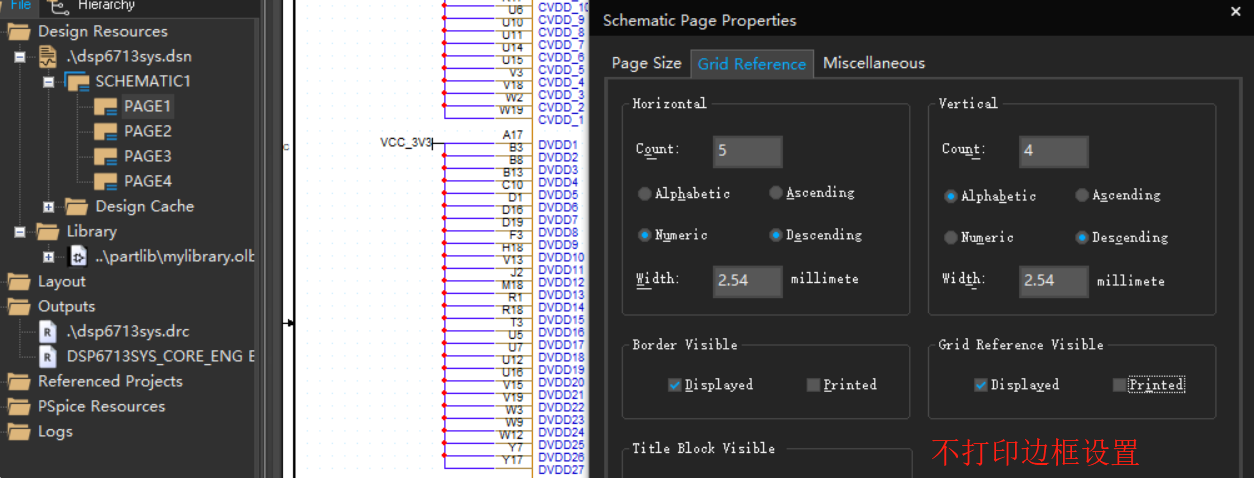

生成打印文件:

打印设置:

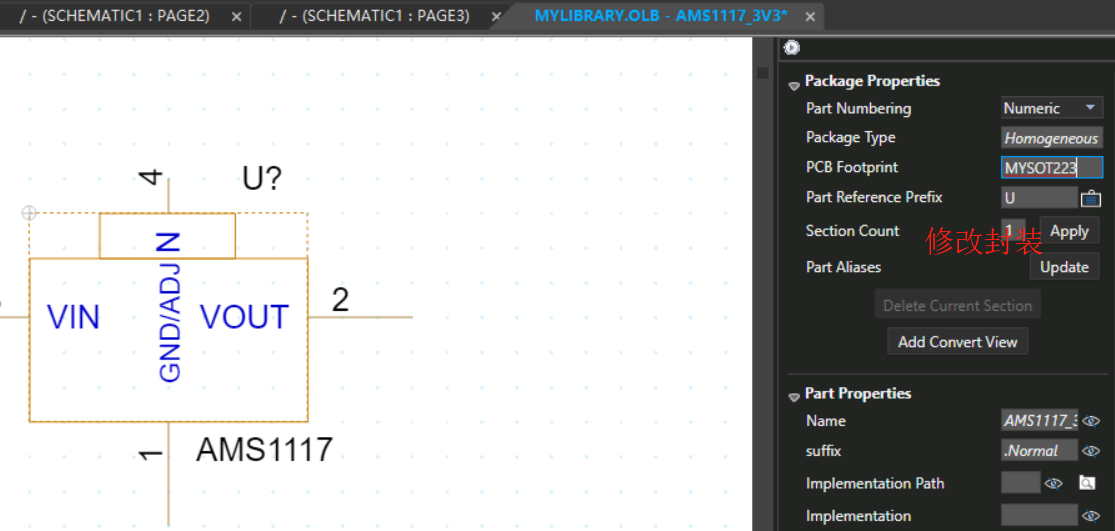

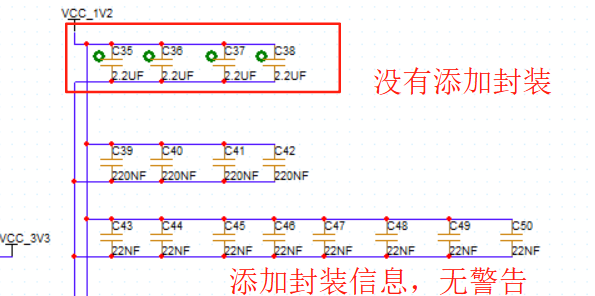

footprint:

找到: [Allegro Footprints]

加入自定义封装路径:Dir1=Dir1=D:\software files\Cadence Projects\mypcblib

可以设置多个Dir2= ...

Dir3=...

将文件中的PSM、PAD和DRA文件复制到添加的文件夹下,以及FSM文件

浙公网安备 33010602011771号

浙公网安备 33010602011771号