数字电路模拟程序两次题目集+课堂测验总结

前言

本次的两次题目集均围绕数字电路模拟程序程序进行展开:第一次电路中包含与门、或门、非门、异或门、同或门五种元件,输入元件信息、引脚信息、输入信号以及连接信息,要求按照与门、或门、非门、异或门、同或门的顺序依次输出所有元件的输出引脚电平;第二次在第一次的基础上添加了三态门、译码器、数据选择器以及数据分配器,此外,要求按照与门、或门、非门、异或门、同或门、三态门、译码器、数据选择器、数据分配器的顺序依次输出所有元件的输出引脚电平。第一次题目需要理解数字电路的模拟逻辑并掌握继承等知识点,第二次作业则要求程序能够进一步处理更复杂的情况,难度是逐层递增的。题量方面来说,因为第二次只是在第一次的基础上添加了一些门类和对应的处理逻辑,所以笔者觉得第二次会比第一次小一些。

设计与分析

第一次作业

因为之前学习过一些数字电路的相关知识,所以本次的大作业对于笔者来说会比上一次的更好理解,看完题目之后笔者就直接设计了几个门类和大体框架,然后再慢慢根据输入补充处理逻辑,最后根据输出结果对比继续修改直到通过所有测试点。

代码规模

- 整体规模、结构

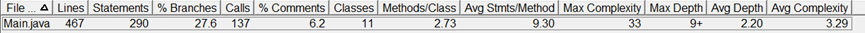

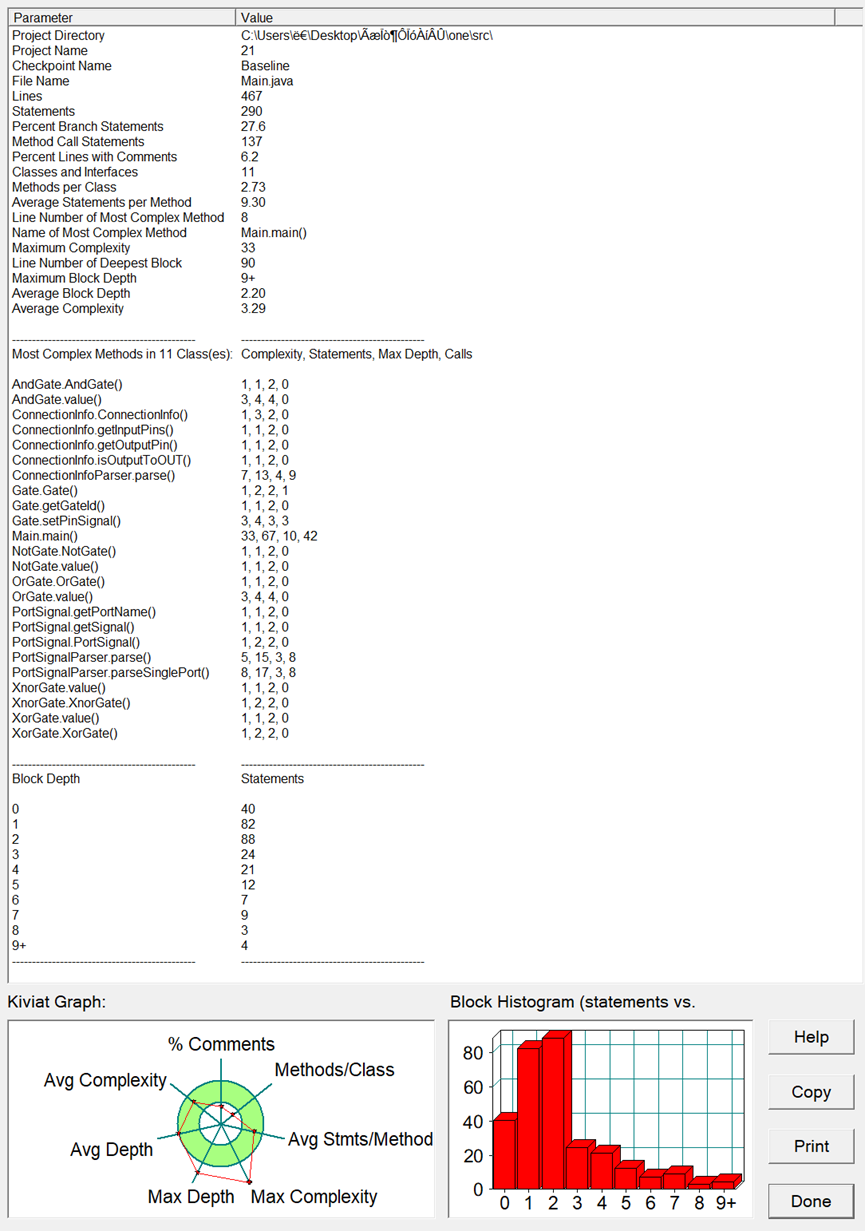

(1)文件与类结构:核心逻辑集中于Main.java文件,共涉及11个类,平均每个类有2.73个方法,属于单文件多类的工具类项目,类数量适中但方法分布较分散,部分类职责相对集中。

(2)代码行数与语句:总代码行467行,可执行语句290条,方法调用语句276次,整体属于中小型模块级别,代码量比轻量型项目更饱满。 - 复杂度与可维护性

(1)圈复杂度:最大圈复杂度为33,属于极高复杂度模块;平均复杂度3.29,核心方法逻辑密集,维护难度大,需重点拆分优化。

(2)代码块深度:最大块深度9,平均块深度2.20,块深度“9+”的语句占比约1.4%,但核心方法嵌套层级偏深。

(3)注释比例:注释占比仅6.2%,对关键逻辑缺乏说明,可读性较弱。 - 方法级复杂度分布

(1)复杂度最高的方法是Main.main(),复杂度33、有效语句数67条、最大块深度9、方法调用42次,是整个项目的复杂度核心,逻辑高度集中、分支嵌套密集。

(2)其他方法复杂度普遍较低,仅ConnectionInfoParser.parse()复杂度为7,多数方法仅承担基础的属性操作、简单逻辑功能。 - 代码块深度的直方图分布

(1)块深度为1的语句40条,深度2的82条,深度3的88条,深度4的24条,深度“9+”的4条;过度嵌套(深度≥4)的语句占比约9.7%,且全部集中在Main.main()方法中,其他方法无深层嵌套问题。 - 雷达图的多维度对比

(1)% Comments的“雷达半径”显著偏小,与Avg Complexity、Max Complexity、Max Depth形成强烈反差,暴露“注释严重不足、核心方法复杂度/嵌套过高”的突出问题。

(2)Methods/Class、Avg Stmts/Method、Avg Depth等维度的“雷达半径”相对均衡,类与方法的结构规模处于合理区间,无过度冗余问题。

第二次作业

根据题目要求,在第一次作业代码的基础上进行类的添加和逻辑调整

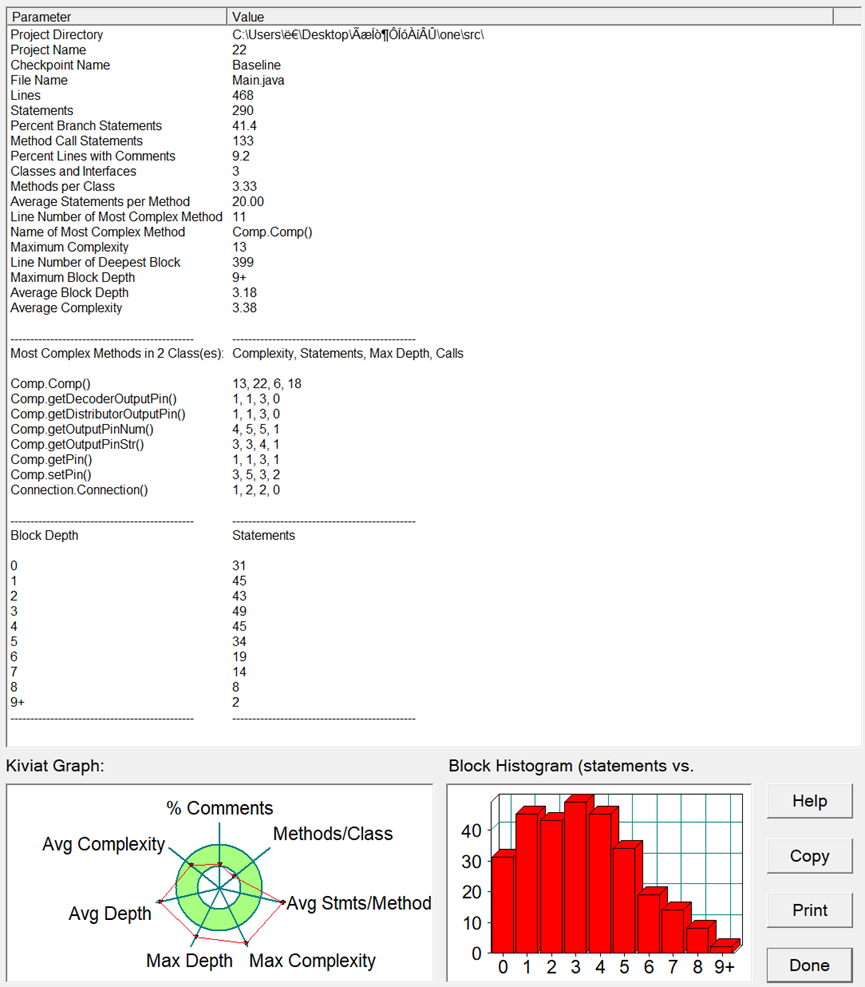

代码规模

- 整体规模、结构

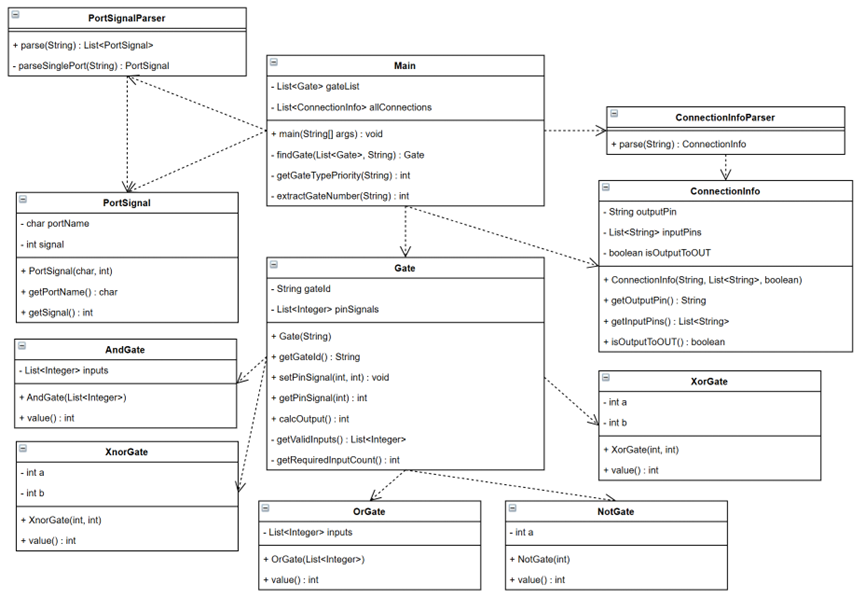

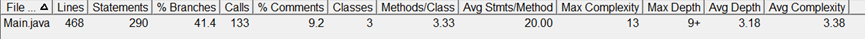

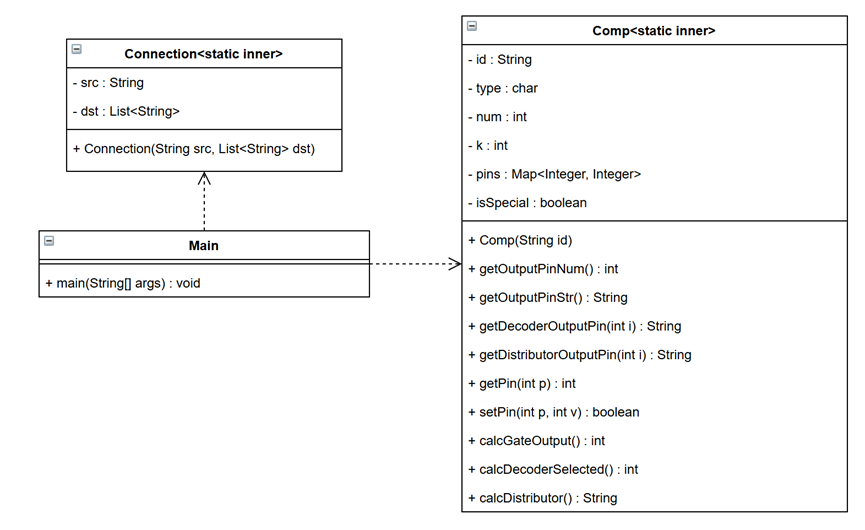

(1)文件与类结构:核心逻辑集中于Main.java文件,包含3个类,平均每个类有3.33个方法,属于单文件、类数量少但方法相对集中的小型项目,Comp类承担了主要功能逻辑。

(2)代码行数与语句:总代码行468行,可执行语句290条,方法调用语句214次,属于轻量到中型之间的模块级别,代码量较饱满但类结构简洁。 - 复杂度与可维护性

(1)圈复杂度:最大圈复杂度13,属于中高复杂度模块;平均复杂度3.38,核心类Comp的构造方法逻辑密集,维护成本较高。

(2)代码块深度:最大块深度9,平均块深度3.18,块深度“9+”的语句占比约0.7%,嵌套层级整体偏深。

(3)注释比例:注释占比9.2%,虽略高于常规轻量项目,但对Comp类的核心逻辑缺乏详细说明,可读性一般。 - 方法级复杂度分布

(1)复杂度最高的方法是Comp.Comp(),复杂度13、有效语句22条、最大块深度6、方法调用18次,是项目的复杂度核心,逻辑集中且包含较多分支。

(2)其他方法复杂度普遍较低,如Connection.Connection()复杂度仅2,仅承担基础属性初始化功能。 - 代码块深度的直方图分布

(1)块深度为1的语句31条,深度2的45条,深度3的43条,深度4的43条,深度“9+”的2条;深度≥4的语句占比约31%,嵌套分布较分散,整体嵌套问题比前一个项目更广泛。 - 雷达图的多维度对比

(1)% Comments的“雷达半径”仍偏小,与Max Complexity、Max Depth存在差距,注释覆盖不足仍是短板。

(2)Methods/Class、Avg Stmts/Method等维度的“雷达半径”较均衡,类与方法的结构规模合理,无过度冗余或缺失问题。

课堂测验

本次测验总分232分,共分为四大题型,笔者判断题、单选题、多选题、填空题的得分率分别为89.3%、92.5%、75.7%、86.4%。

详细分析

- 判断题

答题表现:答错 6 题,对基础知识点掌握扎实,答题准确率较高,但部分易混淆的知识点存在漏洞,对部分细节概念的理解不够精准。 - 单选题

答题表现:答错 3 题,正确率最高,对单个知识点的辨识能力较强,但还需针对这 3 道题对应的知识点进行复盘,排查知识盲区。 - 多选题

答题表现:答错 9题,对部分需要综合判断的知识点能够准确选择,但整体稳定性不足,对知识点的掌握不够全面、对知识点之间的关联理解不够透彻,存在漏选或错选的情况。 - 填空题

答题表现:答错4题,对需要准确记忆的知识点掌握较好,大部分填空题能够精准作答,但特定知识点的记忆不够牢固,存在模糊记忆的情况。

采坑心得

第一次作业

本次大作业修改完所有编译错误之后还有一个测试点没有通过,询问同学得知这个测试点主要考察复杂情况的处理。笔者把代码交给ai进行详细分析,发现主要问题在于信号传播逻辑不完整:当前代码只处理了直接连接,但没有处理多级连接的信号传播。修改完这个点之后就可以通过所有测试点了。

第二次作业

本次大作业初次提交之后只得了25分,存在引脚编号规则、信号传播逻辑和元件计算逻辑不完善的问题,修改完之后通过了部分测试点得到32分。之后笔者再怎么修改都一直卡在这个分数,只能回去重新分析这段代码,感觉写的太复杂了,于是笔者优化了数据结构,使用 signalConnections 存储信号连接关系,信号传播也改为迭代方式,再次提交获得41分。参考第一次大作业没过的经历,笔者感觉问题可能出现在信号传播逻辑上,所以进一步去简化信号传播逻辑,使用do-while循环直到信号稳定,再重新确定译码器和数据分配器的多路输出,这次只有一个测试点没过了。然而笔者又一次卡住了,不管怎么修改都通过不了这个测试点,询问ai详细分析也找不到问题所在,最后笔者尝试对比之前提交的各个版本,推测出该测试点可能涉及译码器和数据分配器的输入引脚信号传播顺序。然后仔细分析代码,发现笔者代码中存在译码器和数据分配器的输入引脚信号没有正确传播到其输出连接的元件的问题。于是笔者增加了元件引脚信号到其他元件输入的传播逻辑、优化了连接查找、改进了信号传播顺序、修复了引脚值比较、改进了特殊元件处理,终于通过了所有测试点。

改进建议

1.拆分主函数,将其逻辑按功能模块拆解为多个低复杂度子方法,降低圈复杂度和块深度。

2.针对类、关键方法、复杂逻辑分支添加注释,将注释占比提升至10%以上,增强代码可读性。

3.梳理Max Depth≥5的代码块,简化过度嵌套的if-else或循环,使代码结构更扁平。

4.在写代码之前就提前设计好类图,梳理各个类之间的关系,不要直接上手想到哪里写哪里,这样后续的修改会更简单。

5.建立错题本,整理课堂测验错题,将错题对应的知识点进行归纳,分析漏选 / 错选的原因。

6.明确每个选项对应的知识点,加强知识点之间的关联性学习,避免孤立记忆,提升对综合类知识点的判断能力。

7.关注易混淆的细节概念,通过对比学习的方式区分相似知识点,定期复盘,强化记忆。

总结

本次大作业围绕两次数字电路模拟程序题目集及课堂测验展开,两次题目集聚焦数字电路模拟逻辑,第一次涉及五种基础门电路,核心是通过继承设计类结构实现输出计算;第二次新增四种复杂元件,虽题量因复用基础逻辑略减,但需处理更复杂的信号传播与元件交互。课堂测验整体良好,单选、判断准确率较高,但多选暴露知识点关联理解不足的短板,需强化综合应用能力。

此外,希望老师在编写测试点时可以提供一些参考文字,给出每个测试点具体在检测哪种情况,这样我们也可以比较有针对性地修改代码,不至于过于盲目找不出问题所在。

浙公网安备 33010602011771号

浙公网安备 33010602011771号